邏輯鎖定功能可以將FPGA中的代碼模塊在固定區域實現,優化時序性能,提升設計可靠性。 增量編譯功能,可以使設計更快速時序收斂,加快編譯速度。

LogicLock

使用Chip Planner創建邏輯鎖定區域

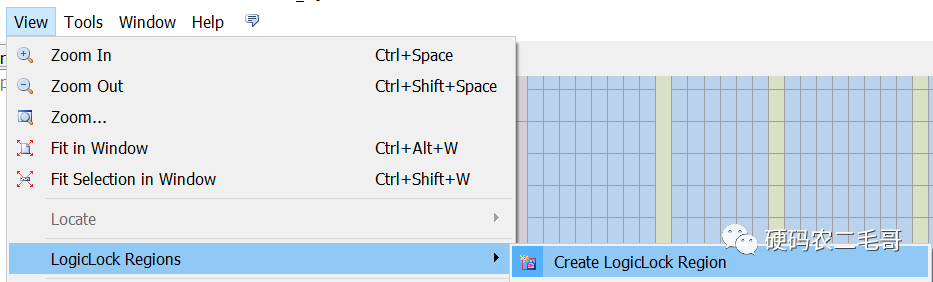

打開Chip Planner,點擊查看 -> 邏輯鎖區域 -> 創建邏輯鎖區域

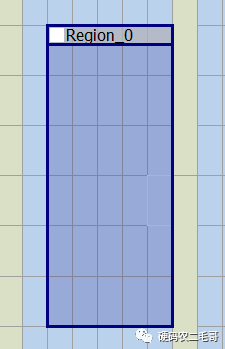

在Chip Planner中選擇一塊區域

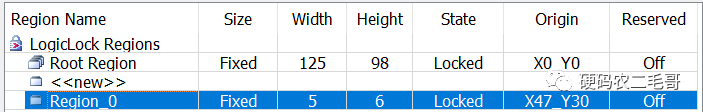

該區域信息如下圖所示

為選擇的區域設置實現模塊

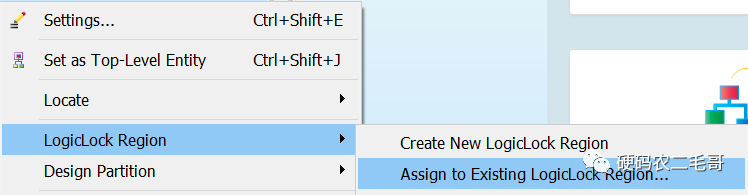

在設計模塊中選中實則文件,右鍵選擇LogicLock Region->Assign to Existing LogicLock Region,完成邏輯鎖定。

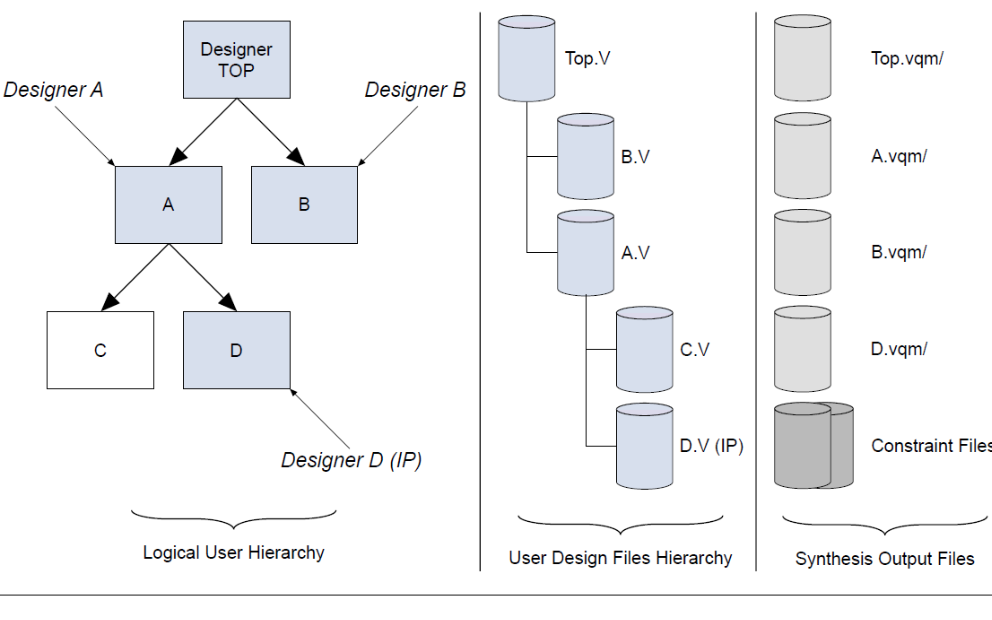

Incremental Compilation

通過對設計進行劃分,保留劃分后模塊編譯結果。 當對工程進行重新編譯時,編譯器會保留劃分模塊的編譯結果,只對修改部分進行重新編譯。

增量編譯步驟:

編譯工程

劃分模塊

設置模塊保留級別

編譯工程

對設計工程進行全編譯。

劃分模塊

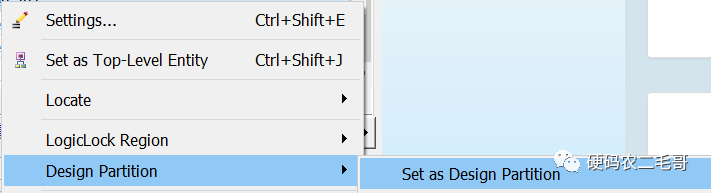

選擇要進行增量編譯的模塊,在quartus13.1版本中,點擊右鍵設置Design Partition-> Set as Design Partition。

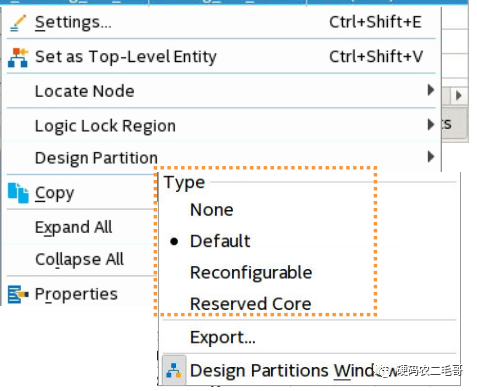

在quartus22.4版本中,Design Partition->Default

設置完成后,編譯工程。

設置模塊保留級別

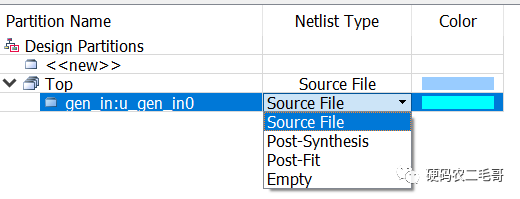

在quartus13.1版本中,設置Netlist Type。

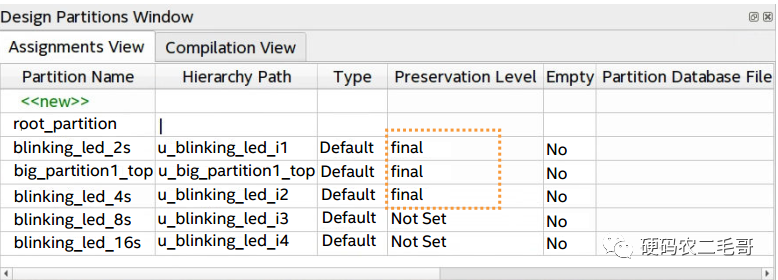

在quartus22.4版本中,設置Preservation Level,可以設置成Synthesized和Final。

當設置成Synthesized時,保留綜合網表,當設置成Final時,保留最終布局布線和時序特性。

完成以上步驟后,再進行編譯時,已經劃分的模塊就可以實現增量編譯,當修改工程其他部分,再進行編譯時,只對沒有劃分模塊進行編譯,從而減少編譯時間。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602043 -

布線

+關注

關注

9文章

766瀏覽量

84295 -

時序

+關注

關注

5文章

386瀏覽量

37290 -

編譯

+關注

關注

0文章

654瀏覽量

32814 -

LogicLock

+關注

關注

0文章

2瀏覽量

806

發布評論請先 登錄

相關推薦

什么是增量式編譯?

Quartus II 下FPGA管腳鎖定

基于Altera系列器件的邏輯鎖定方法學在FPGA設計中的應

LogicLock邏輯鎖定簡介

Vivado Design Suite 2015.3新增量編譯功能介紹

Synplify和QuartusⅡ邏輯鎖設計流程

淺析Vivado中增量編譯與設計鎖定方法與驗證

Vivadoz中增量編譯與設計鎖定

Quartus中的邏輯鎖定與增量編譯

Quartus中的邏輯鎖定與增量編譯

評論