總計:

方式一:普通IO口加上按鍵復位電路和上電自動復位電路

方式二:nCONFIG引腳輸入信號作為系統復位

方式三:用其他MCU控制FPGA的上電復位,既可以將MCU的復位引腳和FPGA的復位引腳連在一起,也可以MCU單獨引腳復位引腳對FPGA進行控制。

總結與討論:

疑問:

總計:

有人說FPGA不需要上電復位電路,因為內部自帶上電復位信號。也有人說FPGA最好加一個上電復位電路,保證程序能夠正常地執行。不管是什么樣的結果,這里先把一些常用的FPGA復位電路例舉出來,以作公示。

方式一:普通IO口加上按鍵復位電路和上電自動復位電路

上圖是兩種復位方式的集合,可以實現上電復位和按鍵復位。電路圖中左半部分是實現按鍵復位的,右圖則是實現上電自動復位的。

按鍵復位: 默認狀態電路圖為高電平,當按鍵按下后,電路產生一個低電平的信號,即產生一個下降沿,這樣的話,就可以實現低電平的復位信號了。

上電自動復位:剛上電的時候,電容導通,復位RST引腳處為低電平,當電容充滿電后,RST引腳處就為高電平了。這樣也產生了低電平的復位信號。

只要將相應的引腳連接至復位引腳處,就能控制電路系統的復位了。

方式二:nCONFIG引腳輸入信號作為系統復位

參考cycloneIII的handbook,可以發現下面這樣一段話。現摘錄如下:

下面則是一個很常用的復位電路,正好使用到了這部分的復位電路。電路中既有系統復位的部分,又有按鍵復位的部分。

具體的介紹如下,系統復位方式采用的普通的按鍵復位電路實現。而用戶復位按鈕,則是對nCONFIG引腳的控制進行復位的,這個引腳連接的是DEV_CLKn引腳,而在上面的介紹中,我們可以看到nCONFIG至少保持低電平500ns以上,就可以實現對整個cycloneIII系列FPGA的重新復位。需要注意的是,這要求QuartusII的設置中不能講DEV_CLRn配置為普通引腳。

方式三:用其他MCU控制FPGA的上電復位,既可以將MCU的復位引腳和FPGA的復位引腳連在一起,也可以MCU單獨引腳復位引腳對FPGA進行控制。

MCU控制FPGA的復位可以在方式一和方式二的方式上進行實現。

例如在底板的STM32中添加按鍵復位,這個復位既連接了STM32本身的復位信號,又連接了FPGA相應的復位信號引腳,這樣的話,就可以達到STM32和FPGA同時復位的效果。當然你也可以使用上電自動復位電路進行實現。

還有一種方式就是,MCU引出一個引腳,控制這個引腳輸入低電平,延時一段時間后再重新拉高,這樣的話,就會產生一個上升沿的信號,同樣可以控制FPGA復位。

總結與討論:

總之,實現FPGA復位的方式有很多。可能不僅僅上面例舉的一些。而且,上面的實現方式,可能并不是最好的,僅僅作為一種參考。

下面進行一些討論。

FPGA在組合電路中是沒有時鐘信號的,這樣的話,也就不可能添加所謂的復位信號,復位信號應該不是必須的。

疑問:

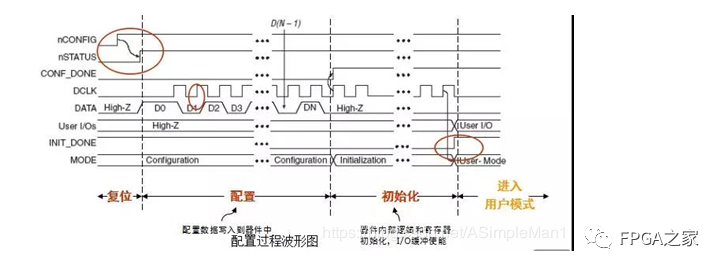

cycloneIII系列程序的下載過程如下:

(1)首先注意的nCONFIG引腳,當其由低電平進入高電平時,程序進入配置過程。

在此過程中,nSTATUS引腳也由低置高,程序進入配置過程。

波形有從低電平到高電平的跳變過程,說明進入了配置過程。

(2)然后注意的引腳是CONFIG_DOWN引腳,當其由低電平進入高電平時,程序配

置完成,進入初始化,這部分才算程序下載完畢。

這樣的話,我是否可以使用CONFIG_DOWN引腳輸出,連接相應的復位RST引腳,遮樣的話,就可以自動的上電自動復位,而不用添加任何的輔助電路?

歡迎大家樓下一起交流

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601826 -

復位電路

+關注

關注

13文章

322瀏覽量

44536 -

上電復位

+關注

關注

1文章

39瀏覽量

15776

發布評論請先 登錄

相關推薦

FPGA中三種常用復位電路

FPGA復位電路的設計

FPGA設計中常用的復位設計

FPGA的理想的復位方法和技巧

FPGA怎么搭復位電路 fpga復位電路設計方案

硬件設計——外圍電路(復位電路)

FPGA復位電路的實現方式

FPGA復位電路的實現方式

評論