正在尋找一種方法來減少在內存控制器/PHY 和子系統驗證項目中定義和跟蹤功能驗證目標的工作量?

如果您尚未在內存項目中部署使用驗證計劃、功能和時序覆蓋模型的最佳實踐,請了解為什么建議這樣做...

功能和時序覆蓋閉合流程的關鍵屬性

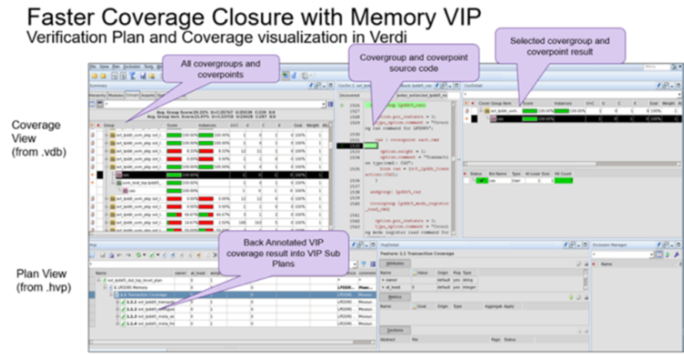

? 自動生成覆蓋率報告,可靈活指定要啟用

的不同類型的覆蓋率 ? 自動將覆蓋率數據反向注釋到測試計劃中,確定覆蓋目標

的進度 ? 快速識別與未加密源代碼相關的剩余覆蓋點,實現更快的覆蓋收斂

? 用戶可以擴展內置覆蓋范圍,以根據內置的VIP采樣事件和組添加自己的箱,或使用任何采樣事件或數據

創建自己的組 ?基于模擬器的覆蓋實用程序(例如排除箱/覆蓋點/覆蓋組)可用于IP/子系統不支持的場景/設置Synopsys 內存模型 (VIP) 具有內置的驗證計劃、功能和定時覆蓋模型,可加速覆蓋收斂。提供覆蓋模型是為了幫助跨配置設置、模式寄存器設置、功能和時序參數的多種組合運行完整的驗證方案。

Synopsys Memory VIP 支持來自 JEDEC、ONFi、SD 和 SPI(DDR5、LPDDR5、DFI 5.0、HBM3、GDDR6 和 NVDIMM-P/N)等標準組織的最新批準和草案規范,以及與 VCS 和 Verdi 的原生集成和優化。

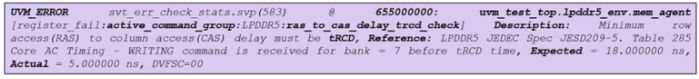

覆蓋模型實現基于 System Verilog 構造(覆蓋組、覆蓋點、箱、非法箱),它是“協議規范版本感知”,這意味著如果不適用于配置的協議規范版本,則忽略覆蓋點/箱。

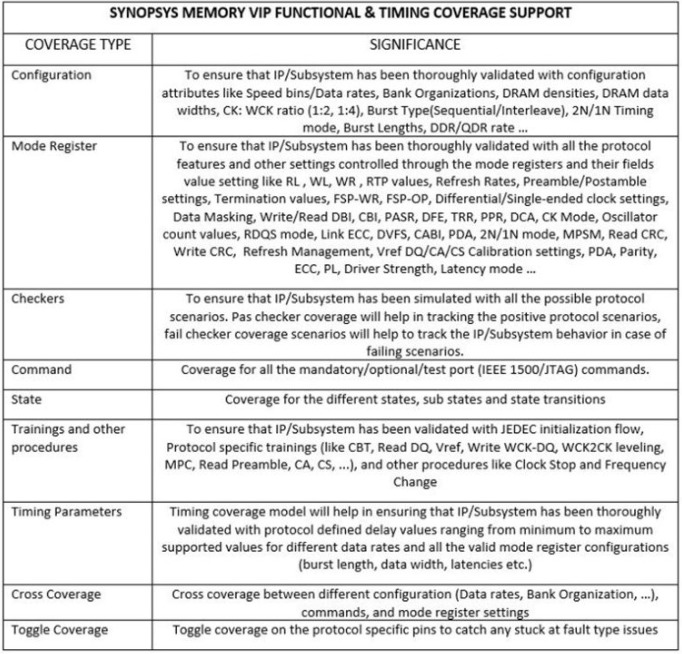

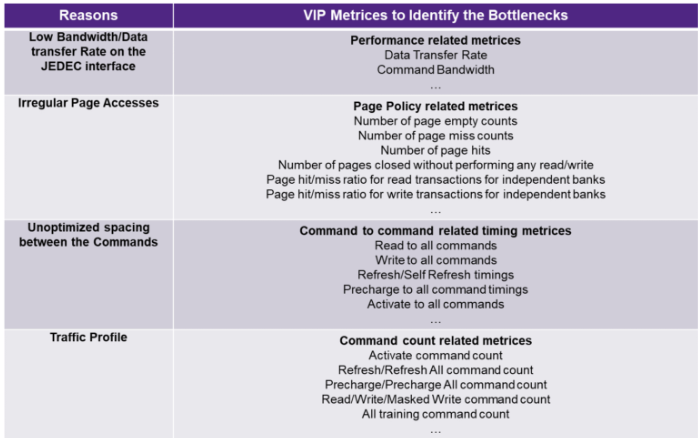

新思科技內存VIP覆蓋模式包括:

·驗證計劃 - 驗證計劃顯示每個功能覆蓋組如何直接映射到協議規范方案。驗證計劃是分層的,子計劃基于不同類型的覆蓋范圍。

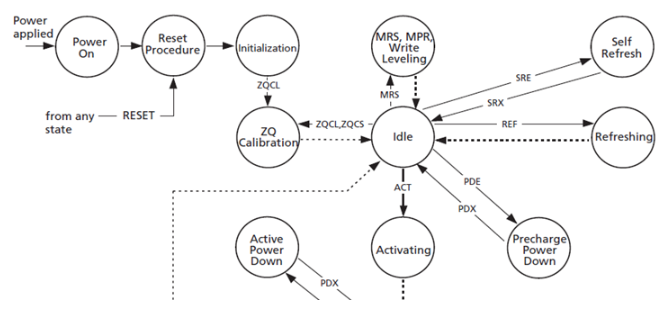

? 功能覆蓋模型 – 功能覆蓋支持包括配置、模式寄存器、檢查、命令、狀態、訓練、定時參數、切換以及有效的交叉覆蓋。

? 定時覆蓋模型 – 定時覆蓋支持包括命令到命令延遲、掉電時間、自刷新時間、建立/保持,以及不同數據速率和所有有效模式寄存器配置(突發長度、數據寬度、延遲等)的交叉覆蓋。

審核編輯:郭婷

-

控制器

+關注

關注

112文章

15879瀏覽量

175338 -

寄存器

+關注

關注

31文章

5250瀏覽量

119192 -

PHY

+關注

關注

2文章

295瀏覽量

51553

發布評論請先 登錄

相關推薦

物理內存模型的演變

發放迅雷vip

史上最難注冊成為VIP的APP

RT1060注冊內存被TFLite Micro模型中的其他函數覆蓋了怎么解決?

全球通VIP俱樂部建設

WCDMA室內覆蓋規劃研究 填補建筑物內盲區

Rust語言助力Android內存安全漏洞大幅減少

跳過DDR VIP模型的初始化

DDR VIP模型的無縫快速初始化

覆蓋模型 – 填補內存VIP的漏洞

覆蓋模型 – 填補內存VIP的漏洞

評論