從一開始,NVMe 就旨在支持多個主機訪問共享媒體。早期實施包括 PCIe 內置設備,如端點 (EP)、根復合體 (RC) 和根復合體集成端點 (RCiEP);隨著時間的推移,云和存儲基礎架構產生了對遠程存儲的需求。

NVMe 實現可以解決 SATA 點對點架構和 SAS 占用的空間問題。在這兩個領域成功采用是由于低延遲和通用存儲接口的承諾,無論位置如何。盡管這兩個用例中的驗證挑戰相似,但它們仍然需要不同的思維過程。

點對點架構中使用的 NVMe 要求以控制器實現為中心進行驗證。在這種情況下,控制器的數量< 10,邏輯內置于硬件、應用軟件和固件中。帶寬和吞吐量是點對點架構中的關鍵度量。NVMe控制器設計人員需要在實現中做出權衡,以實現成本/性能目標,盡管關鍵權衡是在各種功能的硬件和軟件實現之間進行的。這些權衡的細節不會在這里討論,但足以說明線路的位置對驗證工程師很重要。

硬件/軟件分區帶來了驗證的復雜性。傳統上,硬件在仿真中得到驗證,因為它需要更嚴格和徹底的測試。軟件實現的功能在協同仿真和硬件加速驗證環境中經過輕度測試,因為如果更新不影響硬件,則更新成本不高。我們在這里看到的驗證挑戰是驗證用于加速各種軟件功能的實現特定硬件。在這里,軟件通常需要設置并卸載到硬件。根據軟件實現的復雜程度,仿真可能需要數天時間才能達到驗證目標點。協同仿真的仿真啟動是一種直接的進度威脅。

為了解決仿真中的硬件和軟件問題,許多驗證團隊利用ZeBu等硬件加速平臺。硬件加速允許 NVMe 驅動程序在可以連接到仿真設備的 CPU 上啟動。這里最大的挑戰是可重用性。傳統上,在仿真中編寫的測試針對仿真測試平臺進行了優化,并不完全適用于加速環境。Synopsys 的 ZeBu 平臺已通過支持在加速中重用仿真驗證 IP 并保留仿真和加速平臺之間的相同用戶界面,解決了這一問題。由于 ZeBu 加速平臺的執行性能提高了 100 倍,現在可以啟動軟件。這種方法允許模擬更深入地進入測試,以發現可以審查管道、內存帶寬、翻轉條件或卡住或一次性故障的功能錯誤。加速還允許基于波形的調試,這是解決基于硬件的問題所必需的。

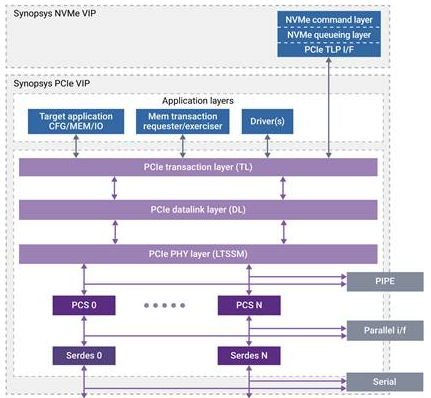

需要考慮其他仿真優化來縮短測試運行時間。對于以 PCIe 作為傳輸的 NVMe,可以刪除整個 PCIe 堆棧,從而公開 NVMe 和 PCIe 堆棧之間的專有 TLP 接口。PCIe 堆棧往往很大,需要設置時間。刪除堆棧也會刪除此基于規范的設置時間。刪除 PCIe 傳輸時,需要考慮其他事項,例如緩沖區管理、中斷等。對于使用 AXI 接口(與專有 TLP 接口相比)的 PCIe 設計 IP,由于 AXI 是公共標準,因此更容易刪除 PCIe 堆棧。這使得AXI接口的中斷相對便攜。

點對點調試相對簡單,盡管通常很乏味。事務和模擬日志用于追蹤與 NVMe 命令關聯的內存事務。記分牌也可以在內聯和邊帶記分牌中得到有效利用。調試的另一個關鍵方面是監視在內存中構造和操作的結構。跟蹤從未進入完成隊列的完成可能非常困難,因為控制器正在主機或驗證 IP 的監視之外執行內存訪問。擁有“監視”此內存的能力,無論該功能內置于驗證IP還是驗證組件中,都將節省無數小時的調試時間。要考慮的另一個驗證工具是跟蹤位于鏈路另一端的控制器、命名空間和其他資源的狀態。通過跟蹤驗證環境中的狀態,可以通過以下方式節省大量調試時間:

? 標記測試編寫器格式不正確的命令 ? 標記由于版本不足或功能

不支持而導致控制器不支持的命令

? 標記與尚未設置的先決條件設施相關的問題

一旦驗證環境可以跟蹤控制器和命名空間,相同的跟蹤將自動擴展到具有多個控制器/命名空間的環境,從而為上述調試節省時間提供乘數效應。

設計最有效的核查環境以及選擇最佳的核查組件對于實現核查時間表的“左移”至關重要。通過重用組件、序列等,可以花更多的時間來發現/修復真正的 DUT 錯誤。不要低估良好的調試工具所節省的時間 - 防止不良測試,指出DUT問題,標記DUT錯誤配置等。

審核編輯:郭婷

-

控制器

+關注

關注

112文章

16206瀏覽量

177427 -

PCIe

+關注

關注

15文章

1224瀏覽量

82445 -

nvme

+關注

關注

0文章

218瀏覽量

22584

發布評論請先 登錄

相關推薦

免疫系統的主組織相容復雜性及其應用

基于構件回歸測試的復雜性度量框架

PCB復雜性怎樣來解決

大數據分析學習的挑戰:復雜性、不確定性及涌現性

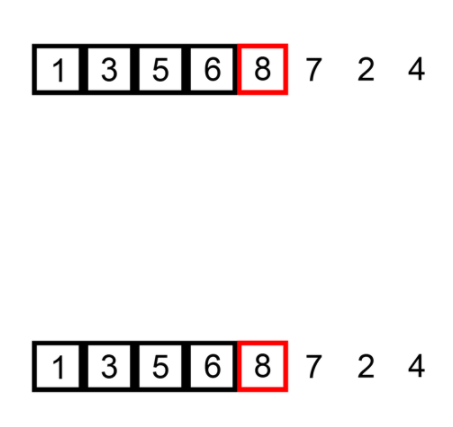

插入排序算法的復雜性、性能、分析

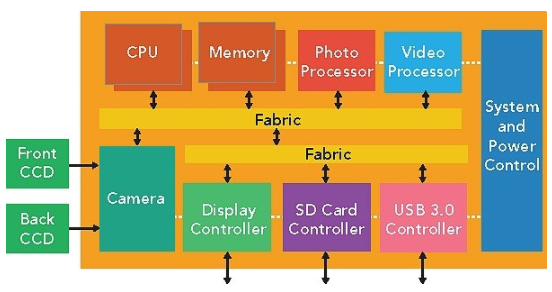

通過場景模型驗證管理SoC復雜性

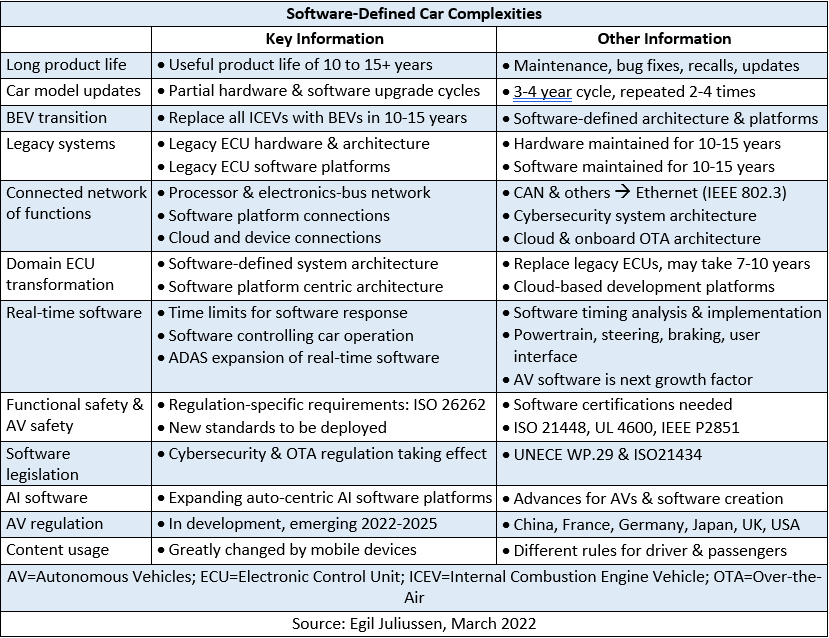

駕馭軟件定義車輛的復雜性

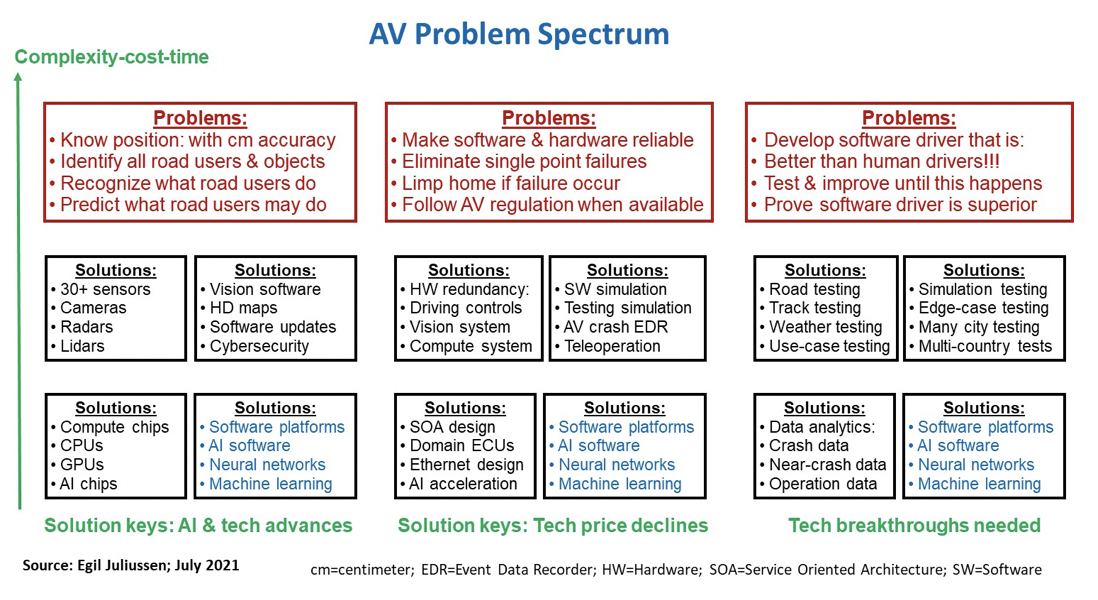

了解 AV 復雜性

管理NVMe驗證復雜性

管理NVMe驗證復雜性

評論