為什么引入寄存器模型

新需求:為帶寄存器的DUT搭建UVM仿真環境

為了讀寫DUT中的寄存器:UVM提供了 配置寄存器的總線 (bus_agent=sqr+drv+mon)——前門訪問DUT中的寄存器值

為了方便參考模型查看DUT中寄存器的值:UVM提供了 寄存器模型 ,作用如下

- 讓前門訪問操作更方便:將對DUT中寄存器的總線操作進行封裝,通過寄存器模型這一暴露的接口可以方便實現對DUT的讀寫操作

- 新加入后門訪問操作:通過層次化引用來讀寫DUT中寄存器的值(不消耗仿真時間),同樣使用寄存器模型作為暴露的接口。

為DUT中的寄存器設定一個參考模型:引入UVM_PREDICT_DIRECT的predict操作,具體實現如下

- 在my_model中, 每得到一個新的transaction, 就先從寄存器模型中得到counter的期望值( 此時與鏡像值一致) ,

- 之后將新的transaction的長度加到counter中,

- 最后使用predict函數將新的counter值更新到寄存器模型中。predict操作會更新鏡像值和期望值。

- 在測試用例中, 仿真完成后可以檢查DUT中counter的值是否與寄存器模型中的counter值一致

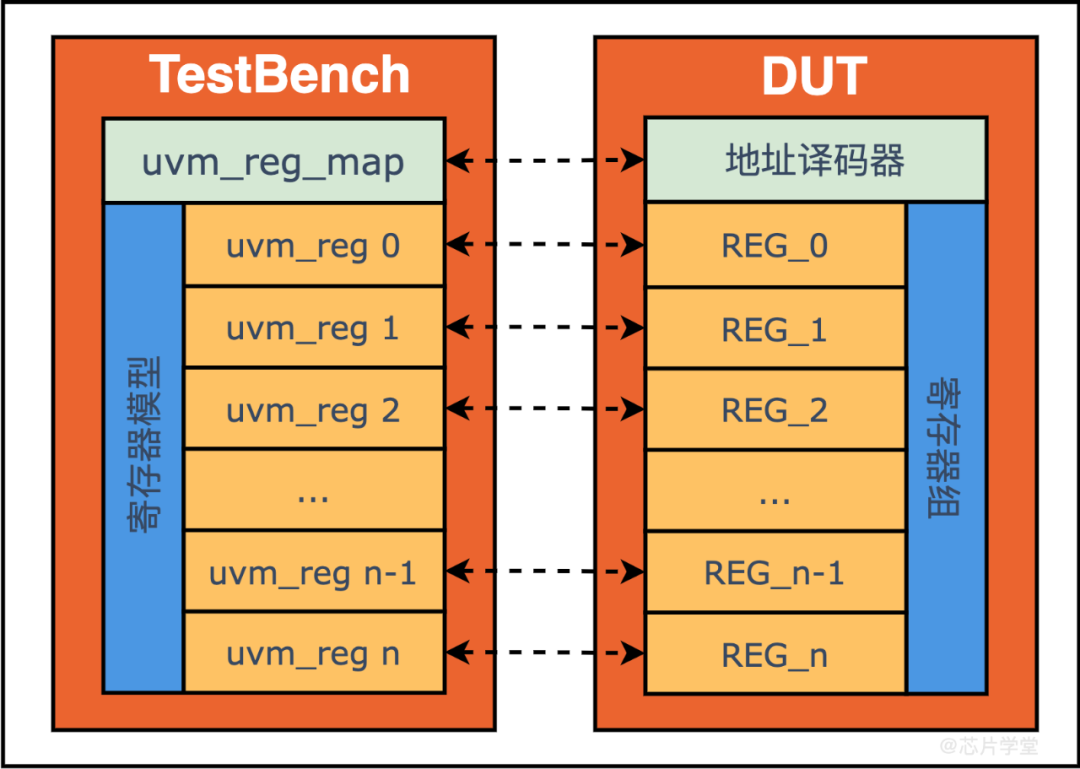

寄存器模型中的基本概念

- uvm_reg_field:寄存器的域,是一個uvm_reg中的一個字段/域

- uvm_reg:寄存器,至少包含一個uvm_reg_field

- uvm_mem:存儲器,

- uvm_reg_file:引入后,uvm_reg配置時,其路徑就不再需要uvm_reg_block的名字

- uvm_reg_block:包含uvm_reg或者其他uvm_reg_block(可設計層次化的寄存器模型)。一個寄存器模型中至少包含一個uvm_reg_block

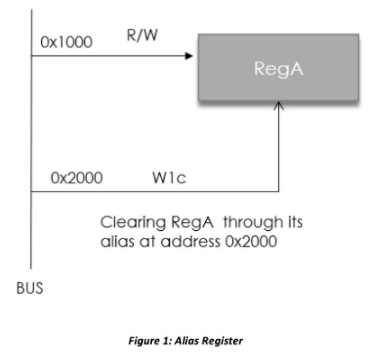

- uvm_reg_map:存儲所有寄存器的地址。每個reg_block內部, 至少有一個( 通常也只有一個) uvm_reg_map。

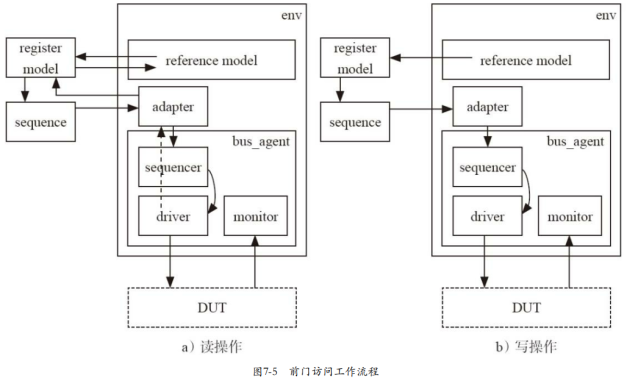

寄存器模型前門訪問的實現

參考模型>寄存器模型>轉換器>bus_sequencer>driver>dut>driver---

寄存器模型后門訪問的實現

- 在reg_block中調用uvm_reg的configure函數時, 設置好寄存器的第三個路徑參數(即后門訪問路徑:DUT內寄存器相對DUT頂層的路徑,如:counter[31:16]表示dut中名為counter的寄存器的[31:16]位)

- 在將寄存器模型集成到驗證平臺時, 設置好DUT的根路徑hdl_root(這樣才能定位DUT在哪里)

- 在sequence中, 使用peek和poke任務 或者 UVM_BACKDOOR形式的read和write

寄存器模型中的期望值與鏡像值

- 期望值:希望向此寄存器中寫入的值——可作為DUT中寄存器的參考模型

- 鏡像值:最大可能地與DUT保持同步

常用操作對期望值和鏡像值的影響

- 針對DUT寄存器的read&write操作:用操作后DUT中寄存器的值更新 期望值和鏡像值(會分前門/后門訪問)

- 針對DUT寄存器的peek&poke操作:用操作后DUT中寄存器的值更新 期望值和鏡像值 (只有后門)

- 針對期望值的get&set操作:更新期望值, 不更新DUT中寄存器,不更新鏡像值

- update操作:用期望值 更新DUT中寄存器 和 鏡像值

- mirror操作:用DUT中寄存器的值 更新 期望值和鏡像值

- randomize操作:隨機化 期望值,不隨機化鏡像值

- predict操作:

- 參數為UVM_PREDICT_READ和UVM_PREDICT_WRITE時:用操作后DUT中寄存器的值更新 期望值和鏡像值——在read/peek和write/poke操作對DUT寄存器完成讀寫后自動調用

- 參數為UVM_PREDICT_DIRECT時:人為更新期望值和鏡像值,不更新DUT中寄存器

引入reg_predictor

引入reg_predictor的原因:配置寄存器的總線存在多個master時,可能存在 不通過寄存器模型 訪問總線來配置DUT中寄存器的情況,這時 寄存器模型 就不能檢查到 DUT中寄存器的變化 ,所以需要引入reg_predictor, 通過monitor檢測總線,將采集到的tr發送給uvm_reg_perdictor 。如下圖,

- 虛線為通過自動預測途徑更新寄存器模型的路徑。

- 實現為經由predictor更新寄存器模型的路徑。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

轉換器

+關注

關注

27文章

8634瀏覽量

146879 -

寄存器

+關注

關注

31文章

5324瀏覽量

120024 -

UVM

+關注

關注

0文章

181瀏覽量

19142 -

DUT

+關注

關注

0文章

189瀏覽量

12344

發布評論請先 登錄

相關推薦

IC驗證"為什么要學習UVM呢"

什么?驗證工程師驗證工程師能夠從本書學會如下內容:如何用UVM搭建驗證平臺,包括如何使用sequence機制、factory機制、callback機制、寄存器模型(register model)等。一些

發表于 12-01 15:09

從設計的角度一塊兒來看下這些UVM寄存器模型

對于搞驗證的同學來講,UVM里面中關于寄存器的概念自然是耳熟能詳,對于搞設計的小伙伴來講,也許我們對于使用的場景和UVM寄存器模型對照并沒有

發表于 06-23 16:06

介紹UVM寄存器模型訪問上的一些內容

模型的構建和集成到驗證環境的基礎上。本文將展開介紹寄存器模型訪問上的一些內容,包括寄存器域段的成員值、寄存器的前后門訪問以及具體各種訪問方法

發表于 07-04 15:36

集成級的UVM寄存器模型

UVM使得驗證測試平臺的結構得以標準化,各種復用策略及標準對于提高驗證質量、縮短項目周期都非常有效。垂直重用是常見的復用策略之一,即同一項目測試平臺復用于不同驗證層次。驗證中常將最底層的IP級驗證平臺向更高的集成層復用,而UVM寄存器

發表于 09-15 11:49

?15次下載

簡化UVM寄存器模型的使用教程

當我開始使用UVM RAL時,我無法理解UVM基類庫對更新Desired和Mirror 寄存器的解釋。覺得使用的術語并不能準確地反映里面的真實的意思。花了一些時間后,我想出了一個表格,它可以幫助我理解

簡化UVM寄存器模型的使用

當我開始使用 UVM RAL 時,我無法理解 UVM 基類庫對更新所需值和鏡像值寄存器的值有什么看法。我還認為,所使用的術語沒有準確反映其意圖。花了一些時間后,我想出了一個表,幫助我了解寄存器

基于DUT內部寄存器值的鏡像

(outdated) 。 寄存器模型可以通過使用 uvm_reg_field::mirror() , uvm_reg::mirror() , 或 u

UVM為什么要引入寄存器模型呢?

UVM為什么要引入寄存器模型呢?

評論