1、 前言

數字鐘是一種用數字電路技術實現時、分、秒計時的裝置,與機械式時鐘相比具有更高的準確性和直觀性,且無機械裝置,具有更長的使用壽命,因此得到了廣泛的應用。

2.設計任務和要求

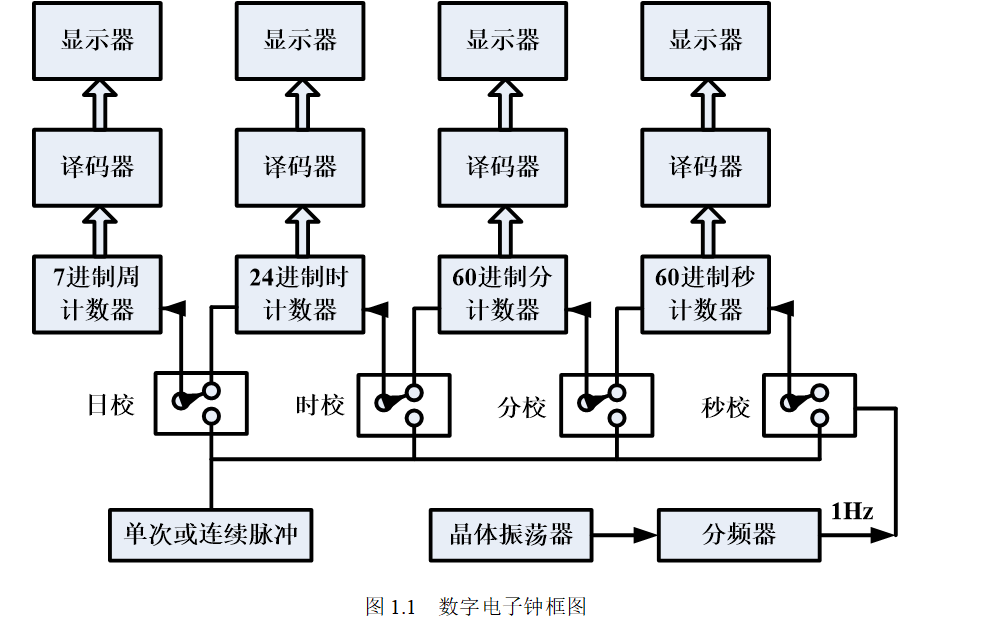

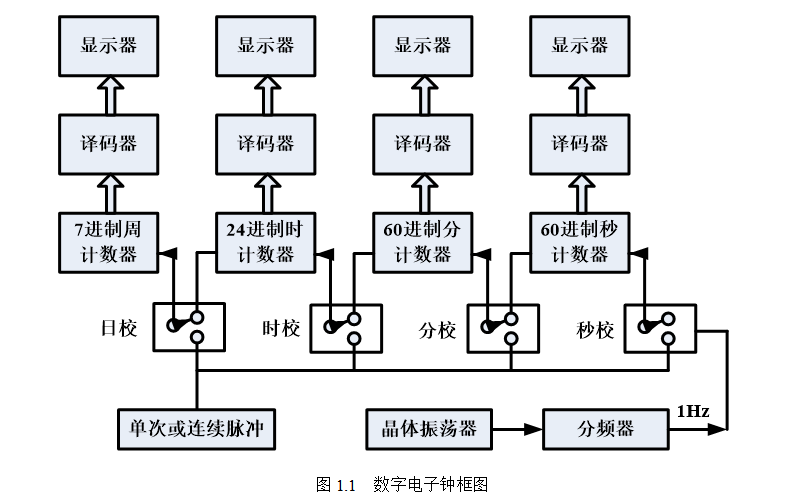

用中小規模集成電路設計一臺能顯示日、時、分秒的數字電子鐘,要求如下:

1.由晶振電路產生1Hz 標準秒信號。

2.秒、分為00—59六十進制計數器。

3.時為00—23二十四進制計數器。

4.周顯示從1—日為七進制計數器。

5.可手動校正:能分別進行秒、分、時、日的校正。 只要將開關置于手動位置,可分別對秒,分、時、日進行手動脈沖輸入調整或連續脈沖輸入的校正。

6.整點報時。 整點報時電路要求在每個整點前鳴叫五次低音(500Hz),整點時 再鳴叫一次高音(1000Hz)。

3、實驗器件選擇

本次實驗中需使用到的元器件如下表所示

| 器件名稱 | 型號 | 數量 | 功能 |

|---|---|---|---|

| 芯片 | 74HC00 | 2 | 與非 |

| 芯片 | 74HC04 | 1 | 非門 |

| 芯片 | 74HC74 | 1 | 2分頻 |

| 芯片 | 74HC161 | 7 | 16進制 |

| 芯片 | 4060 | 1 | 二進制計數器 |

| 芯片 | 4511 | 1 | 驅動LED |

| 晶體振蕩器 | 32768 | 1 | 產生頻率脈沖 |

| 電阻 | 12. | 1 | --- |

| 電阻 | 32米 | 1 | --- |

| 共陰單8顯示器 | 0.56英寸 | 7 | 顯示數字 |

| 可調電容 | 102 | 2 | --- |

表1元器件列表

4、方案設計

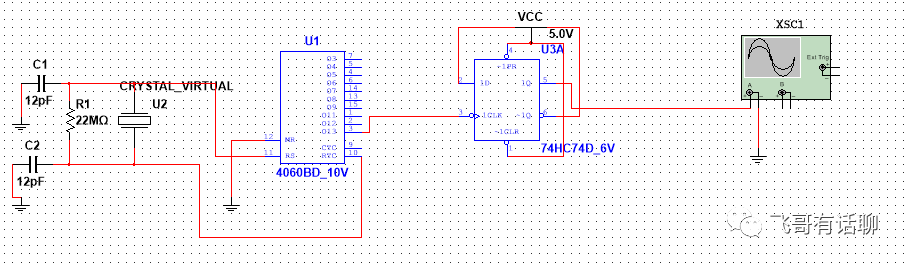

(1)脈沖信號電路設計方案

石英晶體主要成分是二氧化硅,它的物理化學性質十分穩定,本電路的顯著優點是頻率穩定性極好,理論上可達1.000000?Hz的精確度,石英晶體產生的信號經過4060可以達到14分頻,再經過一個D觸發器74HC74就實現了15分頻輸出1HZ信號。

(2)秒、分電路設計

這個模塊就是“秒”的部分,由74HC161芯片產生16進制計數,然后利用送數功能,當計時到1001(即十進制數字9)送0,實現0 ~ 9的循環,作為秒的個位。同時將1001經過與非門之后送到下一片74HC161芯片作為時鐘信號,也就是個位計數十次十位進一次位。十位計數到0101(即十進制5)后經過與非門送到Load置數,同時作為下一片芯片的時鐘信號。十位實現0~5的循環。這樣,秒的個位和十位就完成了。

分的設計和秒類似,這里就不再贅述。

(3)時電路設計

時的電路設計與前面的分和秒類似,但是有些不同,主要是進位上面需要注意一下,個位上先是0 ~ 9循環兩次,然后是0 ~ 4,接著向十位進位。十位上只能是0~2的循環。設計思路如下:個位上,當計數到1001時經過與非門產生送數,計時器回到0,并且向十位產生進位信號。十位上,當個位產生0100和十位產生0010時(組合后就是十進制24),產生的信號送到復位端,讓個位和十位復位,并且信號輸入到下一級的CLK上面。這樣就可以達到要求了。

(4)周電路設計

周要實現周一~周日(日用8代替),因此,當計數到0111時經過與非門置數1,同時因為要顯示8(跳過7),所以利用譯碼器的LT可以實現全亮,這樣就達到了設計要求。

(5)校時電路設計

在剛剛開機接通電源時,由于日、秒、分、時為任意值,所以,需進行調整。 置開關在手動位置,分別對時、分、秒、日進行單獨計數,計數脈沖由單次脈沖或連續脈沖輸入。

方案實現:在芯片的CLK引出一個接口,既可以接收前一級的進位信號,也可以單獨輸入一個高頻率脈沖信號,方便調整時間。

總體連接示意圖

整體電路圖

實物圖1

實物圖2

仿真動態圖

以上就是關于數字時鐘的設計。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42581 -

電路設計

+關注

關注

6665文章

2428瀏覽量

203320 -

時鐘

+關注

關注

10文章

1720瀏覽量

131365 -

數字電路

+關注

關注

193文章

1600瀏覽量

80501 -

數字電子鐘

+關注

關注

7文章

27瀏覽量

20583

發布評論請先 登錄

相關推薦

[求助]哪位高手能詳細地給我講講74LS系列的這幾塊芯片啊?謝謝了

組合邏輯電路設計實驗

VHDL硬件描述語言與數字邏輯電路設計

數字電子技術的八個課題和設計實例詳細說明

數字電子技術的8個實驗資料說明

數字電子鐘邏輯電路設計

數字電子鐘邏輯電路設計

評論