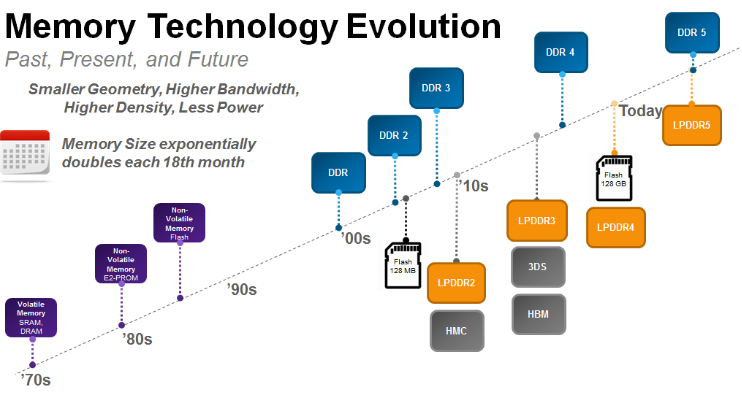

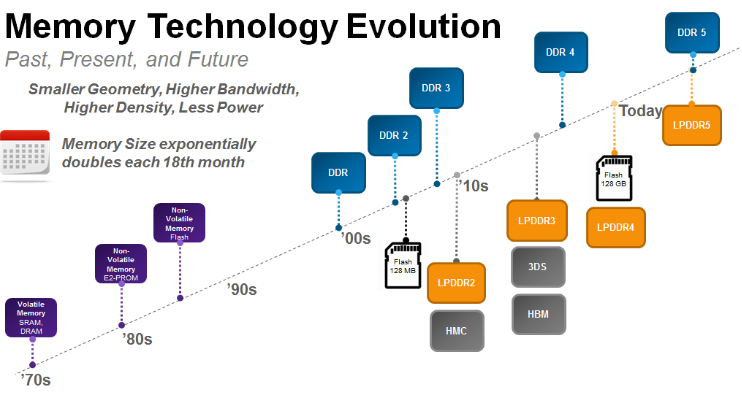

在存儲器密度低、性能緩慢且需要昂貴的硅空間的時代。然后我快進到未來,當內存技術已經發(fā)展到支持巨大的密度,超快的速度,同時保持低功耗,所有這些都在非常小的幾何結構中。

我概述了各種內存技術及其支持的細分市場。為了跟上這種內存技術發(fā)展的步伐,設計和驗證工具以及創(chuàng)建和產品化這些技術的方法也得到了發(fā)展。

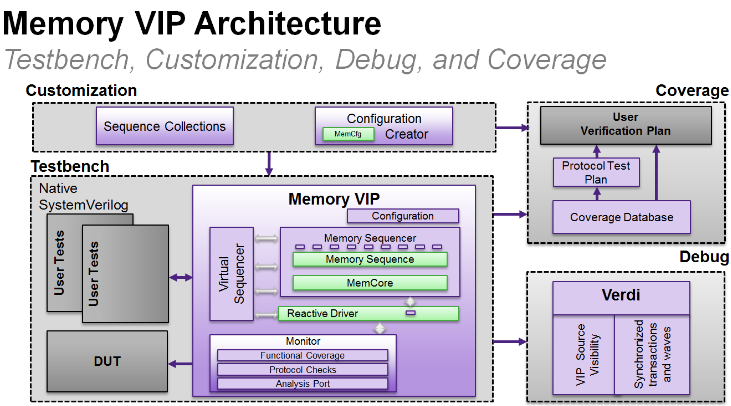

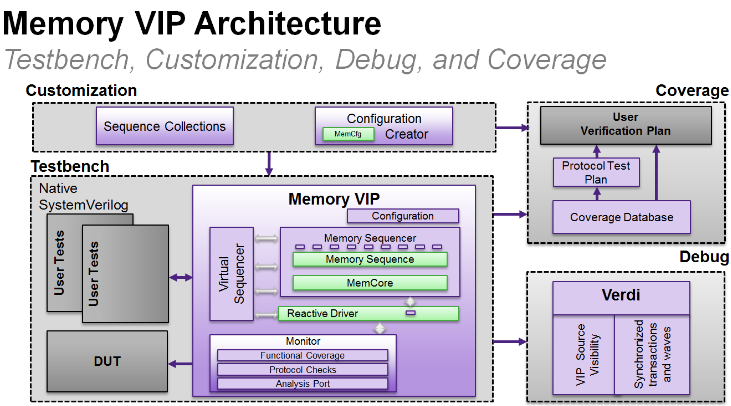

這種存儲器的演變給驗證工程師帶來了一系列全新的挑戰(zhàn)。為了取得成功,驗證必須在設計周期的早期發(fā)展為徹底、高效和有效。此外,它必須依賴于對SystemVerilog的本機支持,利用最先進的驗證技術進行測試平臺創(chuàng)建和定制,以及調試和覆蓋率收斂。

需要更快、經過驗證且最先進的前端內存驗證基礎設施來解決最新內存創(chuàng)新帶來的復雜性。利用行業(yè)標準的通用驗證方法 (UVM),支持高級協議級調試,以及具有內置覆蓋范圍和計劃的加速驗證收斂,驗證工程師可以在短時間內自信地驗證內存技術。

審核編輯:郭婷

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯系本站處理。

舉報投訴

相關推薦

labview用串口采集和用USB采集,使用兩個完全不同的程序同時采集的數據,怎么能保持同步,同步就是能保證同一時間采集的數據,從而能放在同一個時間列中,怎么實現呢?大神幫幫忙呀

發(fā)表于 07-14 20:41

2015年全球領先的半導體制造公司德州儀器(TI)攜手中國電源學會(世紀電源網),推出免費的全國巡回“TI 現場培訓”課程,特別邀國內頂尖專家,為你講解電源設計相關方面的技術知識,將覆蓋初、中、高級

發(fā)表于 07-17 06:25

使用高級校準技術驗證收發(fā)器FPGA

發(fā)表于 09-19 09:05

Arm架構安全技術介紹中,tz是否有定義內存加密的標準或者接口?內存的加密與驗證是在之前提到的memory filter上進行的嗎?

發(fā)表于 09-02 14:22

包括靜態(tài)內存、動態(tài)內存的所有接口的驗證

發(fā)表于 02-16 07:03

DDR驗證和調試的高級方法:Memory Design and ValidationChip/Component DesignPrecise understanding of circuit

發(fā)表于 06-29 17:16

?21次下載

華為NodeB采用的同步方式,失去同步源后可以保持的時間

WCDMA基站之間是不需要同步的。系統(tǒng)時鐘的時鐘源有GPS、BITS、Iub接口(從RNC來的時

發(fā)表于 06-30 09:43

?1709次閱讀

俄勒岡州威爾遜維爾,2016 年 3 月 2 日– Mentor Graphics 公司(納斯達克代碼:MENT)今日宣布,推出首個完全原生的 UVM SystemVerilog 內存驗證 IP 庫,該內存

發(fā)表于 03-02 14:03

?1099次閱讀

逆變器控制的永磁同步電機的試驗驗證_黃勇

發(fā)表于 01-05 15:33

?0次下載

隨著軟件運行時驗證技術的發(fā)展,出現了許多面向C語言的運行時內存安全驗證工具。這些工具大多是基于源代碼或者中間代碼插樁技術來實現

發(fā)表于 04-20 14:42

?5次下載

今天我們來講講進程間使用共享內存通信時為了確保數據的正確,如何進行同步?

![的頭像]() 發(fā)表于

發(fā)表于 05-11 18:25

?1542次閱讀

在這篇博客中,我將展示另一個功能,它使Verdi Protocol Analyzer成為調試內存協議問題和驗證正確系統(tǒng)行為的首選工具。此外,該工具還可用于驗證命令序列器以及 DUT 和內存

![的頭像]() 發(fā)表于

發(fā)表于 05-26 16:34

?762次閱讀

請問下位機與上位機如何保持時鐘同步呢? 下位機與上位機之間的時鐘同步是確保兩者能夠按照相同的時間基準進行操作的關鍵。在許多實時控制和嵌入式系統(tǒng)中,時鐘同步對于確保精確的數據采集、交互和

![的頭像]() 發(fā)表于

發(fā)表于 01-16 17:11

?1392次閱讀

三星電子近日宣布了一項重要進展,其專為高級車載信息娛樂系統(tǒng)(IVI)及高級駕駛輔助系統(tǒng)(ADAS)設計的LPDDR4X車載內存已成功通過高通最新驍龍數字底盤平臺的嚴格驗證。這一成就不僅

![的頭像]() 發(fā)表于

發(fā)表于 08-27 16:02

?438次閱讀

電子設備的內存技術。以下是對DDR內存的工作原理與結構的介紹: 一、工作原理 時鐘同步 :DDR內存是同

![的頭像]() 發(fā)表于

發(fā)表于 11-20 14:32

?177次閱讀

使用高級驗證與內存技術保持同步

使用高級驗證與內存技術保持同步

評論