STA的準備工作包括:設定時鐘、指定IO時序特性、指定false path和multicycle path

1 什么是STA環境

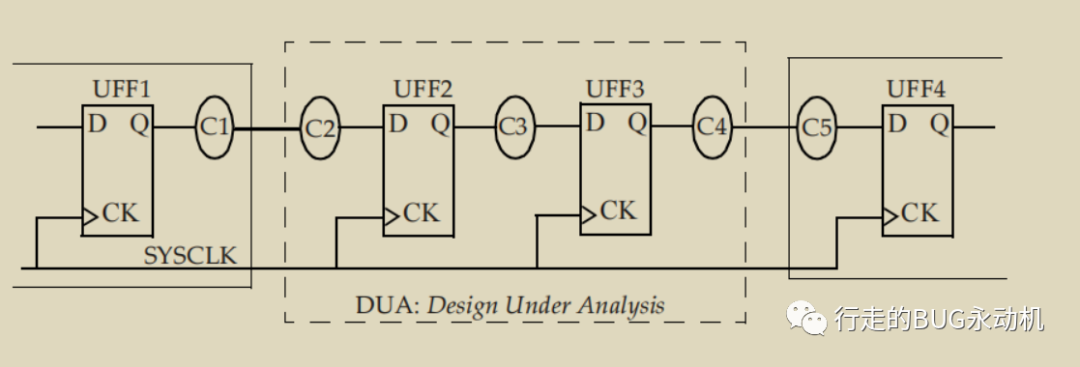

看下面這張圖,假定Design Under Analysis(DUA)會與其他同步設計交互,這意味著DUA會從前一級觸發器接收數據,并將數據發送到DUA后一級觸發器

為了對這種設計執行STA,需要指定觸發器的時鐘、進入DUA和退出DUA的所有路徑上的時序約束

2 指定時鐘

定義時鐘時需要提供以下信息:

- Clock source:可以是design的port,也可以是design內部的pin

- Period:時鐘周期

- Duty cycle:高電平持續時間和低電平持續時間

- Edge time:上升沿和下降沿出現的時刻

通過時鐘定義,所有內部的timing path都將受到約束,表明所有的internal path都可以用時鐘路徑來分析

下面是一個基本的時鐘定義:

create_clock \\

-name SYSCLK \\

-period 20 \\

-waveform {0 5} \\

[get_ports SCLK]

在這個例子中,定義的時鐘名稱為SYSCLK,并且指定定義的時鐘是在端口 SCLK上定義的

SYSCLK的時鐘周期時20(如果沒有明確指定時間的單位,默認是ns)

在-waveform中,第一個變量是上升沿出現的時刻,第二個變量是下降沿出現的時刻,因此在這個例子中,上升沿出現在0ns,下降沿出現在5ns

這個例子對應的波形圖如下

-waveform中可以指定任意數量的邊沿,但是所有的邊沿必須在一個周期之內

邊沿時刻從0時刻之后的第一個上升沿開始,然后依次是下降沿、上升沿、下降沿……

-waveform {time_rise time_fall time_rise time_fall ...}

在-waveform中需要指定偶數個邊沿,并且-waveform指定的是一個周期內的波形,在后續周期中不斷重復

如果沒有指定-waveform,默認是

-waveform {0, period/2}

下面看一個不使用-waveform選項的時鐘定義

create_clock -period 5 [get_ports SCAN_CLK]

其對應的波形圖如下:

在這個例子中,由于沒有指定-name,因此定義時鐘名稱與端口名稱相同

再來看另一個例子

create_clock -name BDYCLK \\

-period 15 \\

-waveform {5 12} \\

[get_ports GBLCLK]

其對應的波形圖如下:

在這個例子中,根據-waveform可以知道,第一個上升沿出現在5ns,第一下降沿出現在12ns

因為選項-waveform給出的上升沿和下降沿時刻會在每個cycle里重復,又因為-period指定周期是15ns,

所以在第二個cycle中,上升沿應該出現在15+5=20ns處

下降沿出現在15+12=27ns處

再來看另外兩個例子:

# Figure (a)

create_clock -period 10 \\

-waveform {0 5} \\

[get_ports FCLK]

#Figure (b)

create_clock -period 125 \\

-waveform {100 150} \\

[get_ports ARMCLK]

對應的波形圖如下:

對于圖(a),周期為10ns,上升沿出現在5ns,下降沿出現在10ns

在第二個cycle中,上升沿出現在10+5=15ns,下降沿出現在10+10=20ns

對于圖(b),周期為125ns,從選項-waveform {100 150}可以知道,上升沿出現在100ns處,并且 high duration = 150-100=50ns,那么low duration = period - high duration,即low duration = 75ns

因為150ns的時刻已經超出了第一個cycle的時間范圍,并且low duration的時長小于上升沿出現的時刻,那么可以推斷出 在第一個cycle中有一個下降沿 ,這個下降沿出現的時刻可以用100 - low duration得到(100 - 75 = 25ns)

出現這種情況的原因是:選項-waveform要從上升沿開始

根據下面的例子,再次理解一下選項-waveform

#Figure (a)

create_clock -period 1.0 \\

-waveform {0.5 1.375} \\

[get_ports MAIN_CLK]

#Figure (b)

create_clock -period 1.2 \\

-waveform {0.3 0.4 0.8 1.0} \\

[get_ports JTAG_CLK]

對應的波形圖如下:

在這個例子中,圖(a)的分析方式與上一個例子相同

圖(b)由于選項-waveform中給出的上升沿和下降沿時刻都在第一個cycle時間范圍內,因此不需要進行額外的推斷

在某些情況下,比如在頂層的輸入端口或某些PLL的輸出端口,工具無法自動計算出過渡時間,此時在clock source出顯示指定過渡時間很有用,可以使用set_clock_transition來指定

set_clock_transition -rise 0.1 [get_clocks CLK_CONFIG]

set_clock_transition -fall 0.12 [get_clocks CLK_CONFIG]

# 這個約束僅適用于ideal clocks,一旦構建了時鐘樹就將其忽略

3 時鐘不確定度

可以用set_clock_uncertainty來指定時鐘周期的timing uncertainty,用不確定度來建模那些會降低有效時鐘周期的因素

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]

setup check會減少可用的有效時鐘周期

對于hold check,clock uncertainty被用作需要滿足的額外時序裕量

這里我的理解是,由于clock uncertainty的存在,減小了有效的時鐘周期,并且在clock uncertainty范圍內,我們無法預測clock是否有效,為了保證數據的正確性,在進行數據傳輸時,應當避開clock uncertainty的范圍

下面幾個command可以用來指定跨時鐘邊界path上的clock uncertainty,被稱為 inter-clock uncertainty

set_clock_uncertainty -from VIRTUAL-SYS_CLK -to SYSCLK -hold 0.05

set_clock_uncertainty -from VIRTUAL-SYS_CLK -to SYSCLK -setup 0.3

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

從圖中可以看到,該電路為兩個不同的clock domain SYS_CLK和CFG_CLK之間的path,根據上面約束可知,setup check的uncertainty是100ps,hold check的uncertainty是50ps

4 時鐘延遲

可以使用set_clock_latency來指定時鐘的延遲,用法如下:

set_clock_latency 1.8 -rise [get_clocks MAIN_CLK]

# MIN_CLK的上升沿延遲是1.8ns

set_clock_latency 2.1 -fall [all_clocks]

# 所有時鐘的下降沿延遲是2.1ns

# -rise和-fall指的是 時鐘在DFF的clock pin上的延遲

時鐘延遲有兩種:network latency和source latency

- network latency:從時鐘定義點(creat_clock)到DFF的clock pin上的延遲

- source latency:指的是從時鐘源到時鐘定義點的延遲

下圖直觀的展示了這兩個延遲類型的位置

以下是一些指定源延遲和網絡延遲的示例

# 沒有給出 -source 選項,表明是 network latency

# 沒有給出 -fall和-rise選項,表明fall和rise是相同的

# 沒有給出 -min和-max選項,表明min和max是相同的

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

set_clock_latency 0.851 -source -min [get_clocks CFG_CLK]

set_clock_latency 1.322 -source -max [get_clocks CFG_CLK]

一個重要的區別:

當clock tree建立后,network latency可以忽略,source latency不可以忽略

這是因為network latency的作用是在clock tree綜合之前用來估算clock tree上的latency,當clock tree綜合之后,我們可以計算出clock tree上的實際的latency,因此不在需要network latency

當clock tree綜合后,總的clock latency = source latency + clock tree上的實際latency

-

觸發器

+關注

關注

14文章

1996瀏覽量

61052 -

時鐘源

+關注

關注

0文章

93瀏覽量

15936 -

PLL電路

+關注

關注

0文章

92瀏覽量

6397 -

dff

+關注

關注

0文章

26瀏覽量

3400

發布評論請先 登錄

相關推薦

【小e物聯網試用體驗】+小e做為AP和STA

USART程序USATR_RX_STA為什么要定義成無符號字符型

MCU產生12MHz時鐘應用于ADC和STA339BW差異有多大?

Wifi的STA模式連接wifi的過程分享

STA7056.pdf

GD32F407的時鐘學習記錄

用CubeMX開發HAL學習記錄(一)

Harmony OS 設備開發學習記錄(十四)--Wifi的STA模式連接wifi

藍橋杯單片機學習過程記錄(八)時鐘芯片

藍橋杯單片機學習過程記錄(十四)第六屆溫度記錄

STM32 task3學習記錄

STA學習記錄-時鐘定義

STA學習記錄-時鐘定義

評論