在博客 DDR VIP 模型的無縫快速初始化中,我們討論了內存 VIP 模擬可以選擇快速完成重置和初始化過程并進入空閑狀態并開始讀取和寫入內存位置的重要性。我們提出了一種方法來實現這一點,即在完成重置和初始化所需的所有JEDEC標準步驟時縮小所需的時序。

在這篇博客中,我們將討論 Synopsys Memory VIP 如何允許完全跳過初始化,同時保持模型的正確行為。

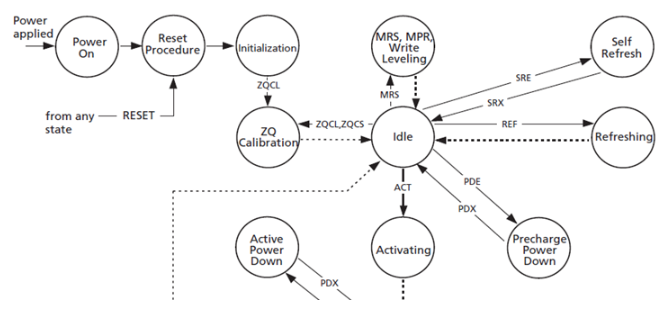

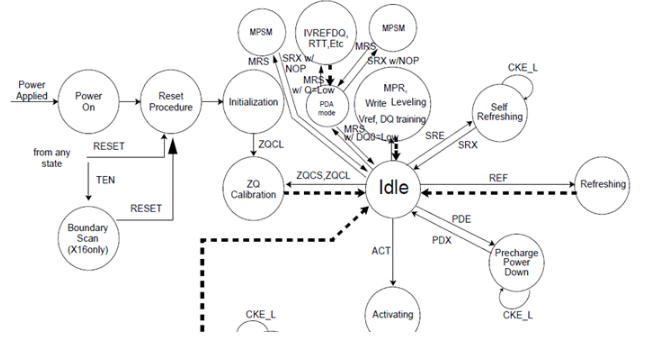

使用 Synopsys 內存 VIP 的 Skip 初始化功能可確保模型處于空閑狀態,從而繞過重置過程的要求。在該狀態下,VIP 已準備好接受 REF、MRS 和 ACT 等命令。允許的命令如圖 1 – DDR3 SDRAM JEDEC 標準 JESD79-3F 狀態圖和圖 2 – DDR4 SDRAM JEDEC 標準 JESD79-4 狀態圖所示。

圖 1 – DDR3 SDRAM JEDEC 標準 JESD79-3F 狀態圖

圖 2 – DDR4 SDRAM JEDEC 標準 JESD79-4 狀態圖

跳過初始化功能適用于 DDR3、DDR4。應該注意的是,使用skip init在后門設置后重置將清除所有設置并設置回默認值。

對于離散設備,我們可以使用以下方法將VIP設置為跳過初始化模式:

|

// dram_cfg is handle of class svt_ddr_confitugation dram_cfg.skip_init = 1 |

對于 DIMM 設備,我們可以使用以下步驟將 VIP 設置為跳過 DIMM 型號上的初始化序列:

|

// dimm_cfg is handle of svt_ddr_dimm_configuration and // configuring the skip_init setting for individual DRAM // configurations with DIMM structure foreach(dimm_cfg.data_lane_cfg[i]) begin foreach(dimm_cfg.data_lane_cfg[i].rank_cfg[j]) begin dimm_cfg.data_lane_cfg[i].rank_cfg[j].skip_init = 1; end end // Skip initialization setting for RCD component within an // RDIMM and LRDIMM dimm_cfg.ca_buffer_cfg.skip_init = 1; |

在通過config_db機制傳遞配置對象之前,應在構建階段完成離散和 DIMM 型號的跳過初始化設置。

此外,這些設置可以在構建階段之后完成,但用戶必須調用 reconfigure() 方法來更新模型中的設置。這必須在接口上執行任何命令之前完成。

以下是 reconfigure() 方法調用的語法:

|

// For Discrete Device Model env.mem_agent.reconfigure(dram_cfg); // For DIMM Model env.dimm_env.reconfigure(dimm_cfg); |

在隨后的博客中,我們將討論如何使用前門和后門訪問設置模式寄存器。

審核編輯:郭婷

-

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

DDR4

+關注

關注

12文章

320瀏覽量

40699 -

Ref

+關注

關注

0文章

19瀏覽量

27883

發布評論請先 登錄

相關推薦

6657的DDR3初始化不成功

如何從.mem文件初始化加密的ddr4內存模型?

初始化封裝

手機模塊初始化向導

ds1302時鐘芯片初始化,自動決定DS1302是否需要初始化程序

如何讓KeyStone DDR3接口初始化的詳細資料概述

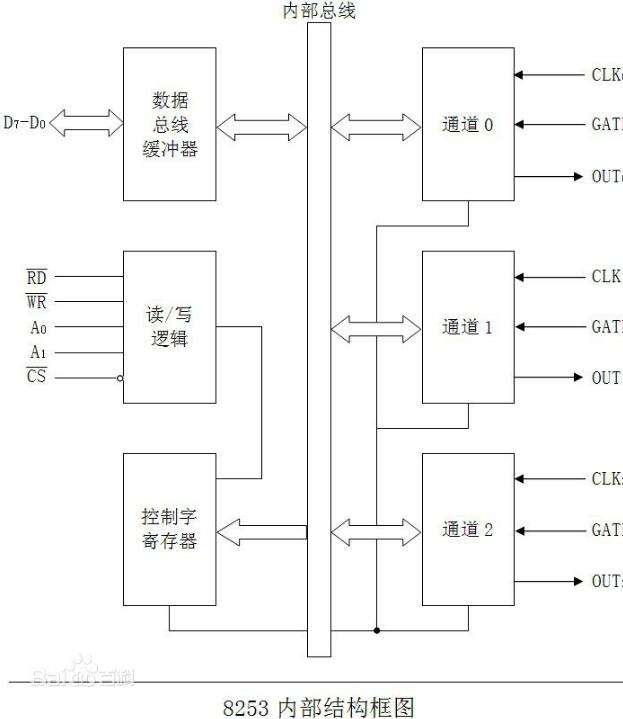

8253初始化程序分享_8253應用案例

在51平臺下初始化文件的引入導致全局變量無法初始化的問題如何解決

DDR VIP模型的無縫快速初始化

DDR4-初始化、訓練和校準

跳過DDR VIP模型的初始化

跳過DDR VIP模型的初始化

評論