眾所周知,在prePlace階段打完P(guān)ower后,需要使用APR工具把網(wǎng)表中存在的例化完的instance來(lái)全局放置在core內(nèi),這個(gè)布局階段(place)會(huì)暴露出設(shè)計(jì)Case在不加任何約束下按工具默認(rèn)的globaldensity等設(shè)置擺放cell所存在的風(fēng)險(xiǎn)。

實(shí)際上在后端范圍,工程師通常提到的高風(fēng)險(xiǎn)模塊指的就是congestion較高的模塊以及時(shí)序風(fēng)險(xiǎn)較高的模塊,這兩者實(shí)際上都和place有著千絲萬(wàn)縷的聯(lián)系,前者可能是因?yàn)閜lace階段不合理/面積切分不合理導(dǎo)致局部繞線資源緊張,后者則有可能因?yàn)閜lace的原因使得局部density過(guò)高導(dǎo)致timing eco階段hold插爆引起不能修的short drc。

這篇文章小編就來(lái)以APR placement flow為例,分析工具在place階段到底做了哪些事情,并且結(jié)合項(xiàng)目心得,講述幾種常見(jiàn)的解congestion的方法和思路。

實(shí)際上placement不止和route最后的drc結(jié)果息息相關(guān),更是和下個(gè)階段的cts時(shí)鐘樹(shù)密切相關(guān),一個(gè)優(yōu)秀的placement,擺的寄存器的位置比較合理/緊湊的話可以讓cts解drv的時(shí)候線長(zhǎng)減短,進(jìn)而減少很多為了解transition而插的INV,進(jìn)而一定程度上優(yōu)化時(shí)鐘樹(shù)長(zhǎng)和skew。

在數(shù)字電路中,單元的放置是很規(guī)范的,std cell的面積都是site的整數(shù)倍,而row是由site大小決定生成的,std cell也通常為一倍/二倍row高度,對(duì)應(yīng)的std cell也會(huì)snap到row上放置,其實(shí)從綜合工具DCG看初始狀態(tài)這些cell全部都是堆疊擺放的。而placement最重要的任務(wù),就是把這些cell擺好,不能有Overlap,不能有l(wèi)egalization的問(wèn)題,不能有FE DRC。這就很類似于一堆散亂的樂(lè)高積木,我們要把它一個(gè)個(gè)的在地上(core row)鋪好,但是又要擺放的符合前端代碼(RTL)關(guān)系。

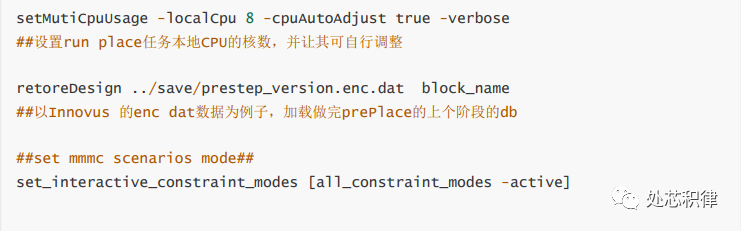

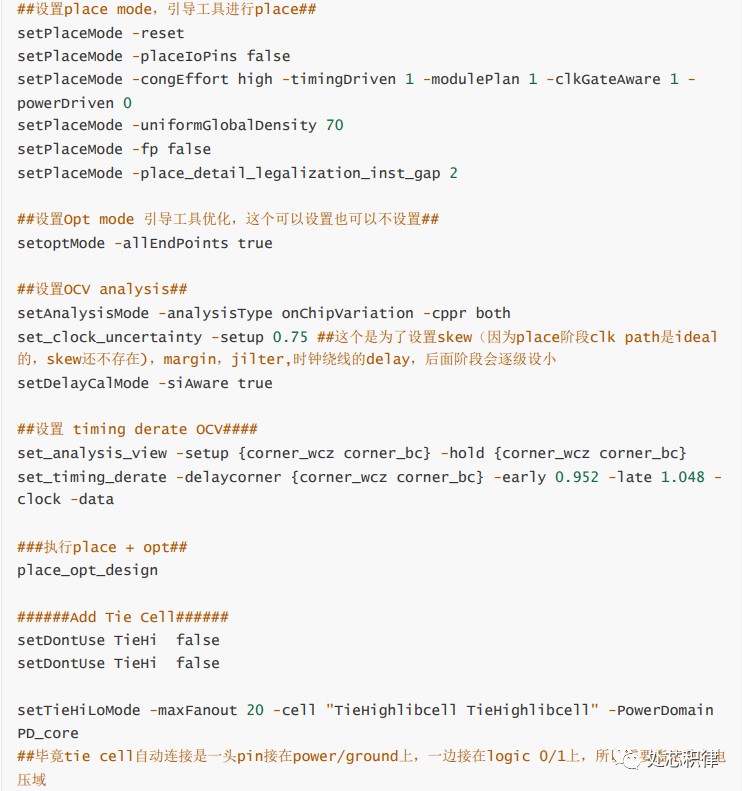

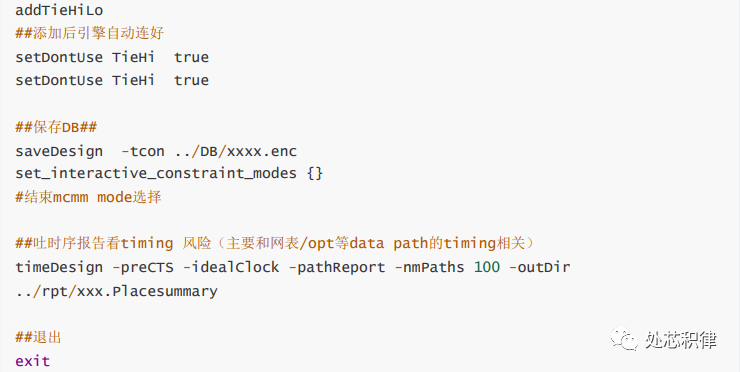

上述內(nèi)容就是指導(dǎo)innovus進(jìn)行block placement的基礎(chǔ)flow了,由注釋可以發(fā)現(xiàn)主要包括設(shè)置placemode;設(shè)置opt mode,設(shè)置OCV derate參數(shù)加嚴(yán)時(shí)序,add_tie_cell來(lái)鉗位住logic 0/1的Pin,一端接pg net,一端接constant pin;進(jìn)行Place以及Place_opt操作;存完db后,報(bào)timing以分析時(shí)序,也許有些ICer會(huì)疑惑PlaceOpt怎么就一個(gè)place_opt_design就一筆帶過(guò)了?事實(shí)上,APR布局布線的PlaceOpt階段工具是其中的一個(gè)重要步驟,主要負(fù)責(zé)對(duì)芯片的物理布局進(jìn)行優(yōu)化,以滿足電氣約束和布局規(guī)則。

PlaceOpt階段工具的主要作用如下:

優(yōu)化芯片的物理布局:PlaceOpt階段工具可以通過(guò)對(duì)芯片的物理布局進(jìn)行優(yōu)化,使得芯片的面積更小、功耗更低、性能更好。PlaceOpt階段工具會(huì)針對(duì)芯片的電氣約束和布局規(guī)則進(jìn)行優(yōu)化,以達(dá)到最佳的布局效果。

解決布局沖突:在布局布線的過(guò)程中,可能會(huì)出現(xiàn)布局沖突的情況,比如兩個(gè)器件之間的距離過(guò)近,或者某些器件之間的間距不符合規(guī)定等。PlaceOpt階段工具可以檢測(cè)這些沖突,并進(jìn)行解決,以保證芯片的物理布局符合規(guī)范。

優(yōu)化時(shí)序和功耗:PlaceOpt階段工具可以通過(guò)優(yōu)化芯片的物理布局,來(lái)改善芯片的時(shí)序和功耗。例如,可以通過(guò)減小器件之間的距離,來(lái)縮短信號(hào)傳輸?shù)臅r(shí)間,從而提高芯片的時(shí)序性能。又如,可以通過(guò)合理的布局,來(lái)降低芯片的功耗。

生成布局報(bào)告:PlaceOpt階段工具會(huì)生成布局報(bào)告,其中包括芯片的面積、功耗、時(shí)序等信息,以便設(shè)計(jì)人員對(duì)布局結(jié)果進(jìn)行評(píng)估和調(diào)整。

需要注意的是,PlaceOpt階段工具只是APR布局布線過(guò)程中的一個(gè)步驟,它需要與其他工具配合使用,才能完成整個(gè)布局布線的過(guò)程。例如,在PlaceOpt階段工具之后,還需要進(jìn)行時(shí)鐘樹(shù)合成、布局布線、后仿真等步驟,以完成芯片設(shè)計(jì)的整個(gè)流程。那么問(wèn)題來(lái)了,如果在place完畢后,工程師在查閱log/報(bào)告時(shí)候發(fā)現(xiàn)局部區(qū)域overflow(congestion)確實(shí)很大,存在很大的繞線風(fēng)險(xiǎn)時(shí)候一般怎么解決呢?

可以通過(guò)調(diào)整flooplan來(lái)解決,通常MEM的溝道/出PIN位置附近會(huì)有縱向/橫向的overflow,這種congestion通常可以通過(guò)調(diào)整溝道寬度/MeM的相對(duì)位置(使得走線規(guī)整)解決

打PlaceBlk,對(duì)于cell density過(guò)高的區(qū)域可以加partitial place blk來(lái)降低density,可以密度逐層遞增,打多層

增加keepout margin,通過(guò)設(shè)置Pin keep out來(lái)給PIN足夠空間出

打routing blk,對(duì)于Macro周邊底層signal如M2 M3等出PIN導(dǎo)致的signal overflow尤其是拐角處,在周邊區(qū)域走線資源充足的情況下,可以對(duì)堵塞區(qū)域設(shè)置對(duì)應(yīng)層的no_signal rblk,route完畢后刪掉,以免報(bào)drc錯(cuò)誤

設(shè)置padding,對(duì)于高Pin Density的區(qū)域,經(jīng)常有AIO,MUX,MBIT等多Pin std cell,雖然cell的密度不高,但是走線出Pin太多,這種情況可以通過(guò)設(shè)置一類lib cell的padding來(lái)解,通常可以加1~2site的距離,不夠再加,注意,這樣操作很有可能會(huì)影響timing,需要謹(jǐn)慎使用。

merge bit,對(duì)于寄存器導(dǎo)致發(fā)生overflow的區(qū)域,工程師可以設(shè)置Merge bit以減少時(shí)鐘PIN

修改RTL代碼,有可能是邏輯設(shè)計(jì)不合理,MUX等多PIN邏輯太多了,后端確實(shí)解不了

修改Power Plan,對(duì)于H overflow,則加密縱向走線,放松橫向Power走線,反之加密橫向Power走線,放松縱向Power走線

規(guī)劃std cell,整理signal 線,在Power net高層空間允許的情況下,走高層NDR來(lái)釋放風(fēng)險(xiǎn)

少部分的signal線,可以自己手動(dòng)拉線走高層/或者換層

最終殺招,和項(xiàng)目經(jīng)理商量要不要增加點(diǎn)面積,或者砍點(diǎn)macro放到其他模塊去,H overflow就增加高度,V overflow就增加寬度。

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5317瀏覽量

120010 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59706 -

apr

+關(guān)注

關(guān)注

0文章

11瀏覽量

6468 -

MEM

+關(guān)注

關(guān)注

0文章

6瀏覽量

8451 -

DCG

+關(guān)注

關(guān)注

0文章

7瀏覽量

2363

原文標(biāo)題:基于方法學(xué)flow來(lái)聊聊APR工具placement

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于方法學(xué)flow來(lái)聊聊APR工具placement

基于方法學(xué)flow來(lái)聊聊APR工具placement

評(píng)論