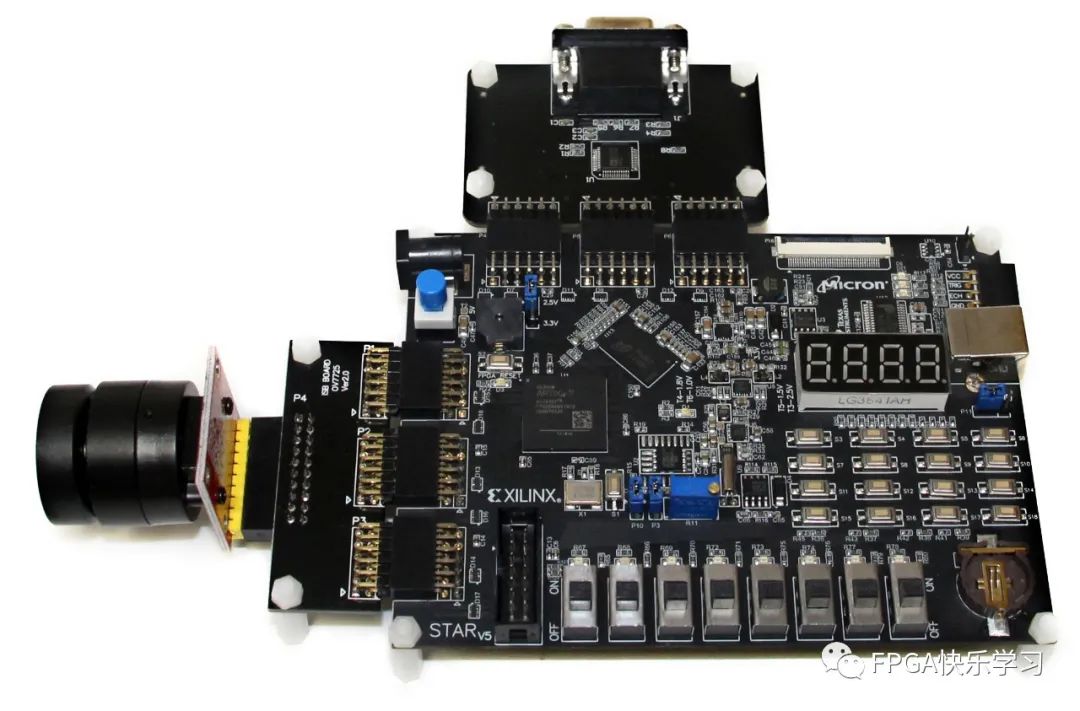

圖1 實驗平臺

視頻內容:

Lesson38圖像傳感器介紹與設計架構(本節視頻)

Lesson39時鐘拓撲、PLL配置與例化

● 圖像采集顯示設計架構的回顧

● 設計中各個模塊的時鐘頻率定義

● PLL的輸入輸出時鐘信號拓撲圖

●Vivado中PLL IP的配置和添加

●PLL IP的仿真驗證

Lesson40 FIFO的配置與使用

Lesson41圖像傳輸接口時序與在線調試

Lesson42圖像采集模塊代碼設計

Lesson43圖像采集模塊仿真驗證

Lesson44可變位寬的FIFO配置與仿真

Lesson45 DDR3 IP接口說明與地址映射

Lesson46 DDR3緩存模塊寫控制設計

Lesson47 DDR3緩存模塊仿真平臺構建

Lesson48 DDR3緩存模塊讀控制設計

Lesson49 DDR3緩存模塊集成仿真

Lesson50 VGA顯示驅動模塊代碼設計

Lesson51 VGA顯示驅動模塊仿真驗證

PLL定義

PLL(Phase Locked Loop):為鎖相回路或鎖相環,用來統一整合時脈訊號,使內存能正確的存取資料。PLL用于振蕩器中的反饋技術。許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。

而我們在這里所說的PLL,沒有上面一段定義那么晦澀難懂,大家記住PLL一個最主要的功能,即能夠對輸入的基準時鐘信號進行一定范圍內的分頻或者倍頻,從而產生多個輸出時鐘信號供芯片內部的各個功能模塊使用。

多時鐘設計

在FPGA的實際工程設計中,很難以一個特定的時鐘頻率打天下。由于FPGA具備豐富的接口協議,能以應對各種不同外設所需要的或高速、或低速、或差分、或單端、電平或高或低等不同接口。那么,要在這些外設之間游刃有余,平穩過度,就需要產生各種不同的時鐘頻率和提供跨時鐘域的數據通信能力。這些,對于FPGA來說都是再基本不過的功能了。

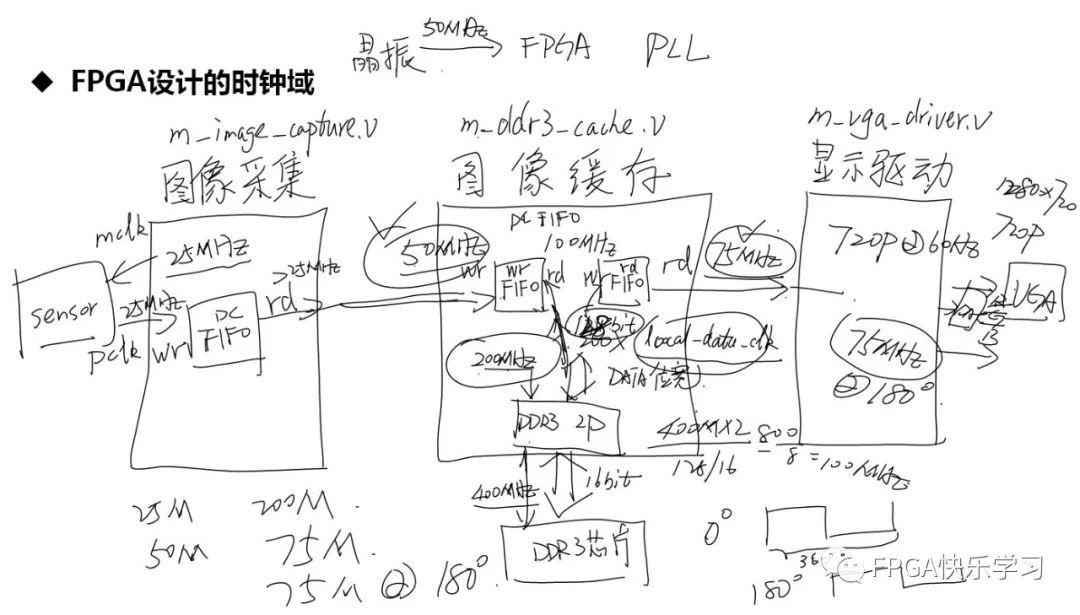

以圖像采集和顯示設計為例,FPGA外接的圖像傳感器需要25MHz的時鐘,而返回的有效數據也是以同樣的同頻不同相的時鐘進行同步;在FPGA內部為了更好的達到時序收斂和性能水平,需要一個更穩定和能以滿足處理需要的的時鐘頻率(如本設計的50MHz);接著是圖像的緩存,其數據的同步時鐘是由DDR3控制器IP給出的100MHz的時鐘,而在此之前,需要有一個200MHz的時鐘作為DDR3控制器IP的輸入;最后的顯示驅動,720p的分辨率,要達到60Hz的顯示刷新率,就需要75MHz的時鐘。這么一看,就這么個不大的設計,涉及的時鐘頻率還真不少。

圖2

時鐘的定義和分配,可以說是由設計的各個外設和設計本身的處理性能需要共同決定的,那么我們這個設計中又是如何進行具體的定義、分配、產生呢?歡迎進入我們的視頻課程進行深入的學習!

審核編輯:湯梓紅

-

傳感器

+關注

關注

2548文章

50740瀏覽量

752147 -

圖像采集

+關注

關注

2文章

299瀏覽量

41257 -

pll

+關注

關注

6文章

775瀏覽量

135054 -

Verilog

+關注

關注

28文章

1345瀏覽量

109996 -

時鐘

+關注

關注

10文章

1721瀏覽量

131378

原文標題:Verilog邊碼邊學 Lesson39 圖像采集與顯示設計之PLL配置與例化【免費視頻】

文章出處:【微信號:FPGA快樂學習,微信公眾號:FPGA快樂學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog邊碼邊學Lesson:圖像采集與顯示設計之PLL配置與例化

Verilog邊碼邊學Lesson:圖像采集與顯示設計之PLL配置與例化

評論