電容在高速 PCB 設計中起著重要的作用,通常也是 PCB 上用得最多的器件。在 PCB 中,電容通常分為濾波電容、去耦電容、儲能電容等。

1 電源輸出電容,濾波電容

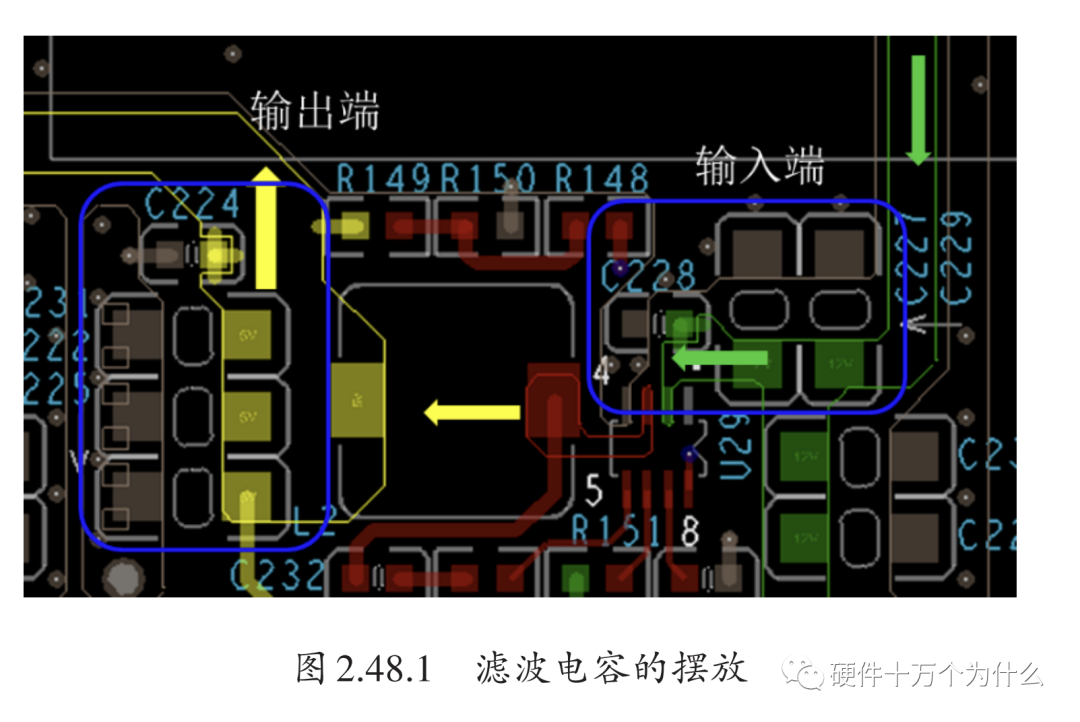

我們通常把電源模塊輸入、輸出回路的電容稱為濾波電容。簡單理解就是,保證輸入、輸出電源穩定的電容。在電源模塊中,濾波電容擺放的原則是“先大后小”。如圖2.48.1所示,濾波電容按箭頭方向先大后小擺放。

電源設計時,要注意走線和銅皮足夠寬、過孔數量足夠多,保證通流能力滿足需求。寬度和過孔數量結合電流大小來評估。

電源輸入電容

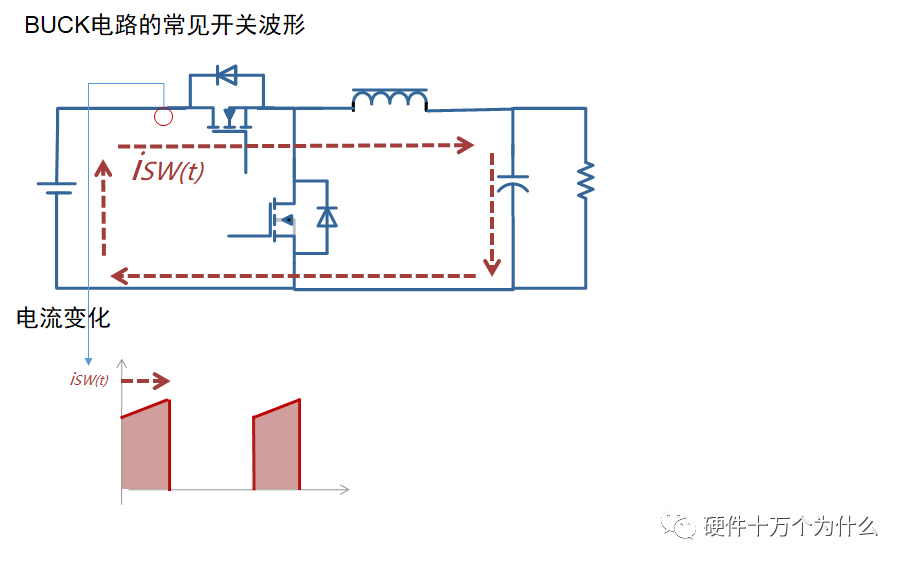

電源輸入電容與開關環路形成一個電流環。這個電流環路的變化幅度大,Iout的幅度。頻率是開關頻率。DCDC芯片開關過程中產生,這個電流環產生的電流的變化,包含了較快的di/dt。

同步BUCK的方式,續流路徑要經過芯片的GND管腳,輸入電容要接在芯片的GND和Vin之間,路徑竟可能的短粗。

這個電流環面積足夠的小,這個電流環對外輻射就會越好。

2 去耦電容

高速 IC的電源引腳需要足夠多的去耦電容,最好能保證每個引腳有一個。實際設計中,如果沒有空間擺放去耦電容,則可以酌情刪減。

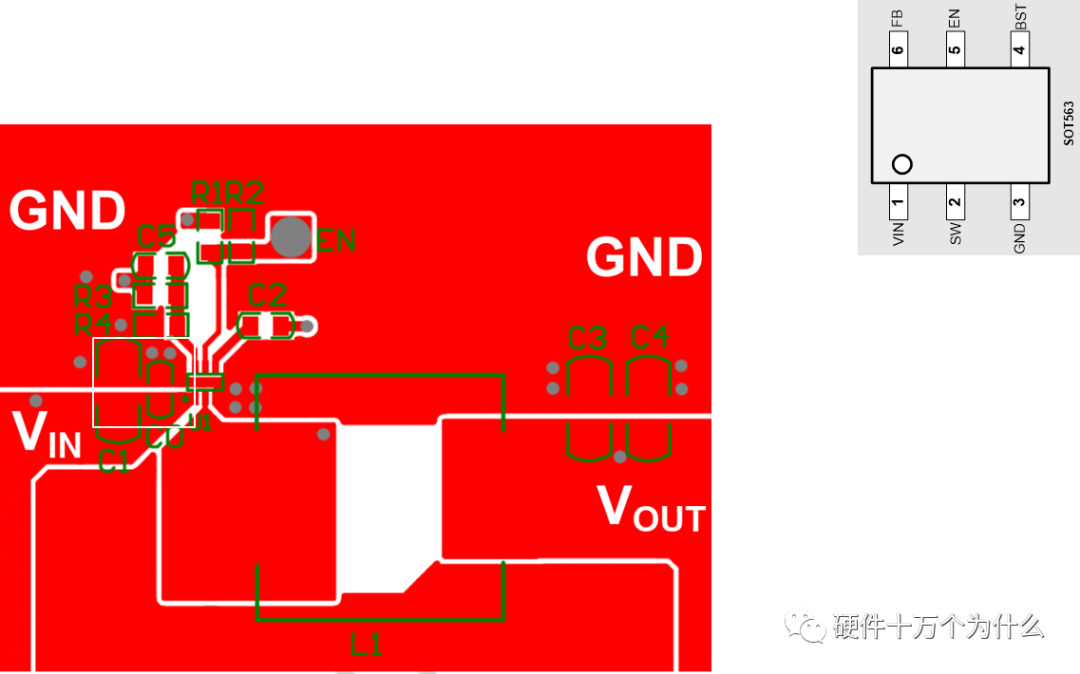

IC 電源引腳的去耦電容的容值通常會比較小,如 0.1μF、0.01μF 等;對應的封裝也比較小,如0402封裝、0603封裝等。在擺放去耦電容時,應注意以下幾點。

(1)盡可能靠近電源引腳放置,否則可能起不到去耦作用。理論上講,電容有一定的去耦半徑范圍,所以應嚴格執行就近原則。

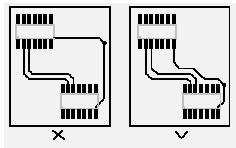

(2)去耦電容到電源引腳引線盡量短,而且引線要加粗,通常線寬為8~15mil(1mil = 0.0254mm)。加粗目的在于減小引線電感,保證電源性能。

(3)去耦電容的電源、地引腳從焊盤引出線后,就近打孔,連接到電源、地平面上。該引線同樣要加粗,過孔盡量用大孔,如能用孔徑10mil 的孔,就不用8mil的孔。

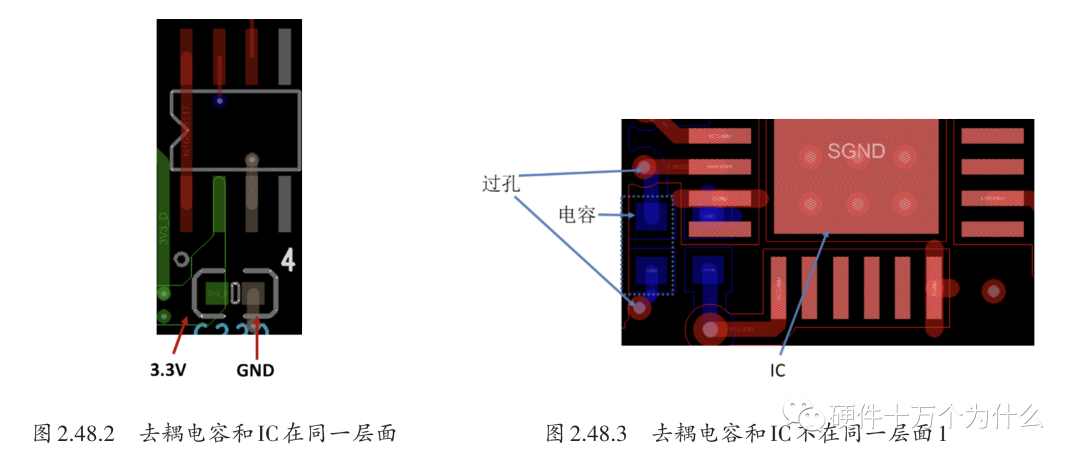

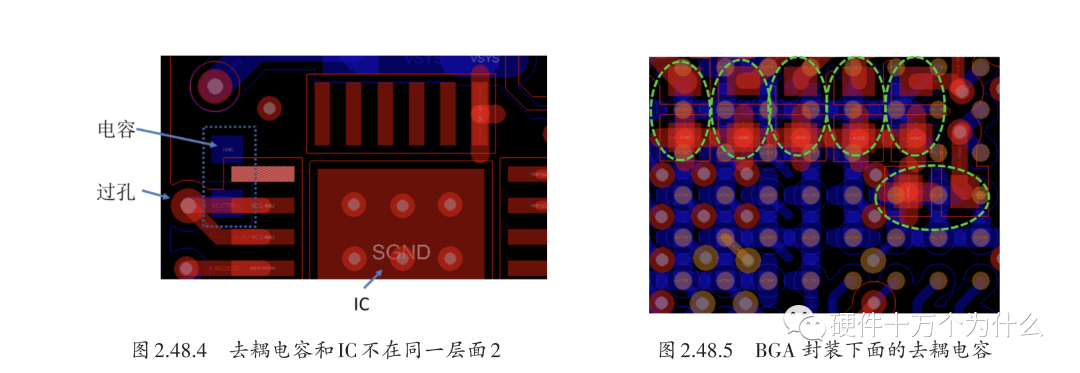

(4)保證去耦環路盡量小。去耦電容常見的擺放示例如圖2.48.2~圖2.48.4所示。圖2.48.2~圖2.48.4所示是SOP封裝的IC去耦電容的擺放方式,QFP等封裝的與此類似。

常見的 BGA封裝,其去耦電容通常放在 BGA下面,即背面。由于 BGA 封裝引腳密度大,因此去耦電容一般放的不是很多,但應盡量多擺放一些,如圖2.48.5所示。

3、儲能電容

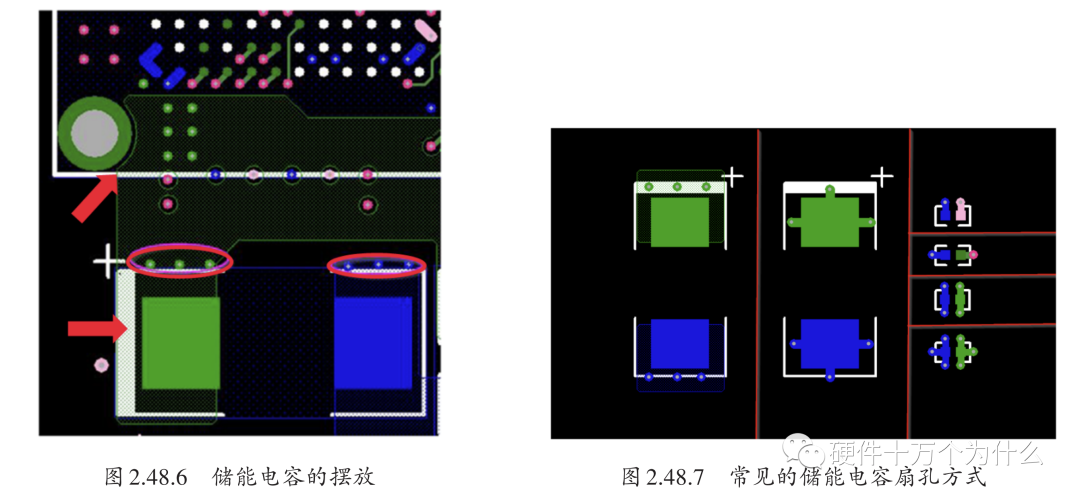

儲能電容的作用就是保證IC在用電時,能在最短的時間內提供電能。儲能電容的容值一般比較大,對應的封裝也比較大。在PCB中,儲能電容可以離器件遠一些,但也不能太遠,如圖2.48.6所示。常見的儲能電容扇孔方式,如圖2.48.7所示。

電容扇孔、扇線原則如下。

(1)引線盡量短且加粗,這樣有較小的寄生電感。

(2)對于儲能電容,或者過電流比較大的器件,打孔時應盡量多打幾個。

(3)當然,電氣性能最好的扇孔是盤中孔。實際需要綜合考慮

審核編輯:湯梓紅

-

pcb

+關注

關注

4317文章

23004瀏覽量

396247 -

濾波電容

+關注

關注

8文章

457瀏覽量

39987 -

PCB設計

+關注

關注

394文章

4670瀏覽量

85281 -

去耦電容

+關注

關注

11文章

315瀏覽量

22309 -

儲能電容

+關注

關注

0文章

14瀏覽量

6001

原文標題:PCB設計時電容如何擺放?

文章出處:【微信號:PCB電子電路技術,微信公眾號:PCB電子電路技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB設計時如何擺放元器件?

PCB設計中絲印的要求及擺放

高速PCB設計系列基礎知識66 | PCB設計中絲印的要求及擺放

濾波電路的PCB設計注意事項

電容在高速PCB設計中該如何擺放呢?

如何進行電源模塊的PCB設計?

PCB設計時電容如何擺放?

PCB設計時電容如何擺放?

評論