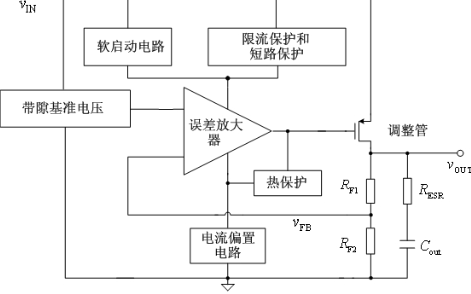

模擬集成電路包括運(yùn)算放大器、濾波器、電源管理電路、模擬開關(guān)、PLL、射頻前端等,其典型參數(shù)包括泄漏電流、基準(zhǔn)電壓、阻抗、增益、靈敏度、紋波抑制、頻率或相位響應(yīng)、諧波、互調(diào)失真、串?dāng)_、信噪比、噪聲系數(shù)等。

與數(shù)字集成電路相比,模擬集成電路中的晶體管較少,其參數(shù)范圃是連續(xù)的,缺之良好的故障模型,不存在可拆分的子電路,測試儀器儀表的引腳負(fù)載、接口阻抗、噪聲等均會導(dǎo)致測量誤差,因此模擬集成電路的測試更加困難。

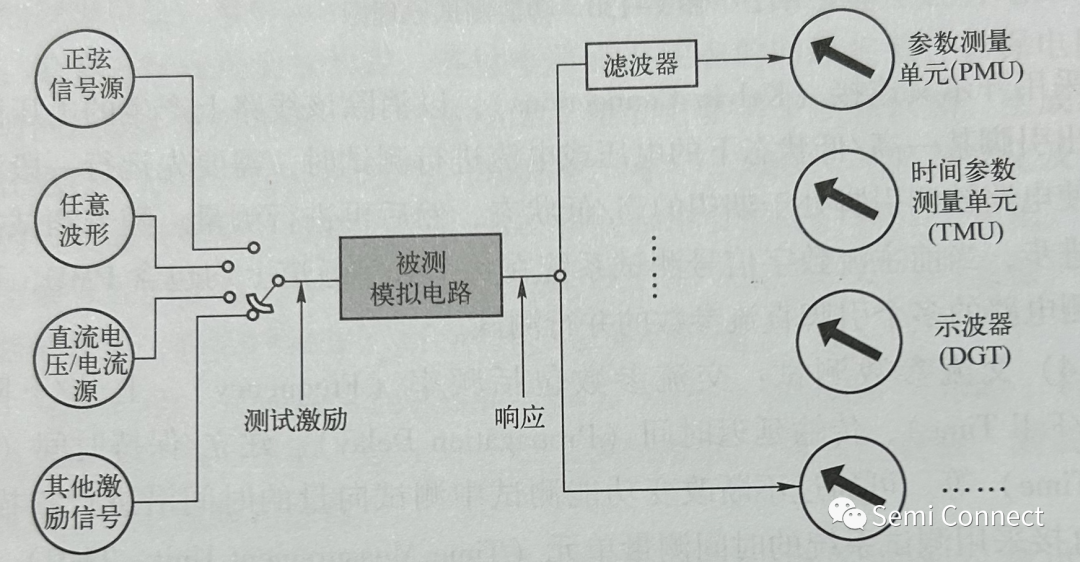

下圖所示的是基于功能的模擬集成電路測試方法,該方法不需要故障模型,便于處理。由于模擬集成電路缺三良好的故障模型,且結(jié)構(gòu)模擬故障與功能映射并不理想,因此模擬集成電路結(jié)構(gòu)測試方法尚未得到廣泛應(yīng)用。

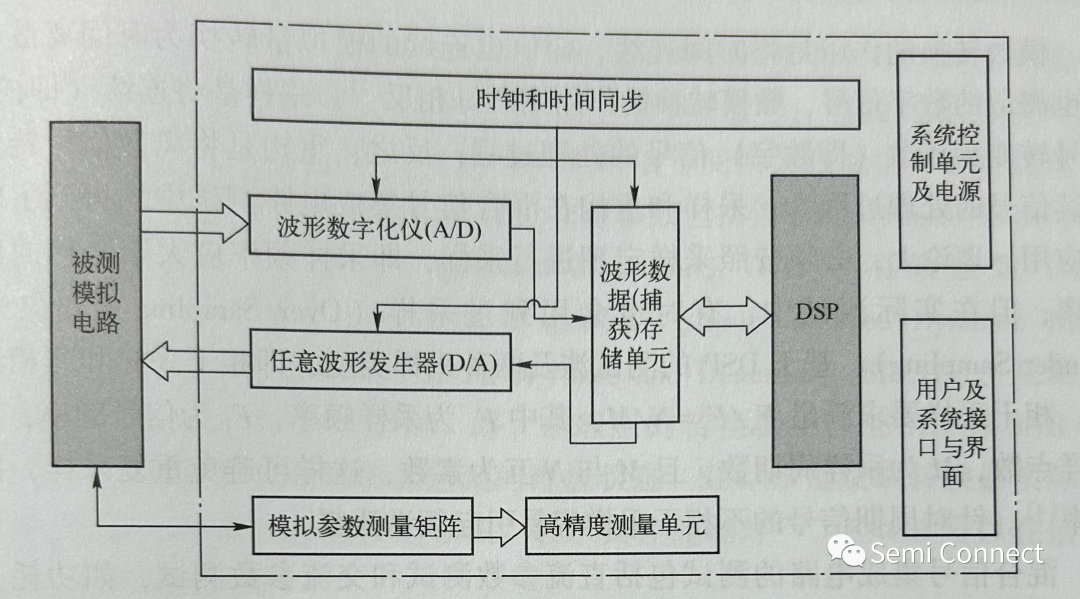

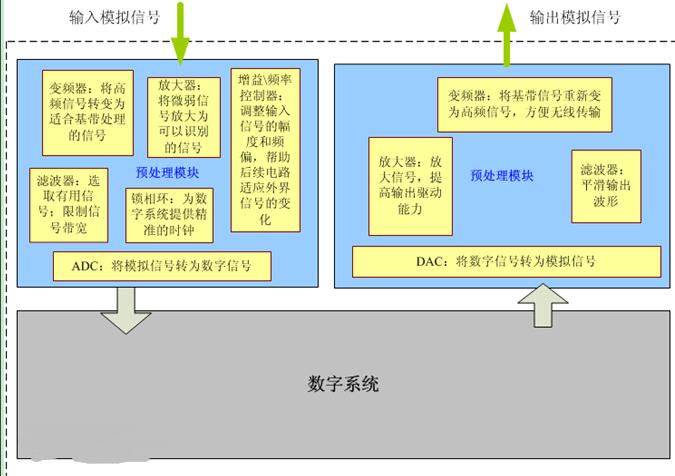

傳統(tǒng)的模擬集成電路測試方法存在參數(shù)多,測試時(shí)間長,激勵與響應(yīng)很難同步,噪聲處理復(fù)雜等問題。隨著技術(shù)的進(jìn)步和軟硬件成本的降低,基于數(shù)宇信號處理器(DSP)的功能測試方法得以廣泛應(yīng)用。下圖所示的是基于DSP 的模擬集成電路測試架構(gòu)圖,其校心部件是任意波形發(fā)生器、波形數(shù)字化儀和 DSP。

基于DSP 的測試方法將模擬信號數(shù)字化,使得儀器串?dāng)_、噪聲、漂移大大減少;同時(shí),利用多次數(shù)字化采樣,提高了測試精度,重復(fù)性更好,是一種更佳的測試方案。但是,如果測試參數(shù)單一,其測試成本比傳統(tǒng)的高。

模擬集成電路的 DFT 和內(nèi)建自測試(BIST)設(shè)計(jì)比較滯后。IEEE 1149.4提出了一種針對模擬集成電路擴(kuò)充的邊界掃描方法,但目前尚無業(yè)界認(rèn)可的模擬信號性能測試的可行的方案。在模擬信號 BIST 領(lǐng)域,需要投人更多的精力進(jìn)行研究,以降低對高性能復(fù)雜模擬自動測試系統(tǒng)(ATE)的需求。

審核編輯:湯梓紅

-

集成電路

+關(guān)注

關(guān)注

5367文章

11168瀏覽量

358440 -

濾波器

+關(guān)注

關(guān)注

158文章

7598瀏覽量

176616 -

運(yùn)算放大器

+關(guān)注

關(guān)注

213文章

4816瀏覽量

171742 -

pll

+關(guān)注

關(guān)注

6文章

767瀏覽量

134861 -

DFT

+關(guān)注

關(guān)注

2文章

224瀏覽量

22609

原文標(biāo)題:模拉集成電路測試,類比積體電路測試, Analog IC Test

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

模擬集成電路原理與應(yīng)用

模擬集成電路基礎(chǔ)與應(yīng)用

模擬集成電路,模擬集成電路是什么意思

模擬集成電路與系統(tǒng)圖書

模擬集成電路_模擬集成電路圖書

模擬集成電路是什么

模擬集成電路設(shè)計(jì)與仿真電子版下載

模擬集成電路測試方法

模擬集成電路測試方法

評論