隨著摩爾定律的失效,芯片集成度的提高遇到了困難。英特爾(Intel)創始人之一戈登·摩爾(Gordon Moore)于上世紀60年代提出,芯片集成度每18-24個月就會翻一番,性能也會提升一倍,這被稱為摩爾定律。我們可以將摩爾定律比作一輛不斷升級的汽車。每個18到24個月,這輛汽車就會升級換代,增加更多的功能和性能。比如,引擎會變得更強大,車身會更加輕便,空氣動力學也會更加優化,使得這輛汽車更加高效和安全。同時,這輛汽車的制造成本也在不斷降低,使得更多的人們能夠擁有它。

隨著晶體管尺寸的不斷縮小,到了14/7納米以下,芯片制造面臨著一系列問題。第一是散熱的問題,由于晶體管尺寸的縮小,芯片的尺寸也變得越來越小,這導致芯片內部的熱量密度增加。同時,芯片內部的電路也變得更加復雜,這使得散熱問題更加困難。因此,需要更高效的散熱技術來避免芯片過熱導致性能下降甚至損壞,例如通過優化晶體管布局和材料選擇來降低功耗和熱量產生。

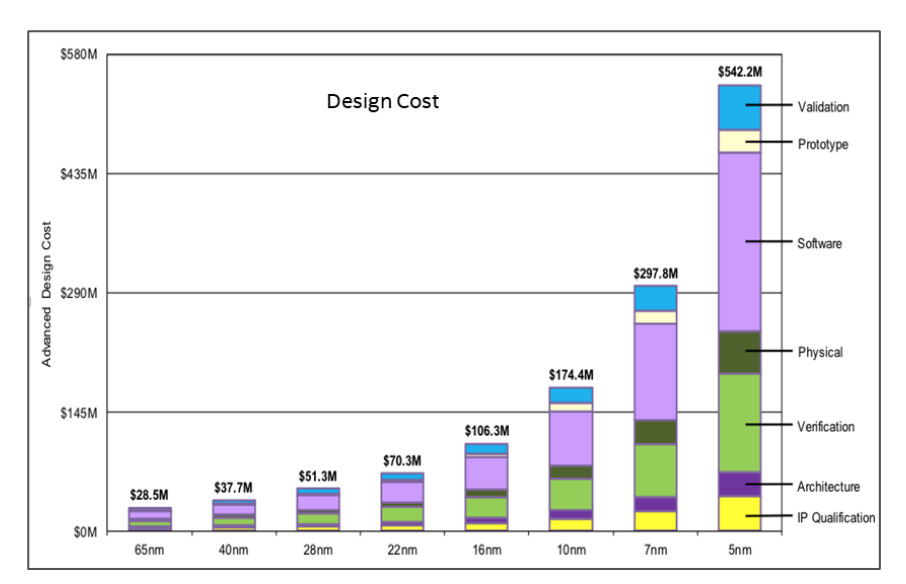

另外,芯片制造還面臨著良率問題。在芯片制造過程中,晶體管數量的增加和密集度的提高會增加芯片出現問題的概率。即使只有一個晶體管出現問題,整個芯片也可能無法正常工作。這會導致制造商的成本增加。據統計,制造65nm芯片的成本為2850萬美元,而制造7nm的成本則需要近3億美元,而到了5nm,這個成本還需要再次翻倍。此外,芯片制造的良率也受到晶圓大小的影響,晶圓越大,晶體管密度增加,晶圓上的芯片數量越多,良率也越低。因此,需要進行嚴格的測試來確保芯片的質量和可靠性。隨著芯片的集成度和復雜度的不斷提高,芯片制造的難度和成本不斷增加,因此芯片的良率和測試也變得越來越重要。

這些問題使得制造商難以繼續遵循摩爾定律的速度提高芯片的集成度和性能,因此需要采用新技術和新方法來解決這些問題。

不同工藝節點下的設計成本

(Source: IBS, as cited in IEEE Heterogeneous Integration Roadmap)

在后摩爾時代,Chiplet技術成為了重要的解決方案。Chiplet技術可以將不同或相同功能的芯片集成在一起,實現更高的計算和處理能力,同時也可以提高芯片的良率,并降低成本和風險。Chiplet技術的優勢之一是可以將不同制造工藝的芯片集成在一起。舉例來說,如果需要高性能的CPU和GPU,可以選擇使用5納米或3納米的工藝來制造,而對于一些IO和power等電路,可以使用成熟的工藝來制造,以降低成本和風險。這種做法的好處在于可以根據不同的需求選擇不同的工藝,從而提高芯片的性能和靈活性,同時也可以降低成本和風險。

然而,Chiplet的發展面臨著一個重要的瓶頸,即互連問題。

為了實現不同芯片之間高速、可靠互連,以實現數據傳輸和共享,Chiplet技術中采用了PCIe、BOW等接口標準。然而,這些標準并不是專為Chiplet設計的,或未定義完整的協議及封裝等標準。這導致了芯片制造商之間的互操作性問題,限制了Chiplet技術的發展和應用。為了解決這個問題,通用Chiplet互聯技術UCIe(Universal Chiplet Interconnect Express)標準應運而生。

UCIe是一個開放的行業互連標準,旨在為芯片制造商提供一種通用的芯片互連標準,以降低芯片互連的成本和風險,并促進Chiplet技術的生態系統拓張和推廣。UCIe標準可以實現小芯片之間的封裝級互連,具有高帶寬、低延遲、經濟節能的優點。該標準定義了完整的協議和封裝,可以支持高速、可靠的芯片互連,并提供了靈活的拓撲結構和配置選項,以滿足不同應用場景的需求。UCIe標準的開放性和通用性使得它可以被廣泛應用于各種不同的計算領域,包括云端、邊緣端、企業、5G、汽車、高性能計算和移動設備等,以滿足對算力、內存、存儲和互連不斷增長的需求。通過采用UCIe標準,芯片制造商可以實現更高的計算和處理能力,同時也可以降低芯片制造的成本和風險。

UCIe標準是一種通用的芯片互連標準,其主要特點包括高帶寬和低延遲、靈活性和可擴展性、可靠性以及生態系統完整性。高帶寬和低延遲可以提高芯片的性能和效率,使其能夠更好地滿足不同應用場景的需求。靈活性和可擴展性可以支持不同的拓撲結構和配置選項,以滿足不同應用場景的需求。可靠性可以確保芯片互連的可靠性和穩定性,從而提高芯片的可靠性和穩定性。生態系統完整性可以促進芯片制造商之間的合作和互操作性,推動其推廣和普及。

UCIe標準是芯片設計和產業發展的一大亮點,它將為Chiplet的發展和應用帶來更多的創新和機遇。未來,我們可以期待UCIe標準在數據中心、人工智能、云計算等領域發揮更加重要的作用,為我們的生活帶來更多的便利和創新。

芯耀輝作為中國接口IP領軍企業,于Chiplet早期就開始研究和開發相關技術,后又作為首批IP供應商于2022年4月加入UCIe組織,并率先推出了完整的Chiplet D2D解決方案,包括物理層、控制器和封裝,能夠更好地滿足不同行業和應用的需求。同時,芯耀輝積極參與了中國首個原生Chiplet標準的制定,該標準由中國集成電路領域相關企業和專家共同主導,由工信部中國電子工業標準化技術協會于2022年12月審核發布。芯耀輝作為重點貢獻企業,積極參與該標準的制定,為推動Chiplet的發展和應用作出了突出貢獻。

此中國首個原生Chiplet標準,既定義了并口,也定義了串口,其協議層的自定義數據包格式與UCIe保持兼容,且在封裝上的標準主要采用國內可實現的技術,可直接使用國內已有生態開發及落地Chiplet技術。所以,芯耀輝的參與和貢獻加速了UCIe標準的推廣和應用,還為后摩爾時代的芯片設計提供了一個完整的、可落地的Chiplet解決方案。隨著技術的不斷發展和創新,Chiplet將會在數據中心、人工智能、云計算等領域扮演越來越重要的角色。我們相信,有了UCIe標準的支持和芯耀輝等企業的積極參與,Chiplet將會迎來更加廣闊的發展前景。Chiplet技術的不斷發展和創新將為推動數字經濟和智能化社會的發展作出更大的貢獻。

審核編輯:湯梓紅

-

芯片

+關注

關注

450文章

49636瀏覽量

417158 -

摩爾定律

+關注

關注

4文章

630瀏覽量

78769 -

晶體管

+關注

關注

77文章

9502瀏覽量

136935 -

chiplet

+關注

關注

6文章

404瀏覽量

12513 -

UCIe

+關注

關注

0文章

42瀏覽量

1596

原文標題:芯科普丨UCIe 為后摩爾時代帶來什么?

文章出處:【微信號:AkroStar-Tech,微信公眾號:芯耀輝科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

根據“后摩爾時代”芯片行業如何發展?

IC在后摩爾時代的挑戰和機遇

后摩爾定律時代的骨干網挑戰

后摩爾時代集成電路產業特性及發展趨勢

吳漢明以《后摩爾時代的芯片挑戰和機遇》發表了演講

重磅演講:持續推進摩爾時代的IC設計藝術

聚焦后摩爾時代,后摩爾時代集成電路產業如何突破

如何調節后摩爾時代的架構計算之爭

普萊信智能孟晉輝出席CSPT 2022,共探后摩爾時代的封裝技術

后摩爾時代,十大EDA驗證技術趨勢展望

后摩爾時代,十大EDA驗證技術趨勢展望

重磅:Keysight官宣加入UCIe聯盟

后摩爾時代,從有源相控陣天線走向天線陣列微系統

SiP封裝技術將制霸“后摩爾時代”?利爾達首款SiP模組應運而生!

UCIe為后摩爾時代帶來什么?

UCIe為后摩爾時代帶來什么?

評論