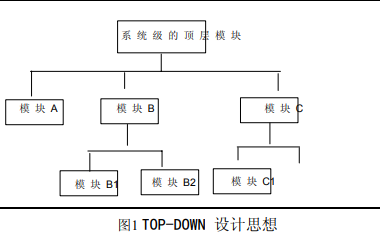

設(shè)計方法

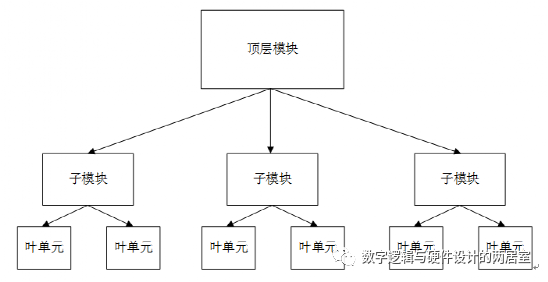

Verilog 的設(shè)計多采用自上而下的設(shè)計方法(top-down)。即先定義頂層模塊功能,進而分析要構(gòu)成頂層模塊的必要子模塊;然后進一步對各個模塊進行分解、設(shè)計,直到到達無法進一步分解的底層功能塊。這樣,可以把一個較大的系統(tǒng),細(xì)化成多個小系統(tǒng),從時間、工作量上分配給更多的人員去設(shè)計,從而提高了設(shè)計速度,縮短了開發(fā)周期。

設(shè)計流程

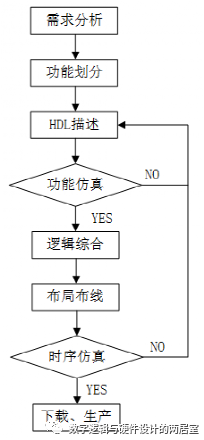

Verilog 的設(shè)計流程,一般包括以下幾個步驟:

◆需求分析:

工作人員需要對用戶提出的功能要求進行分析理解,做出電路系統(tǒng)的整體規(guī)劃,形成詳細(xì)的技術(shù)指標(biāo),確定初步方案。例如,要設(shè)計一個電子屏,需要考慮供電方式、工作頻率、產(chǎn)品體積、成本、功耗等,電路實現(xiàn)采用 ASIC 還是選用 FPGA/CPLD 器件等。

◆功能劃分

正確地分析了用戶的電路需求后,就可以進行邏輯功能的總體設(shè)計,設(shè)計整個電路的功能、接口和總體結(jié)構(gòu),考慮功能模塊的劃分和設(shè)計思路,各子模塊的接口和時序(包括接口時序和內(nèi)部信號的時序)等,向項目組成員合理分配子模塊設(shè)計任務(wù)。

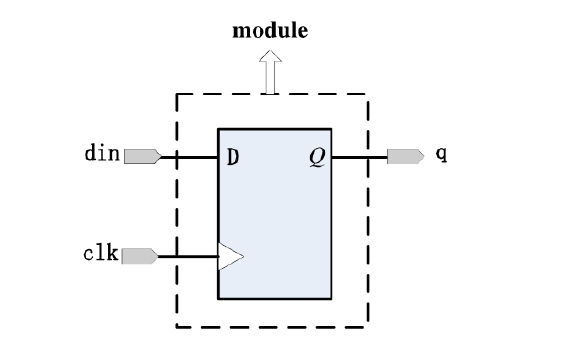

◆文本描述:

可以用任意的文本編輯器,也可以用專用的 HDL 編輯環(huán)境,對所需求的數(shù)字電路進行設(shè)計建模,保存為 .v 文件。

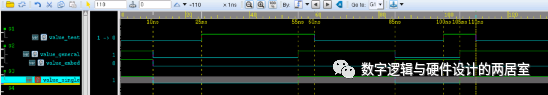

◆功能仿真(前仿真):

對建模文件進行編譯,對模型電路進行功能上的仿真驗證,查找設(shè)計的錯誤并修正。

此時的仿真驗證并沒有考慮到信號的延遲等一些 timing 因素,只是驗證邏輯上的正確性。

◆邏輯綜合:

綜合(synthesize),就是在標(biāo)準(zhǔn)單元庫和特定的設(shè)計約束的基礎(chǔ)上,將設(shè)計的高層次描述(Verilog 建模)轉(zhuǎn)換為門級網(wǎng)表的過程。邏輯綜合的目的是產(chǎn)生物理電路門級結(jié)構(gòu),并在邏輯、時序上進行一定程度的優(yōu)化,尋求邏輯、面積、功耗的平衡,增強電路的可測試性。

但不是所有的 Verilog 語句都是可以綜合成邏輯單元的,例如時延語句。

◆布局布線:

根據(jù)邏輯綜合出的網(wǎng)表與約束文件,利用廠家提供的各種基本標(biāo)準(zhǔn)單元庫,對門級電路進行布局布線。至此,已經(jīng)將 Verilog 設(shè)計的數(shù)字電路,設(shè)計成由標(biāo)準(zhǔn)單元庫組成的數(shù)字電路。

◆時序仿真(后仿真)

布局布線后,電路模型中已經(jīng)包含了時延信息。利用在布局布線中獲得的精確參數(shù),用仿真軟件驗證電路的時序。單元器件的不同、布局布線方案都會給電路的時序造成影響,嚴(yán)重時會出現(xiàn)錯誤。出錯后可能就需要重新修改 RTL(寄存器傳輸級描述,即 Verilog 初版描述),重復(fù)后面的步驟。這樣的過程可能反復(fù)多次,直至錯誤完全排除。

◆FPGA/CPLD 下載或 ASIC 制造工藝生產(chǎn)

完成上面所有步驟后,就可以通過開發(fā)工具將設(shè)計的數(shù)字電路目標(biāo)文件下載到 FPGA/CPLD 芯片中,然后在電路板上進行調(diào)試、驗證。

如果要在 ASIC 上實現(xiàn),則需要制造芯片。一般芯片制造時,也需要先在 FPGA 板卡上進行邏輯功能的驗證。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21669瀏覽量

601869 -

寄存器

+關(guān)注

關(guān)注

31文章

5317瀏覽量

120015 -

Verilog

+關(guān)注

關(guān)注

28文章

1344瀏覽量

109986 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59706 -

CPLD芯片

+關(guān)注

關(guān)注

0文章

18瀏覽量

11620

發(fā)布評論請先 登錄

相關(guān)推薦

Verilog HDL華為入門教程

Verilog HDL入門教程(華為絕密資料)

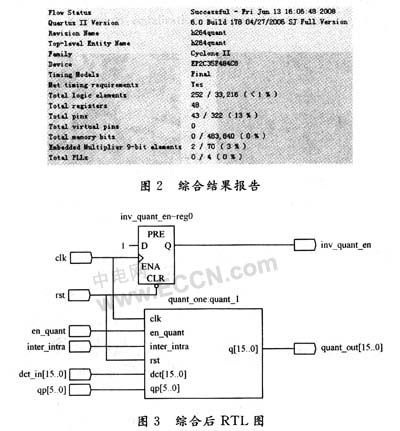

H.264/AVC中量化的Verilog方法介紹及實現(xiàn)

Verilog HDL語言的文件調(diào)用問題:include使用方法介紹

Verilog HDL入門教程

verilog是什么_verilog的用途和特征是什么

Verilog HDL入門教程之Verilog HDL數(shù)字系統(tǒng)設(shè)計教程

Verilog教程之Verilog的命令格式資料說明

Verilog HDL入門教程

Verilog HDL語言組合邏輯設(shè)計方法以及QuartusII軟件的一些高級技巧

Verilog教程之Verilog HDL數(shù)字集成電路設(shè)計方法和基礎(chǔ)知識課件

Verilog的設(shè)計方法介紹

Verilog的設(shè)計方法介紹

評論