您如何在提高開關速度和增加設計復雜度之間尋求平衡?本博客文章將討論此類權衡考量,并提供了一種更高效的方法,有助于您克服設計挑戰并充分發揮 SiC 器件潛力。

這篇博客文章最初由 United Silicon Carbide (UnitedSiC) 發布,該公司于 2021 年 11 月加入 Qorvo 大家庭。UnitedSiC 是一家領先的碳化硅 (SiC) 功率半導體制造商,它的加入促使 Qorvo 將業務擴展到電動汽車 (EV)、工業電源、電路保護、可再生能源和數據中心電源等快速增長的市場。

隨著人們對高效率、高功率密度和系統簡單性的需求不斷增長,碳化硅 (SiC) FET 因其較快的開關速度、較低的 RDS(on) 和較高的額定電壓,逐漸成為對電力工程師極具吸引力的選擇。

但是,SiC 器件較快的開關速度會導致更高的 VDS 尖峰和更長的振鈴持續時間,從而在高電流電平下引入了更多的 EMI。對于從事電動汽車和可再生能源等高功率應用的工程師來說,如何在提高效率并充分發揮先進技術潛力的同時,避免過于復雜的設計將會是一大難題。

?

?

什么是 VDS 尖峰和振鈴?

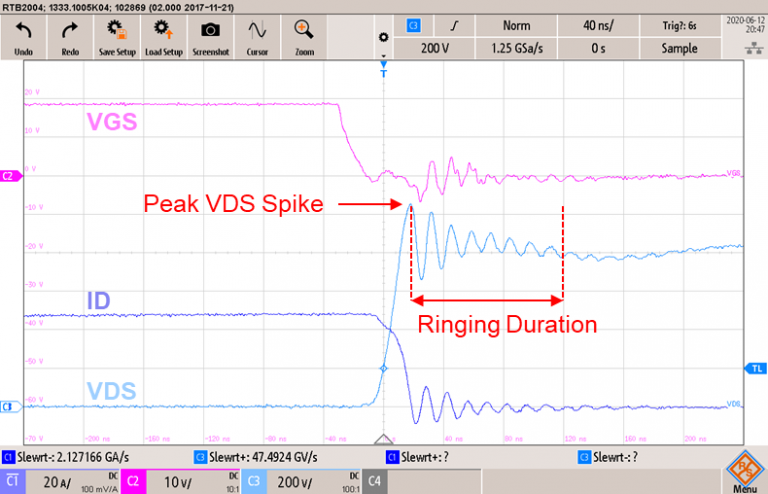

寄生電感是導致 VDS 尖峰和振鈴的根本原因。從 SiC MOSFET 的典型關斷波形(圖 1)可以看出,柵極-源極電壓 (VGS) 在 18V 至 0V 之間,關斷的漏極電流 (ID) 為 50A,且總線電壓 (VDS) 為 800V。由于 SiC MOSFET 具有更快的開關速度,所以會出現較高的 VDS 尖峰和較長的振鈴持續時間。較高的 VDS 尖峰會減少器件應對閃電和負載突變等條件導致的電壓問題的裕量。較長的振鈴持續時間也會引入更多的 EMI。這種現象在高電流電平下更加明顯。

圖 1:SiC 器件的較快開關速度所導致的關斷 VDS 尖峰和振鈴

傳統方法

抑制EMI 的常規解決方案就是使用高柵極電阻 (RG) 來降低電流變化率 (dI/dt)。但實際上,使用高 RG 會顯著增加開關損耗,進而損失效率,所以在使用這種方法時,我們不得不在效率和 EMI 之間做出取舍。

另一種解決方案是減少電源回路中的雜散電感。但是,這需要重新設計PCB 布局,并需要使用尺寸更小、電感更低的封裝。此外,PCB 上能夠減小的電源回路面積是有限的,而且也需要遵守相關安全法規規定的最小間距和最小間隙。此外,更小巧的封裝還會導致熱性能降低。

我們還需要考慮濾波器,以幫助我們滿足EMI 要求并簡化系統權衡。除此之外,我們還可以使用控制方法來減少 EMI。例如,頻率抖動技術可通過擴展電源的噪聲頻譜范圍來減少 EMI。

新方法

一個簡單的 RC 緩沖電路可以幫助克服設計挑戰并充分發揮 SiC 器件的潛力,是一種更為高效的解決方案。事實證明,這個簡單的解決方案可以在廣泛的負載范圍內更高效地控制 VDS 尖峰并縮短振鈴持續時間,并實現可以忽略的關斷延遲。

得益于更快速的 dv/dt 和額外的 Cs,緩沖電路還具有更高的位移電流,從而可以減少關斷過渡期間的 ID 和 VDS 重疊。

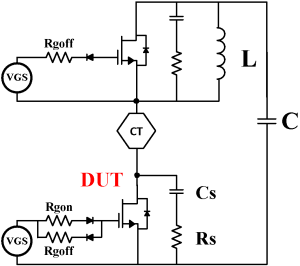

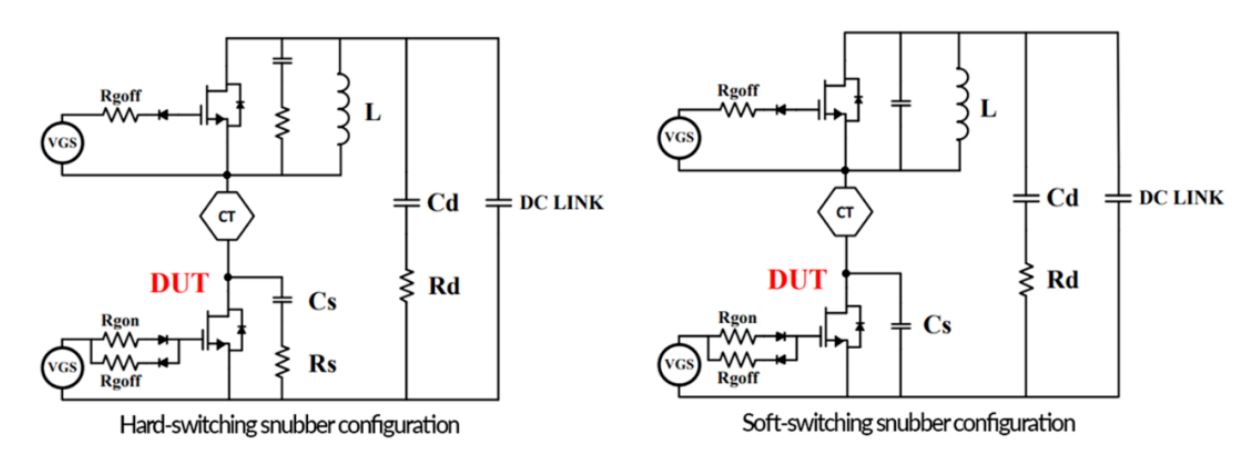

可以通過雙脈沖測試 (DPT) 來證明緩沖電路的有效性。該測試采用了帶感性負載的半橋配置。高端和低端都使用相同的器件,VGS、VDS 和 ID 均從低端器件測量(圖 2)。

圖 2:半橋配置(頂部和底部使用相同的器件)

使用電流互感器 (CT) 測量器件和緩沖電路的電流。因此,測得的開關損耗包括器件開關損耗和緩沖電路損耗。

其中的緩沖電路由 SiC MOSFET 漏極和源極之間的一個 10Ω 電阻和一個 200pF 電容串聯組成。

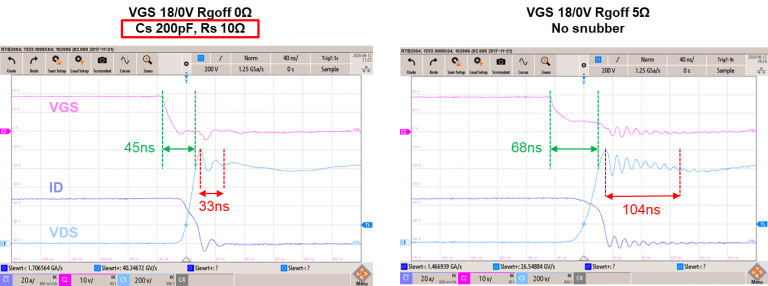

圖 3:RC 緩沖電路可更有效地控制關斷 EMI

首先,我們比較關斷時的情況(圖3)。測試的設備對象與圖 1 相同。左側波形使用 RC 緩沖電路和低 RG(off),而右側波形則使用高 RG(off),未使用緩沖電路。這兩種方法都可以限制關斷 VDS 峰值電壓。但是,使用緩沖電路之后,只需 33ns 即可抑制振鈴,而高 RG(off) 的振鈴持續時間仍超過 100ns。與使用高 RG(off) 相比,使用緩沖電路時的延遲時間更短。由此可判斷,緩沖電路有助于在關斷時更有效地控制 VDS 關斷尖峰和振鈴持續時間。

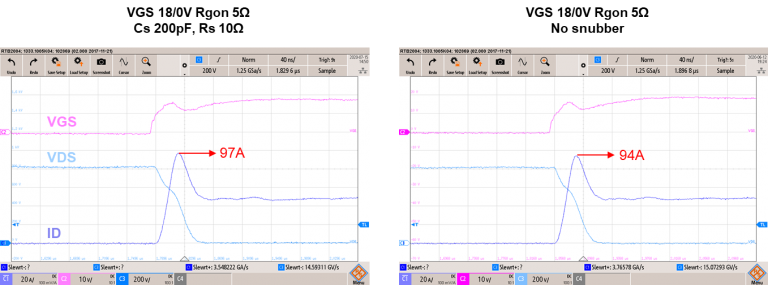

圖 4:RC 緩沖電路在導通期間的有效性

在導通時(圖4),將使用 RC 緩沖電路和 5Ω RG(on) 的波形與未使用緩沖電路的波形進行比較可以發現,使用緩沖電路時,反向恢復電流峰值 (Irr) 略有提高,從 94A 提高到了 97A,除此之外,其對導通波形的影響可以忽略不計。

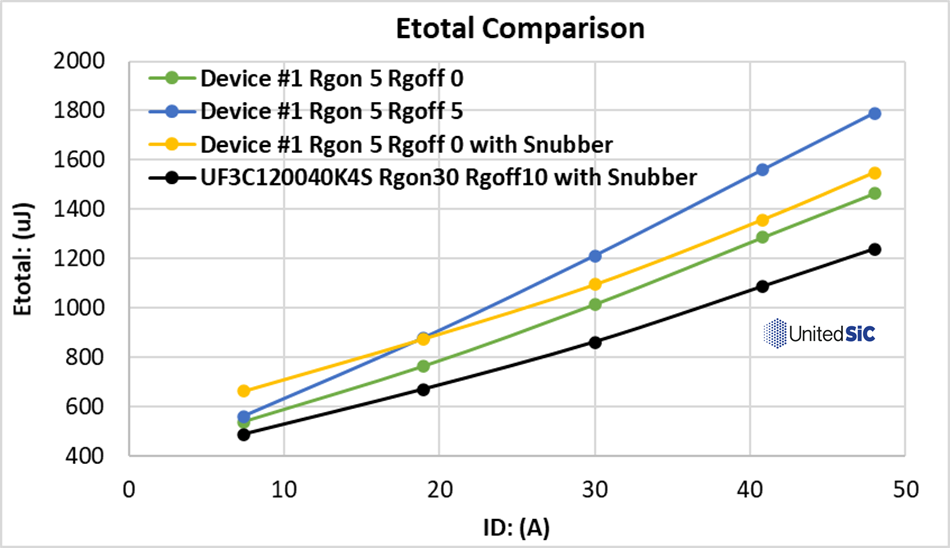

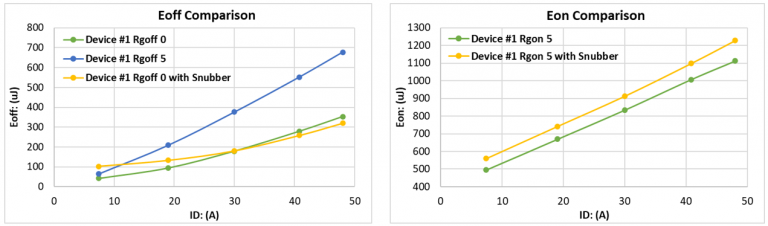

這表明,與高 RG(off) 相比,緩沖電路有助于更有效地控制 VDS 尖峰和振鈴持續時間。但緩沖電路能否更高效呢?(圖 5)

圖 5:比較緩沖電路與高 RG(off) 之間的開關損耗(Eoff、Eon)

在 48A 時,高 RG(off) 的關斷開關損耗是使用緩沖電路和低 RG(off) 時的兩倍以上。由此證明,緩沖電路在關斷時更高效。因為緩沖電路可實現更快速的開關,同時還可以更好地控制 VDS 尖峰和振鈴。

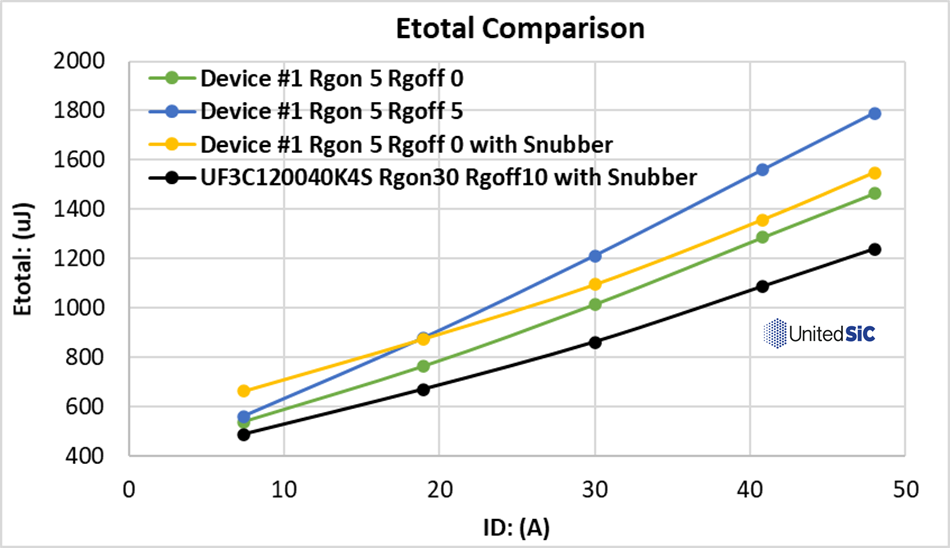

從導通開關損耗的角度看,使用緩沖電路時,Eon 平均增加了 70μJ。為了充分估計整體效率,我們需要將 Eoff 和 Eon 相加,然后比較 Etotal(圖 6)。在全速開關器件時,可以很明顯地看出緩沖電路在漏級電流為 18A 以上時效率更高。對于在 40A/40kHz 下開關的 40mΩ 器件,在使用高 RG(off) 與使用低 RG(off) 和緩沖電路之間,每個器件的開關損耗差為 11W。

圖 6:比較緩沖電路與高 RG(off) 之間的開關損耗 (Etotal)

因此我們可以推斷,與使用高 RG(off) 相比,使用緩沖電路是一種更高效的解決方案。

隨著第 4 代 SiC 器件進入市場,這種簡單的設計解決方案將繼續提供更低的總開關損耗,繼續幫助優化系統功率效率。

關于簡單的緩沖電路如何在 UnitedSiC SiC 器件中實現出色效率的更多信息,請觀看我們近期的研討會:盡可能地降低 SiC FET 的電磁干擾和開關損耗。

您可以點擊此處https://unitedsic.com/events/webinar-minimizing-emi-and-switching-loss-for-fast-sic-fets/觀看完整的研討會。

原文標題:盡可能地降低 SiC FET 的電磁干擾和開關損耗

文章出處:【微信公眾號:Qorvo半導體】歡迎添加關注!文章轉載請注明出處。

-

Qorvo

+關注

關注

17文章

633瀏覽量

77392

原文標題:盡可能地降低 SiC FET 的電磁干擾和開關損耗

文章出處:【微信號:Qorvo_Inc,微信公眾號:Qorvo半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

影響MOSFET開關損耗的因素

為了盡可能的消除模擬開關的影響,xtr105的電壓至少需要多少伏?

差分探頭在測量開關損耗中的應用

零電壓開關與零電流開關的區別

如何使用示波器測量電源開關損耗

淺談電磁干擾系統

水下航行器電機的SiC MOSFET逆變器設計

盡可能地降低 SiC FET 的電磁干擾和開關損耗

盡可能地降低 SiC FET 的電磁干擾和開關損耗

評論