一,邏輯門電路

我們在設(shè)計數(shù)字電路時,都希望器件的功耗低、速度快并且封裝(器件價格)便宜。但這如同所有的“神秘三角”一樣,是不可兼得的。所有的邏輯器件都是在權(quán)衡了功耗、速度和封裝之后的折衷方案:

——“神秘三角”有項目的管理三角:范圍、時間和成本;病毒三角:傳染性、毒性和適應(yīng)性(新冠病毒之所以沒有滅絕人類,就是因為它受到了這“神秘三角”的約束);等。

- 標(biāo)準(zhǔn)封裝在制造時節(jié)省了費用,但降低了器件的靈活性;

- 標(biāo)準(zhǔn)封裝限制了每個封裝單元內(nèi)的門電路和管腳數(shù)量,迫使設(shè)計者將大的系統(tǒng)拆分成多個器件;

——器件之間的信號連接響應(yīng)明顯比同一封裝內(nèi)信號要慢,所需的功率更大;即,使得系統(tǒng)的性能降低,功耗增加。

- 標(biāo)準(zhǔn)的封裝結(jié)構(gòu)限定了器件所允許的最大散熱能力,如果要改進封裝的散熱能力,則需要花費額外的成本;

- 隨著芯片制造工藝的改進,每個邏輯單元尺寸變的更小,在相同的封裝內(nèi)可以集成更多的門電路數(shù)量;高密度的封裝有助于降低產(chǎn)品尺寸和組裝成本,但這意味著需要更大的單位面積散熱的能力;

——每個封裝所允許的最大散熱功耗限定了封裝內(nèi)的門電路數(shù)量。

- 高速器件通常消耗更大的功率,速度和功率在一定程度上可以相互對應(yīng);所以封裝的最大散熱功耗,也稱為了高速的限制因素。

——在相同制造工藝下,速度越高的器件功耗會越大。

所以對于邏輯門電路高速特性,我們主要考慮如下三個方面:

- 功耗:分為靜態(tài)功耗和 動態(tài)功耗 ;

- 速度:

1, 理論上:數(shù)字邏輯的設(shè)計重點是關(guān)注 邏輯門電路的傳輸延時 ;

2, 實際上:通常取決于 最小輸出轉(zhuǎn)換時間(邊沿時間) 。

——較快的轉(zhuǎn)換時間會導(dǎo)致回流,串?dāng)_和振鈴等與傳輸延時無關(guān)的問題倍增。

- 封裝,對于任何高速器件封裝都會引入:管腳寄生電感、寄生電容以及散熱的問題。

二,功耗

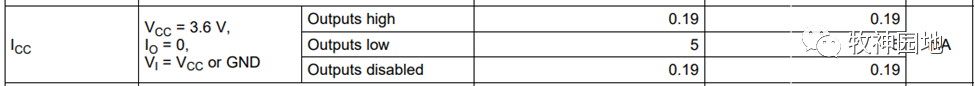

我們想要知道一個邏輯器件的功耗,一般會查看其數(shù)據(jù)手冊上的典型電流值Icc,但這并非是器件的實際功耗,或則說在一些條件下器件的功耗會遠大于標(biāo)稱的Icc電流值。舉個栗子:常用的16位驅(qū)動器74LVTH16245,如果16個輸出管腳同時快速翻轉(zhuǎn),那么其實際功耗應(yīng)該會遠超規(guī)格書中的Icc,如下圖所示。

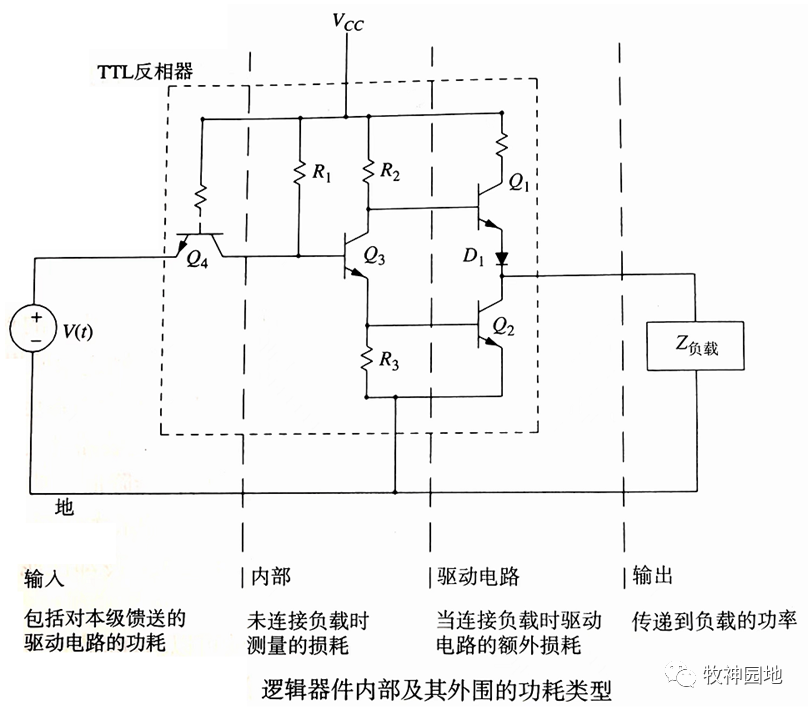

如下圖所示,為一個簡單的TTL反相器的內(nèi)部邏輯結(jié)構(gòu),從功耗角度分為4部分:

——如下每一種功耗都可以進一步細分為:靜態(tài)功耗和動態(tài)功耗。

- 輸入功耗;

- 內(nèi)部功耗;

- 驅(qū)動電路功耗;

- 輸出功耗。

1,靜態(tài)功耗和動態(tài)功耗

這里非常重要的概念是:靜態(tài)功耗和動態(tài)功耗。我們所有的功耗都可以將它分為這兩部分。

靜態(tài)功耗:指邏輯電路保持一個邏輯狀態(tài)時消耗的功率。靜態(tài)功耗可以由每個阻性單元兩端電壓V和電流I的乘積計算所得(P靜態(tài) = V*I),并且求和得到總功率,這是在沒有負(fù)載情況下的靜態(tài)功耗(即數(shù)據(jù)手冊上看到的Icc標(biāo)稱值)。

——需要強調(diào)的是:靜態(tài)功耗是不計負(fù)載損耗的器件自身功耗。

但實際上邏輯電路不跳變則無法傳遞信息,也就成了無用之物,我們需要器件“動”起來,那么器件就要消耗超過它正常靜態(tài)功耗之外的“額外功率”。當(dāng)這個變化很有節(jié)奏時,舉個栗子:以時鐘信號頻率跳變;那么:動態(tài)功耗 = 周期頻率* 每個周期額外的功率。

——動態(tài)損耗最常見的原因:負(fù)載電容(RC充電)和偏置電流。

如下圖所示為驅(qū)動一個容性負(fù)載時的情形:

- t1時刻電路開關(guān)A閉合(B斷開):負(fù)載電容充電至Vcc,在電容充電時電流流過驅(qū)動電阻“R充電”,有功率消耗;

- t2時刻電路開關(guān)B閉合(A斷開):負(fù)載電容通過電阻“R放電”進行放電,電流流過驅(qū)動電阻,也有功率消耗;

- t1和t2之間有一個“死區(qū)時間”(A和B都斷開):此死區(qū)時間是為了防止電源Vcc直接通過開關(guān)短路到GND,造成器件損耗增加,甚至燒壞內(nèi)部開關(guān)。

——該“死區(qū)時間”的原理同開關(guān)電源,在邏輯門電路中,其主要影響器件的功耗和電平切換速率(I/O管腳支持的最大速率)。

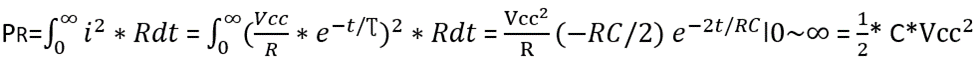

那么一個電壓源通過電阻R對容性負(fù)載C充電或放電時,是如何計算它的功耗呢?

- 胖友們已經(jīng)知道電容是一個儲能元件,并不會耗電,所以在容性負(fù)載充放電過程中不會耗電;

——如果有胖友還對這個問題有疑問:電容器有ESR,有寄生電阻呀等等;建議再回顧《阻容感基礎(chǔ)01》中的內(nèi)容,另外我想說的是:我們要區(qū)分電容與電容器這兩個概念;電容是指容性,而電容器是指具體的器件,對于容性本身來說,它是不會造成電能的損耗,而造成損耗的是阻性。

- 我們來考慮RC充/放電電路中電阻R的能量消耗,有如下兩個計算方法:

1, 直接計算電阻R在充電RC充電電路中的功耗:P = I2 * R,由于電流并非線性的,而是指數(shù)函數(shù):(U/R)*exp(-t/τ);所以需要用到積分公式來進行計算,具體計算如下:

RC放電電路是充電的反向過程,同理其消耗在電阻R上的功耗也為(1/2)* CV2cc;所以充放電的總功耗為:P = CV2cc;

——指數(shù)函數(shù)的積分(面積)是1(即指數(shù)函數(shù)積分從-至x的積分值就是其本身,t 是-∞至0,那么可得積分為e?= 1),具體請參考《傳遞函數(shù)和波特圖》的“說在開頭”章節(jié)關(guān)于自然常數(shù)e的描述。

2, 將RC電路看成一個整體,同時將充電和放電看成一個整體;那么器件給R/C充電的總能量,就等于RC充電和RC放電兩個過程中總共消耗的能量;電源消耗總能量:P = VccIt = VccQ = Vcc Vcc C = C V2cc;

——電源總能量是指器件Vcc通過“R充電”給容性負(fù)載C充電,然后由容性負(fù)載C通過“R放電”釋放掉的總電能量;經(jīng)過整個充電和放電過程,容性負(fù)載上并無能量儲存,所以所有的能量都被電阻所消耗,即,我們可認(rèn)為Vcc釋放出來的能量都消耗在了電阻上。

3, 所以我們得到結(jié)論:對于恒壓電源充電 / 放電電路來說 ,不管串接的電阻R阻值是多少,每個充電周期消耗掉的能量是總電源能量的一半:(1/2)* CV2cc;而整個充放電周期(管腳輸出一個時鐘周期)消耗的能量是:C V2cc。

- 如果器件管腳以f Hz頻率循環(huán)工作,那么驅(qū)動電路的功率為:f * C* V2cc。

——舉個栗子:輸出10MHz時鐘信號,負(fù)載電容為10pF,電壓為3.3V,那么驅(qū)動功率:1010?Hz1010?12F3.33.3V2 ≈ 1.110?3W = 1.1mW;這么一算單個管腳的功耗還是比較小的;但這只考慮了理想情況,后續(xù)還有跟個詳細的分析。

2,疊加偏置電流的動態(tài)功耗

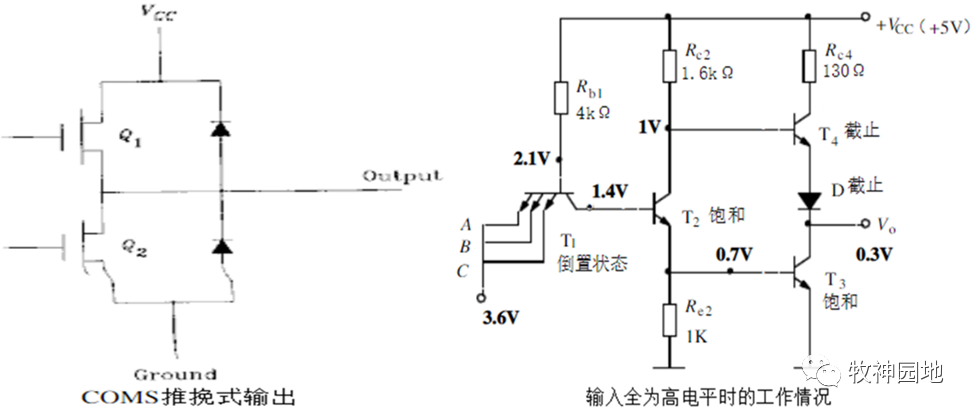

如上圖TTL反相器的輸出驅(qū)動電路在H(高電平)和L(低電平)之間較低轉(zhuǎn)換,Q1和Q2交替處于導(dǎo)通狀態(tài),而非兩者同時導(dǎo)通;這種電路配置有兩個激勵電路:一個把輸出電壓上拉到H,另一個將輸出電壓下拉到L,通常稱之為推挽輸出電路。TTL和CMOS都有推挽輸出,如下左圖為CMO推挽式輸出電路。

TTL推挽式輸出結(jié)構(gòu)工作原理如上右圖所示,結(jié)構(gòu)中各個器件的作用如下:

- 二極管D保證了在T2和T3全飽和時,輸出電平鉗位輸出是低電平,防止T3和T4同時導(dǎo)通產(chǎn)生大的交越電流;

——所有推挽式輸出電路都需要有保護電路,防止高驅(qū)動和低驅(qū)動電路同時導(dǎo)通。

- 如果輸入電平轉(zhuǎn)換很快時,每個周期都有一個交越電流并消耗一定的功耗(如下圖所示),交越電流產(chǎn)生的額外功耗與轉(zhuǎn)換速率成正比;

——對于一個快速的輸入轉(zhuǎn)換,重疊電流脈沖的大小和波形在每個周期都是一致的,并且每個周期消耗的能量也相同,所以這部分額外功耗與轉(zhuǎn)換速率成正比,與容性負(fù)載導(dǎo)致的功耗不同:交越電流產(chǎn)生的功耗并不隨電源電壓的平方增加。

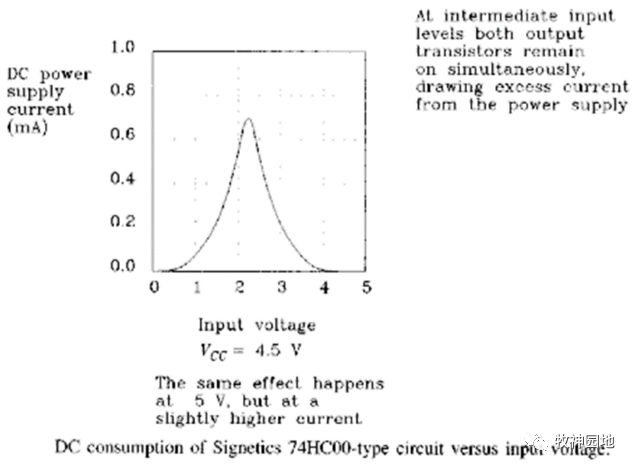

- 減緩輸入信號邊沿,會導(dǎo)致交越時間延長;如上圖為門電路典型直流電源電流與輸入電壓的函數(shù)關(guān)系曲線。

——減緩輸入電壓的轉(zhuǎn)換時間往往會延長交越時間,導(dǎo)致T3和T4同時導(dǎo)通的電壓附近停留的時間會更長,所以很多器件會對輸入信號邊沿時間有要求。

- 對于TTL電路來說,交越效應(yīng)相比CMOS更顯著;如果將一個TTL反相器的輸入端與其輸出端相連,會產(chǎn)生自我偏置,從而進入交越范圍內(nèi),消耗大量能量。

——因此TTL電路不適合用作線性的小信號處理器(如:振蕩器),因為它們在線性工作狀態(tài)是要消耗額外的能量。

3,輸入功耗

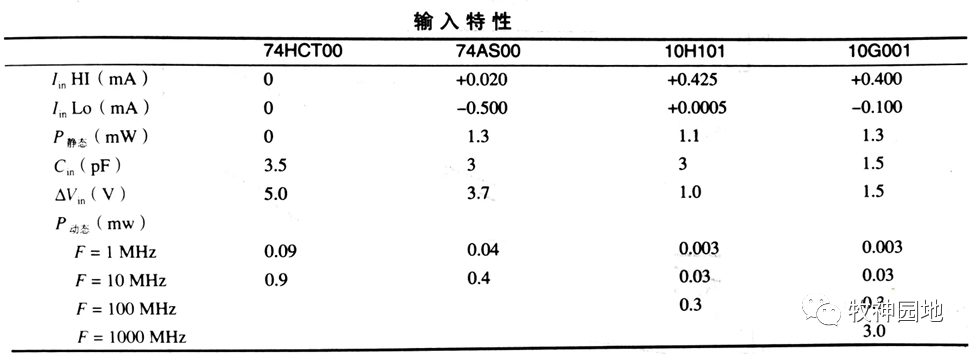

芯片的輸入功耗,來自于輸出器件,并由它來激活輸入電路。對于輸入電路的偏置和觸發(fā)來說是必需的。如下表對比了4種不同邏輯器件的靜態(tài)和動態(tài)輸入特性:

- 靜態(tài)輸入功耗:驅(qū)動電壓和輸入電流的乘積;它包含了接收邏輯器件內(nèi)部功耗和驅(qū)動器的功耗之和。

- 動態(tài)輸入功耗:需要計算輸入電容、典型供電電壓和工作頻率代入公式:功率 = f * C*V2cc;計算出電路驅(qū)動該輸入時的總功耗。

——這些功耗相對比較小,只有較大數(shù)量扇出(Fanout)或系統(tǒng)要求在極低功耗運行時,才能體現(xiàn)其重要性。

4,內(nèi)部功耗

內(nèi)部功耗是指邏輯器件內(nèi)部偏置電流和內(nèi)部邏輯翻轉(zhuǎn)的功耗,包括靜態(tài)和動態(tài)功耗。

- 靜態(tài)內(nèi)部功耗:是指在無負(fù)載驅(qū)動、輸入端處于隨機狀態(tài)條件下的功耗,是所有輸入狀態(tài)(高/低/高阻)下的平均值;

- 動態(tài)內(nèi)部功耗:是指內(nèi)部動態(tài)耗散常數(shù)“K動態(tài)”是在輸出懸空,預(yù)設(shè)輸入頻率為時測量得到總功率P總,而后計算動態(tài)功耗常數(shù): K動態(tài) = (P總 – P靜態(tài))/f ;

——動態(tài)常數(shù)K動態(tài)表示周期頻率每增加1Hz將額外消耗的功率。

- 計算任意頻率下的總功耗:總 = P靜態(tài) + f*K動態(tài)。

——動態(tài)頻率在相對較頻率(>10MHz)時才會比較明顯。

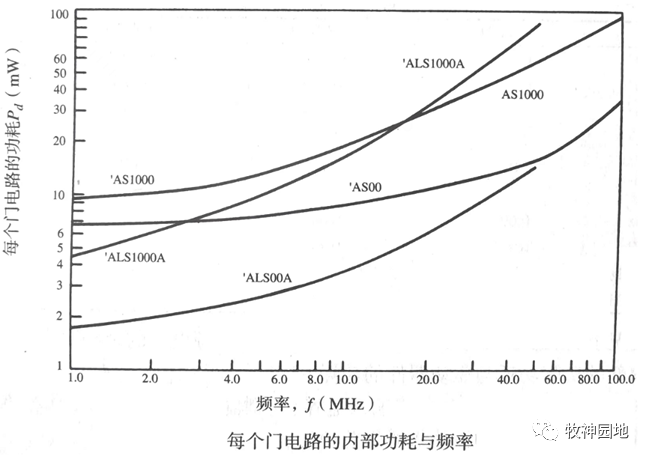

在非常寬的頻率范圍內(nèi),CMOS器件的內(nèi)部功耗和周期頻率呈明顯的線性關(guān)系,這是因為CMOS電路的內(nèi)部靜態(tài)功耗非常低;而TTL器件由于內(nèi)部靜態(tài)功耗較大,所以直到工作頻率接近器件的最大工作頻率時才呈現(xiàn)出線性關(guān)系。如下圖所示為不同類型TTL邏輯器件的門電路內(nèi)部功耗與工作頻率的關(guān)系曲線:

- 在10MHz以上:動態(tài)功耗遠大于靜態(tài)功耗,總功耗曲線幾乎與頻率成正比;

- 在1MHz以下:動態(tài)功耗小于靜態(tài)功耗,總功耗曲線相對于頻率是平坦的。

CMOS器件數(shù)據(jù)手冊用等效電容Cpd來表示內(nèi)部功耗,CMOS內(nèi)部功耗 = Cpd * V2 * f。可得到CMOS器件功耗的關(guān)聯(lián)因素:

- 與管腳工作頻率和負(fù)載電容成正比;

1,器件工作頻率越來越高,是整個行業(yè)的發(fā)展方向,所以不能以降低管腳工作頻率為代價來減小器件功耗;

2,負(fù)載電容與器件封裝技術(shù)相關(guān),器件小型化是發(fā)展趨勢,但負(fù)載電容不能無限制地減小,需要付出更多的成本代價。

- 與I/O工作電壓的平方成正比。

——減小I/O工作電壓對功耗影響非常大(平方正比關(guān)系),是最明確可行的方案,舉個栗子:I/O電壓從5V減小至1V,那么功耗將減小至1/25;所以我們看到器件工作電壓是越來越小的趨勢。

5,驅(qū)動電路功耗

邏輯器件中的主要能量消耗在輸出驅(qū)動電路上,而驅(qū)動電路功耗由:輸出電路的結(jié)構(gòu)、邏輯電平、輸出負(fù)載以及運行速度決定。我們主要考慮2種輸出結(jié)構(gòu):

- 推挽電路輸出;

- 射極跟隨器輸出;

5.1 推挽電路輸出

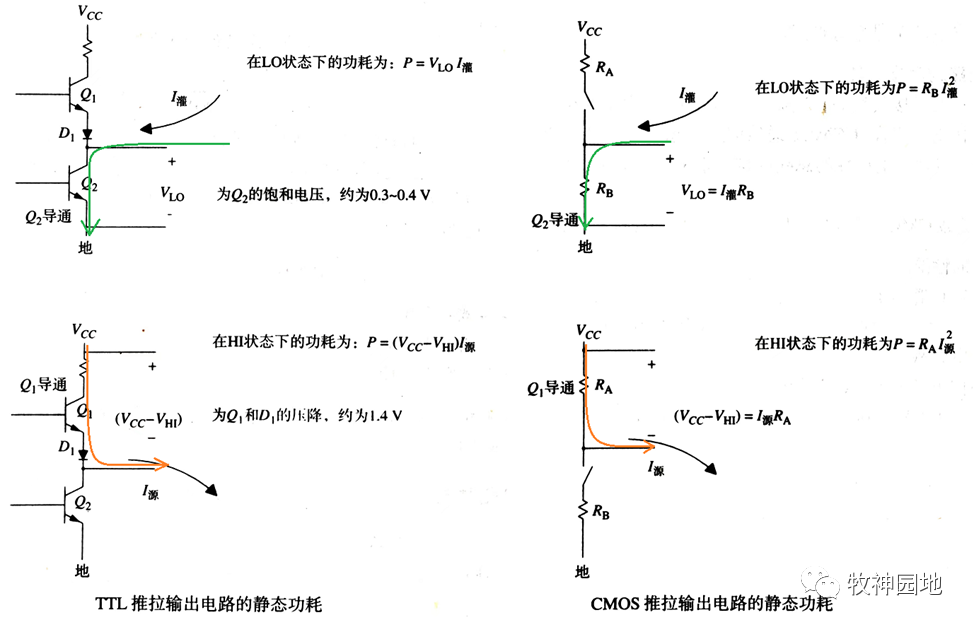

如下左圖所示為理想TTL驅(qū)動器在H(高電平)和L(低電平)狀態(tài)下的靜態(tài)功耗,對于標(biāo)準(zhǔn)TTL器件來說Q2處于飽和狀態(tài)(低電平)時的壓降VL固定在大約0.3V;在高電平H狀態(tài)下,壓降由Q1的VBE和正向偏置二極管D1鉗位(Vcc - VHI),約為1.4V。此時TTL驅(qū)動電流電路總靜態(tài)功耗平均值近似為:P靜態(tài) = (0.3I灌+1.4I源)/2。

——此時Q1不會進入飽和狀態(tài),因為其B極電壓不會上升到高于它C極電壓(三極管飽和狀態(tài)判斷,具體參考《三極管原基礎(chǔ)》相關(guān)章節(jié))。

如上右圖所示為CMOS驅(qū)動器電路,MOS管的導(dǎo)通壓降很低,通常等效串聯(lián)了上拉和下拉電阻;所以CMOS驅(qū)動器在高電平和低電平狀態(tài)下的靜態(tài)功耗:P靜態(tài) = (RbI2灌+RaI2源)/2。

——舉個栗子:某器件VOL(Io = 4mA),25℃時典型值為0.15V,最大值為0.33V;某器件VOH(Io = -4mA),25℃時典型值為4.32V,最大值為3.48V;那么根據(jù)R = V/I,可計算Ra的阻抗范圍是:37Ω83Ω;Rb的阻抗范圍是:45Ω165Ω。在不同電源電壓下,CMOS驅(qū)動器的輸出電阻變化很大。

推挽電路輸出負(fù)載能力,如果只按照所接負(fù)載直流輸入要求進行計算,使輸出負(fù)載能力達到它的直流最大扇出,特別是CMOS總線理論上的扇出能力是無限的;重負(fù)載的總線結(jié)構(gòu)會帶來兩個問題:

- 邊沿時間會變緩;

- 驅(qū)動器功耗增大。

輸出總負(fù)載電容為:器件管腳寄生電容(10pf/pin)+PCB走線寄生電容(2pf/in)。舉個栗子:我們有20個負(fù)載和10in長度的PCB走線,那么總電容 = 負(fù)載電容+走線電容 = 2010pf/pin + 10in 2pf/in = 220pF;此時信號邊沿時間會變緩以及線路延遲會非常大。充電時間常數(shù)約等于驅(qū)動器輸出電阻乘以輸出負(fù)載電容,Trc = RC = 110Ω 220pF = 24ns(假設(shè)總線驅(qū)動器輸出電阻為110Ω)。

——充電時間常數(shù)是指:電容從0充電至0.63Vcc所需的時間,升至高電平90%所需時間是Trc的兩倍多:T10-90 = 2.2Trc = 53ns。

計算推挽電路動態(tài)輸出功耗:f * C* V2cc;假設(shè)最差供電電壓為5.5V,負(fù)載電容如上所述為220pF,信號線輸出頻率為10MHz,那么可得每個驅(qū)動器的功耗:1010?Hz22010?12F5.5V2 ≈ 0.067W,如果這是一個16bit的驅(qū)動器,那么同時翻轉(zhuǎn)產(chǎn)生的器件總功耗:P總 = 16*0.067w ≈ 1.1W。而且當(dāng)上升時間緩慢時,驅(qū)動器的功耗會更高。

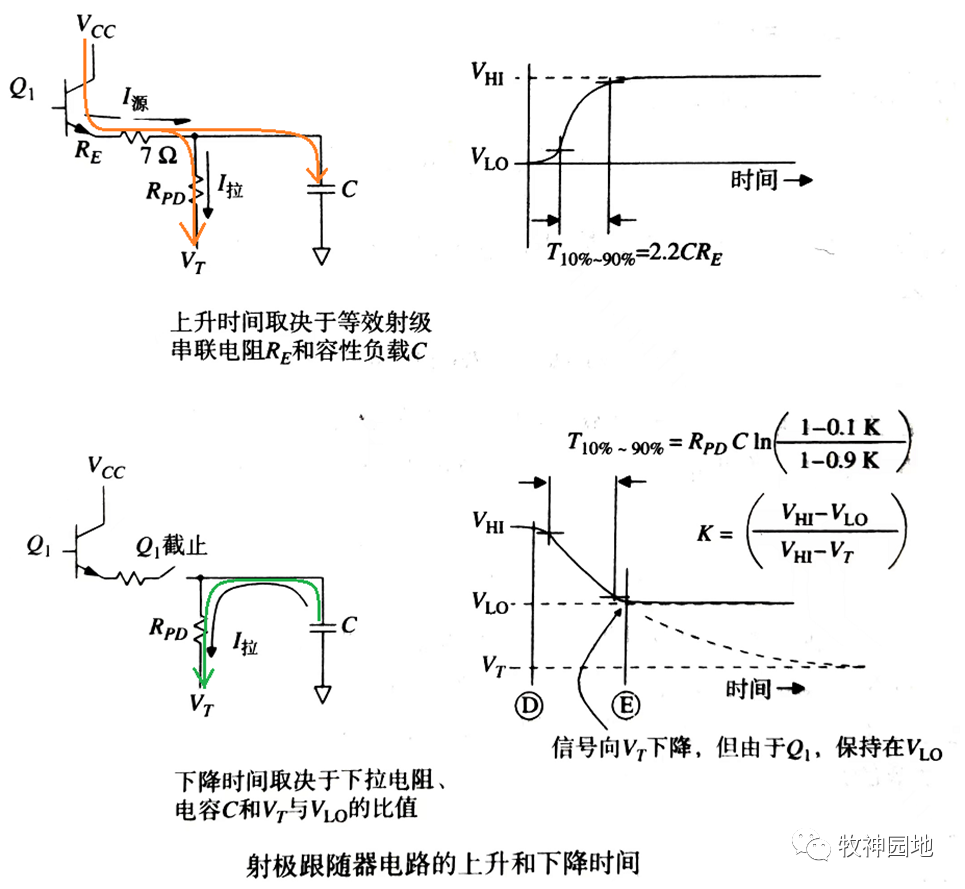

5.2 射極跟隨器(ECL)電路輸出

如下圖所示為ECL射極跟隨器輸出電路,該電路在HI(高電平)和LO(低電平)兩個狀態(tài)下都有電流流過。HI(高電平)和LO(低電平)輸出電壓都是相近的,這些器件一般用-5.2V電源供電,高電平VHI= -0.9V,低電平VLO = -1.7V;同時射極耦合邏輯電路需要有一個上拉電阻R,用于端接至Vt = -5.2V或中間電壓 -2.0V(戴維南匹配,具體參考《反射與阻抗匹配》),那么可得輸出電路的靜態(tài)功耗:

P靜態(tài) = (1/2) [(Vcc-Vhi) (Vhi-Vt)+(Vcc-Vlo)*(Vol-Vt)]/R

其中,Vcc =0V,VHI= -0.9V,VLO = -1.7V, Vt = -5.2V;那么計算可得:P靜態(tài) = 4.91/R。

同樣,如果將R下拉至-2.0V時,可以計算得到:P靜態(tài) = 0.75/R。

那么我們可以得到:對于相同的電阻值R,使用中間電壓(-2.0V)端接時表現(xiàn)出明顯的功耗優(yōu)勢;這是因為當(dāng)電源電壓被下拉到-2.0V時,下拉電阻汲取的電流比較小(意味著低功耗)。

- 如上圖所示,當(dāng)晶體管Q1導(dǎo)通(信號上升沿),電流從晶體管輸出流向下拉電阻Rpd和容性負(fù)載;由于Rpd相對于Re更大,Rpd的下拉電流相對于Re輸出的I源電流可以忽略不計,所以輸出電壓上升時間不受下拉電流的影響;

——上圖中給出Re = 7Ω,當(dāng)給容性負(fù)載C充電時,其充電時間常數(shù)為:Trc = Re* C;而充電至90%所需的時間為T10-90 = 2.2*Trc。

- 當(dāng)晶體管Q1截止(信號下降沿),從而不再有電流流過發(fā)射極;只有容性負(fù)載C通過下拉電阻Rpd放電:下降時間與電容C放電的速度成正比,功耗與靜態(tài)下拉電流成正比;此時需要有一個大電流迅速地將電容C放電;

——如果Q1完全截止(忽略其漏電流),從90%-10%的下降時間為:T90-10 = RpdCln[(1-0.1K)/(1-0.9K)];其中常數(shù)K = (Vhi-Vlo)/(Vhi-Vi);如上面栗子參數(shù)(Vt = -5.2V),可計算K = 0.186, T90-10 = 0.164RpdC。若Vt = -2.0V,那么計算K = 0.727,T90-10 = 0.987RpdC。

- 當(dāng)Vt = -2.0V時雖然功耗相對較小,但是邊沿時間會更長,為了達到相同的相同時間,必須要求所采用的下拉電阻相比于Vt = -5.2V電阻的阻值更小,而一旦選擇了較小的電阻,其兩種匹配方式的功耗數(shù)也大致相等。

——同時考慮其它方面:1,采用Vt = -5.2V不需要引入單獨的新電源;2,采用Vt = -2.0V時下拉電阻范圍在50100Ω,正好可以作為線路的終端匹配(阻抗匹配),而Vt = -5.2V時端接電阻在330680Ω,不適合做終端匹配(關(guān)于終端匹配相關(guān)知識參考:《反射與阻抗匹配》章節(jié)內(nèi)容)。

- ECL輸出電路相對于推挽輸出電路的好處是:

1, 由于電壓擺幅小,所以電路動態(tài)功耗非常小(下拉電阻產(chǎn)生的損耗);

2, 沒有推挽輸出電路的高低電平切換“死區(qū)時間”,切換的速率更快,且無額外損耗。

-

驅(qū)動器

+關(guān)注

關(guān)注

52文章

8168瀏覽量

146049 -

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42581 -

TTL反相器

+關(guān)注

關(guān)注

0文章

6瀏覽量

7027 -

RC充電

+關(guān)注

關(guān)注

0文章

3瀏覽量

5065 -

GND

+關(guān)注

關(guān)注

2文章

529瀏覽量

38657

發(fā)布評論請先 登錄

相關(guān)推薦

電平設(shè)計基礎(chǔ)1:邏輯門電路高速特性(1)

電平設(shè)計基礎(chǔ)1:邏輯門電路高速特性(1)

評論