由于摩爾定律逐漸接近其物理極限,為進一步追求速度、功耗、功能與制造成本的平衡,后道封裝更加強調封裝集成度、I/O引腳密度及功能集成度,因此SiP、2.52D/3D集成及WLP成為未來集成電路后道封裝工藝的發展重點。 當前最主要的封裝形式仍然為倒裝鍵合和引線鍵合,先進封裝(包括2.5D集成、Fan-out WLP/PLP等)已經進入市場并占據一定市場份額,3D集成是當前技術研究熱點。2018年底,英特爾發布了首個商用3D集成技術:FOVEROS混合封裝。

傳統的集成電路后道工藝設備主要包括:劃切設備、減薄設備、鍵合設備、測試分選設備等。SiP、2.5D/3D集成、WLP等先進封裝技術大量采用了前道工藝中的光刻、刻蝕、金屬化、平坦化等工藝設備,集成電路前后道工藝呈現融合發展的態勢。集成電路后道工藝設備的發展需要滿足未來SiP、2.5D/3D集成、WLP等先進封裝技術發展的需求。

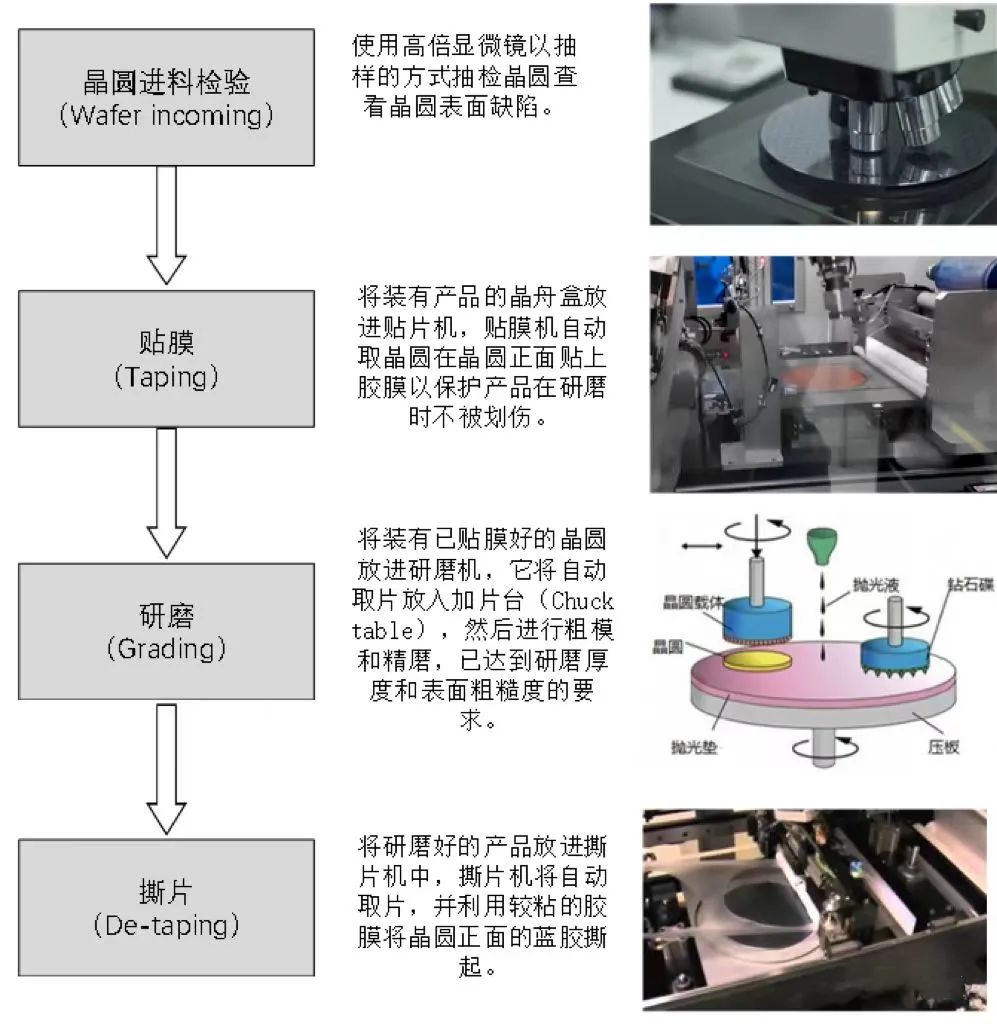

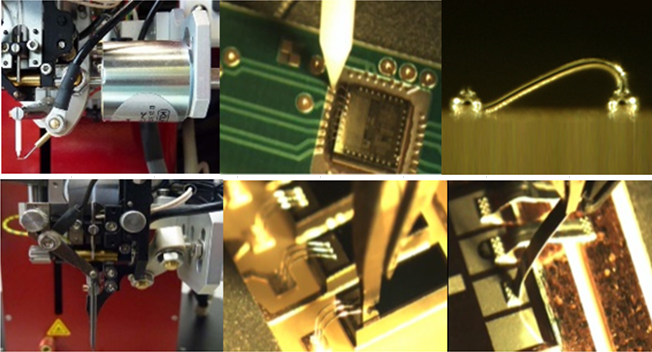

主要技術挑戰 (1)超薄晶圓減薄及劃切設備。代工廠出廠的硅晶圓厚度一般為0.7~0.8 mm,為保證芯片小尺寸封裝的要求,硅晶圓在封裝中一般需要通過背面研磨/拋光過程進行減薄。當前大生產中引線鍵合芯片的減薄工藝可達30μm,倒裝芯片的減薄工藝一般在50μm左右,晶圓減薄設備已經相對成熟,可以支持直到2030年的減薄工藝需求。  超薄晶圓劃切可能導致芯片的卷曲和碎裂,傳統的機械劃切和激光劃切在劃切質量和成本等方面都面臨著極大的挑戰。一種新興的等離子體劃切技術近年來逐漸受到關注:等離子體劃切技術與干法刻蝕技術相近,利用等離子體物理轟擊和化學反應在硅片表面形成深而細的溝槽,從而達到分割芯片的目的。相對于傳統劃切技術,等離子體劃切具有三大優點:一是芯片側壁無損傷,沒有應力導致的芯片彎曲;二是可以實現多條線的批量劃切,減少工藝時間;三是劃切通道窄,減少材料損失。 (2)引線鍵合設備。目前,引線鍵合仍然是主流的芯片互聯方式,占全部封裝市場的77%左右,其中用于系統級封裝的引線鍵合市場增長迅速。當前引線鍵合工藝及設備的發展趨勢主要包括四個方面:一是降低成本(主要通過引線材料的變革,由Au線逐漸變更為Ag、Cu線);二是提高產能(近年來,除提升鍵合機定位平臺電機速度外,鍵合工藝的優化在提升鍵合設備產能中發揮的作用越來越重要);三是互聯密度更大(主要通過新的封裝結構和工藝實現);四是采用智能引線鍵合機(智能引線鍵合機將實現精確的工藝控制、缺陷檢測和可追溯性,從而縮短封裝產品的研發時間、提高良率和產能,是未來先進引線鍵合技術發展的主要驅動力之一)。

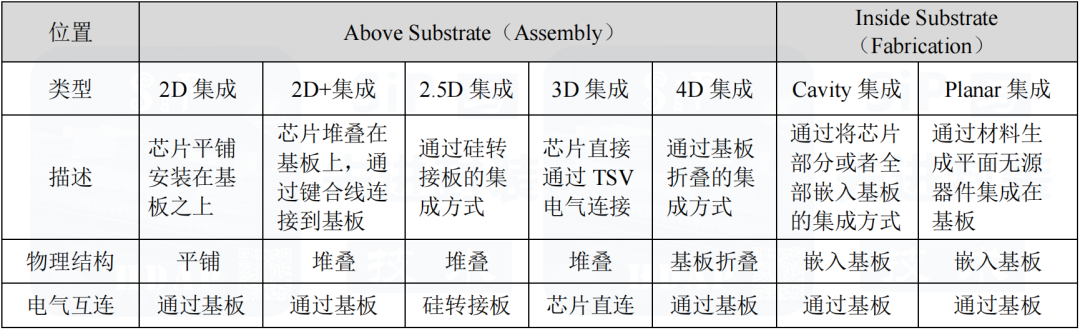

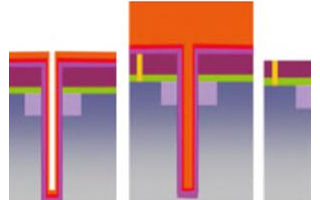

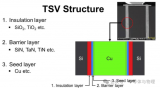

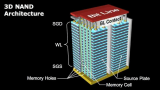

超薄晶圓劃切可能導致芯片的卷曲和碎裂,傳統的機械劃切和激光劃切在劃切質量和成本等方面都面臨著極大的挑戰。一種新興的等離子體劃切技術近年來逐漸受到關注:等離子體劃切技術與干法刻蝕技術相近,利用等離子體物理轟擊和化學反應在硅片表面形成深而細的溝槽,從而達到分割芯片的目的。相對于傳統劃切技術,等離子體劃切具有三大優點:一是芯片側壁無損傷,沒有應力導致的芯片彎曲;二是可以實現多條線的批量劃切,減少工藝時間;三是劃切通道窄,減少材料損失。 (2)引線鍵合設備。目前,引線鍵合仍然是主流的芯片互聯方式,占全部封裝市場的77%左右,其中用于系統級封裝的引線鍵合市場增長迅速。當前引線鍵合工藝及設備的發展趨勢主要包括四個方面:一是降低成本(主要通過引線材料的變革,由Au線逐漸變更為Ag、Cu線);二是提高產能(近年來,除提升鍵合機定位平臺電機速度外,鍵合工藝的優化在提升鍵合設備產能中發揮的作用越來越重要);三是互聯密度更大(主要通過新的封裝結構和工藝實現);四是采用智能引線鍵合機(智能引線鍵合機將實現精確的工藝控制、缺陷檢測和可追溯性,從而縮短封裝產品的研發時間、提高良率和產能,是未來先進引線鍵合技術發展的主要驅動力之一)。  (3)倒裝鍵合設備。相對引線鍵合,倒裝鍵合是高密度封裝技術的主要發展方向,有助于實現堆疊芯片和三維封裝工藝,在2.5D/3D集成、晶圓級封裝、系統級封裝等封裝技術領域均有廣泛應用。 目前倒裝芯片的互聯方式主要包括熱超聲(采用金球凸點,Gold stud)、回流焊(采用錫球凸點,Solder bump)和熱壓(采用銅柱凸點,Copper pillar)三種鍵合工藝。熱超聲倒裝鍵合設備基于成熟的引線鍵合技術,主要用于I/O密度較低的芯片中;回流焊工藝設備通過熱回流將蘸有助焊劑的芯片焊接在基板上,是相對主流的倒裝焊設備;熱壓工藝設備主要面向銅柱凸點和微銅柱凸點,凸點密度更高,代表著倒裝設備的發展方向,熱壓工藝設備最大的技術挑戰是設備的裝片精度(提高裝片精度會犧牲工藝速度,從而增大工藝成本)。 除以上三種主要倒裝鍵合技術外,正在開發的先進倒裝技術包括基于熱壓工藝設備的無凸點Cu-Cu直接鍵合技術。 (4)2.5D/3D集成。2.5D集成是傳統的2D封裝(兩個裸片在封裝體內水平排布)的升級,指兩個或更多的裸片以倒裝鍵合的形式在基板上水平排布。3D集成指兩個或更多的裸片相互堆疊,并直接互聯。2.5D/3D集成技術相對傳統的2D封裝,可實現更高的性能、更低的能耗、更低的延遲、以及更小的芯片尺寸。 2.5D/3D集成都離不開TSV(硅通孔)、倒裝鍵合等封裝技術,TSV工藝是關鍵,相關設備發展是重點。TSV是通過芯片和芯片之間、晶圓和晶圓之間制造垂直通孔,在通孔中電鍍銅實現垂直方向上芯片的互聯,主要包括通孔刻蝕(使用深反應離子束刻蝕或激光打孔設備)、絕緣層/介電層沉積(CVD設備)、阻擋層/種子層沉積(PVD設備)、通孔鍍Cu(ECD設備)、多余Cu去除(CMP設備)等工藝步驟,可見,TSV技術主要基于集成電路前道設備實現。

(3)倒裝鍵合設備。相對引線鍵合,倒裝鍵合是高密度封裝技術的主要發展方向,有助于實現堆疊芯片和三維封裝工藝,在2.5D/3D集成、晶圓級封裝、系統級封裝等封裝技術領域均有廣泛應用。 目前倒裝芯片的互聯方式主要包括熱超聲(采用金球凸點,Gold stud)、回流焊(采用錫球凸點,Solder bump)和熱壓(采用銅柱凸點,Copper pillar)三種鍵合工藝。熱超聲倒裝鍵合設備基于成熟的引線鍵合技術,主要用于I/O密度較低的芯片中;回流焊工藝設備通過熱回流將蘸有助焊劑的芯片焊接在基板上,是相對主流的倒裝焊設備;熱壓工藝設備主要面向銅柱凸點和微銅柱凸點,凸點密度更高,代表著倒裝設備的發展方向,熱壓工藝設備最大的技術挑戰是設備的裝片精度(提高裝片精度會犧牲工藝速度,從而增大工藝成本)。 除以上三種主要倒裝鍵合技術外,正在開發的先進倒裝技術包括基于熱壓工藝設備的無凸點Cu-Cu直接鍵合技術。 (4)2.5D/3D集成。2.5D集成是傳統的2D封裝(兩個裸片在封裝體內水平排布)的升級,指兩個或更多的裸片以倒裝鍵合的形式在基板上水平排布。3D集成指兩個或更多的裸片相互堆疊,并直接互聯。2.5D/3D集成技術相對傳統的2D封裝,可實現更高的性能、更低的能耗、更低的延遲、以及更小的芯片尺寸。 2.5D/3D集成都離不開TSV(硅通孔)、倒裝鍵合等封裝技術,TSV工藝是關鍵,相關設備發展是重點。TSV是通過芯片和芯片之間、晶圓和晶圓之間制造垂直通孔,在通孔中電鍍銅實現垂直方向上芯片的互聯,主要包括通孔刻蝕(使用深反應離子束刻蝕或激光打孔設備)、絕緣層/介電層沉積(CVD設備)、阻擋層/種子層沉積(PVD設備)、通孔鍍Cu(ECD設備)、多余Cu去除(CMP設備)等工藝步驟,可見,TSV技術主要基于集成電路前道設備實現。  TSV工藝及設備技術在持續提升中,主要挑戰和發展方向包括:高密度、高深寬比刻蝕、絕緣層和金屬層的低溫工藝、高速通孔填充、持續降低成本等。 (5)晶圓級封裝(WLP)。晶圓級封裝是在晶圓上直接進行裸芯片封裝,再切割形成獨立的芯片。晶圓級封裝可減少封裝材料及工序,同時具有輕薄短小的特點,是封裝技術發展方向之一。晶圓級封裝作為一種新型封裝形式,其制備過程同樣需要基于鍵合、減薄、TSV等封裝技術和設備。 晶圓級封裝最主要的發展趨勢是由晶圓級向板級發展:為了追求更高的生產效率進而降低成本,晶圓級封裝從傳統的以200 mm/300 mm晶圓形式封裝向長方形板級封裝發展,長方形基板尺寸從300 mm×300 mm、457 mm×610 mm、510 mm×515 mm提升至600 mm×600 mm。從設備角度來說,主要的挑戰在于基板形狀的變化,很多基于圓形基板的設備(如旋轉涂膠設備)等,需要做適應性改造。目前韓國三星電機(SEMCO)和納沛斯(Nepes)公司都在開展板級封裝設備的研發。

TSV工藝及設備技術在持續提升中,主要挑戰和發展方向包括:高密度、高深寬比刻蝕、絕緣層和金屬層的低溫工藝、高速通孔填充、持續降低成本等。 (5)晶圓級封裝(WLP)。晶圓級封裝是在晶圓上直接進行裸芯片封裝,再切割形成獨立的芯片。晶圓級封裝可減少封裝材料及工序,同時具有輕薄短小的特點,是封裝技術發展方向之一。晶圓級封裝作為一種新型封裝形式,其制備過程同樣需要基于鍵合、減薄、TSV等封裝技術和設備。 晶圓級封裝最主要的發展趨勢是由晶圓級向板級發展:為了追求更高的生產效率進而降低成本,晶圓級封裝從傳統的以200 mm/300 mm晶圓形式封裝向長方形板級封裝發展,長方形基板尺寸從300 mm×300 mm、457 mm×610 mm、510 mm×515 mm提升至600 mm×600 mm。從設備角度來說,主要的挑戰在于基板形狀的變化,很多基于圓形基板的設備(如旋轉涂膠設備)等,需要做適應性改造。目前韓國三星電機(SEMCO)和納沛斯(Nepes)公司都在開展板級封裝設備的研發。

-

晶圓

+關注

關注

52文章

4848瀏覽量

127808 -

封裝

+關注

關注

126文章

7789瀏覽量

142734 -

TSV

+關注

關注

4文章

108瀏覽量

81444

原文標題:半導體工藝裝備現狀及發展趨勢(中)

文章出處:【微信號:閃德半導體,微信公眾號:閃德半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

先進封裝中互連工藝凸塊、RDL、TSV、混合鍵合的新進展

開啟高性能芯片新紀元:TSV與TGV技術解析

HBM:突破AI算力內存瓶頸,技術迭代引領高性能存儲新紀元

TSV 制程關鍵工藝設備技術及發展

基于兩步刻蝕工藝的錐形TSV制備方法

TSV與異構集成技術的前沿進展與趨勢展望

一文詳解硅通孔技術(TSV)

TSV工藝及設備技術

TSV工藝及設備技術

評論