眾所周知,***作為芯片生產過程中的最主要的設備之一,其重要性不言而喻。

先進的制程工藝完全依賴于先進的***設備,比如現階段臺積電最先進的第二代 3nm 工藝,離不開 EUV ***。

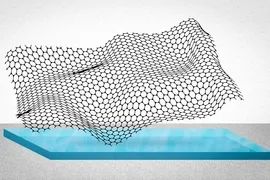

然而,前不久麻省理工學院(MIT)華裔研究生朱家迪突破了常溫條件下由二維(2D)材料制造成功的原子晶體管,每個晶體管只有 3 個原子的厚度,堆疊起來制成的芯片工藝將輕松突破 1nm。

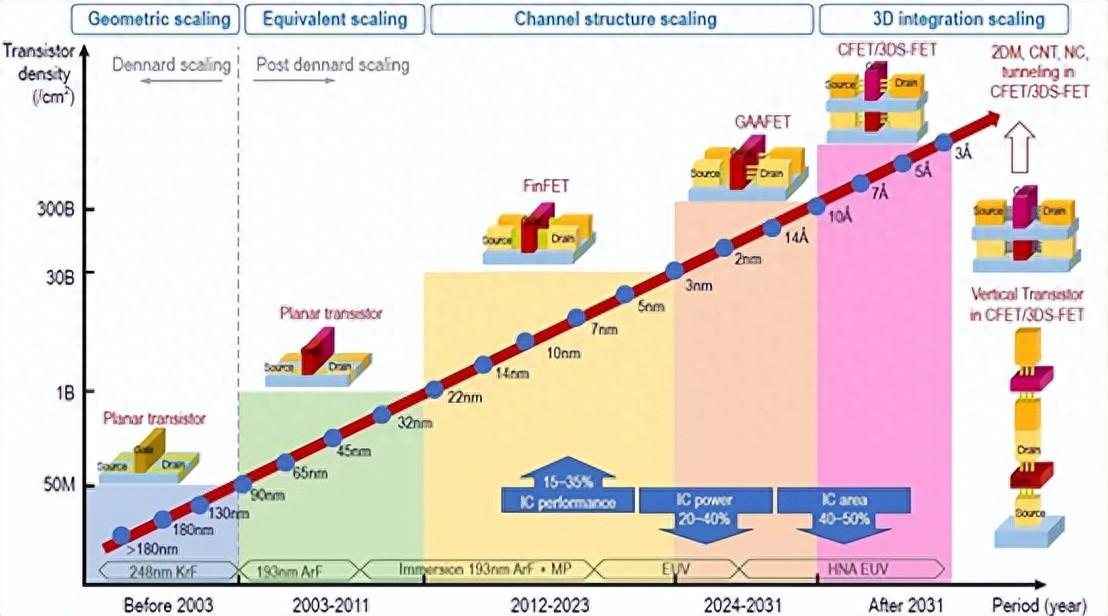

目前的半導體芯片都是在晶圓上通過光刻/蝕刻等工藝加工出來的三維立體結構,所以堆疊多層晶體管以實現更密集的集成是非常困難的。

而且,現在先進制程工藝的發展似乎也在 1~3nm 這里出現了瓶頸,所以不少人都認為摩爾定律到頭了。

但是由超薄 2D 材料制成的半導體晶體管,單個只有 3 個原子的厚度,可以大量堆疊起來制造更強大的芯片。

正因如此,麻省理工學院的研究人員研發并展示了一種新技術,可以直接在硅芯片上有效地生成二維過渡金屬二硫化物 (TMD) 材料層,以實現更密集的集成。

但是,直接將 2D 材料生成到硅 CMOS 晶圓上有一個問題,就是這個過程通常需要約 600 攝氏度的高溫,但硅晶體管和電路在加熱到 400 攝氏度以上時可能會損壞。

這次麻省理工學院(MIT)華裔研究生朱家迪等人的研究成果就是,開發出了一種不會損壞芯片的低溫生成工藝,可直接將 2D 半導體晶體管集成在標準硅電路之上。

此外,這位華裔研究生的新技術還有兩個優勢:擁有更好的工藝+減少生成時間。

之前研究人員是先在其他地方生成 2D 材料,然后將它們轉移到晶圓上,但這種方式通常會導致缺陷,進而影響設備和電路的性能,而且在轉移 2D 材料時也非常困難。

相比之下,這種新工藝會直接在整個 8 英寸晶圓上生成出光滑、高度均勻的材料層。

其次就是能夠顯著減少生成 2D 材料所需的時間。以前的方法需要超過一天的時間來生成 2D 材料,新方法則將其縮短到了一小時內。

“使用二維材料是提高集成電路密度的有效方法。我們正在做的就像建造一座多層建筑。如果你只有一層,這是傳統的情況,它不會容納很多人。但是隨著樓層的增加,大樓將容納更多的人,從而可以實現驚人的新事物。”

朱家迪在論文中這樣解釋,“由于我們正在研究的異質集成,我們將硅作為第一層,然后我們可以將多層 2D 材料直接集成在上面。”

隨著 ChatGPT 的興起,帶動了人工智能產業的蓬勃發展,AI 的背后就需要強大的硬件算力支持,也就是芯片。

該技術不需要***就可以使芯片輕松突破 1nm 工藝,也能大幅降低半導體芯片的成本,如果現階段的***技術無法突破 1nm 工藝的話,那么這種新技術將從***手中拿走接力棒,屆時***也將走進歷史~

審核編輯 :李倩

-

芯片

+關注

關注

453文章

50393瀏覽量

421786 -

半導體

+關注

關注

334文章

27004瀏覽量

216269 -

晶體管

+關注

關注

77文章

9634瀏覽量

137844

原文標題:光刻機將成為歷史!麻省理工華裔研究出 2D 晶體管,輕松突破 1nm 工藝!

文章出處:【微信號:robotqy,微信公眾號:機械自動化前沿】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MOSFET晶體管的工藝制造流程

麻省理工學院研發全新納米級3D晶體管,突破性能極限

麻省理工學院推出新型機器人訓練模型

CMOS晶體管的尺寸規則

NMOS晶體管和PMOS晶體管的區別

2D多鰭FETs的高密度集成,搭臺引導外延的科技突破!

GaN晶體管和SiC晶體管有什么不同

微電子所在《中國科學:國家科學評論》發表關于先進CMOS集成電路新結構晶體管的綜述論文

《麻省理工科技評論》洞察與思特沃克發布最新報告

麻省理工與Adobe新技術DMD提升圖像生成速度

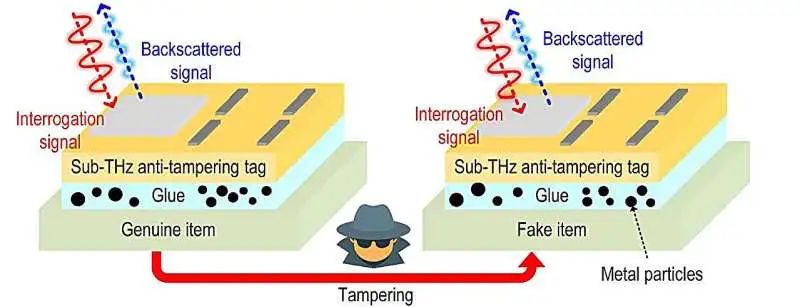

麻省理工學院開發出新的RFID標簽防篡改技術

麻省理工華裔研究出2D晶體管,輕松突破1nm工藝!

麻省理工華裔研究出2D晶體管,輕松突破1nm工藝!

評論