寫在前面

本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。在FPGA和ASIC設計中,時鐘信號的好壞很大程度上影響了整個系統的穩定性,本文主要介紹了數字設計中的非理想時鐘的偏差來源與影響。

理想時鐘

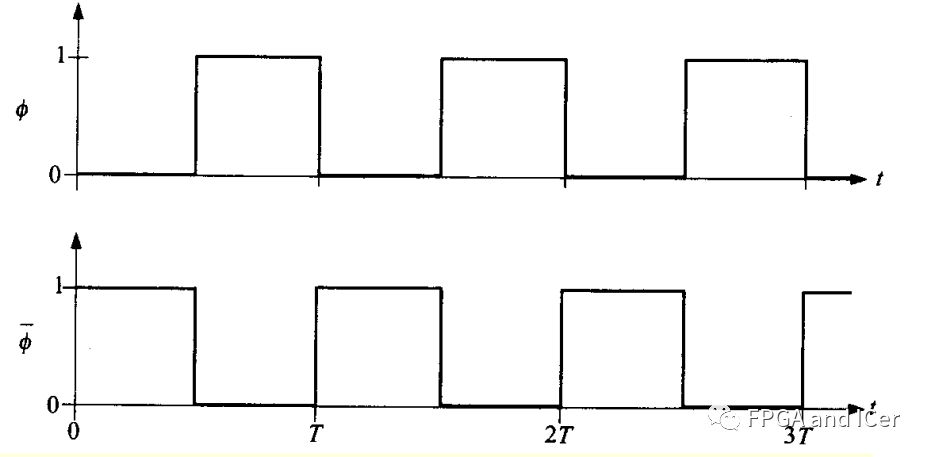

在數字設計中的理想時鐘如下圖所示:

理想時鐘

理想時鐘的特點如下:

- 時鐘無重疊: 任意時刻下, Φ 與Φ非的與恒為零;

- 全軌輸出: VDD - V(Φ) = V (Φ非);

- 時鐘無延遲、無偏斜、無抖動 。

非理想性時鐘

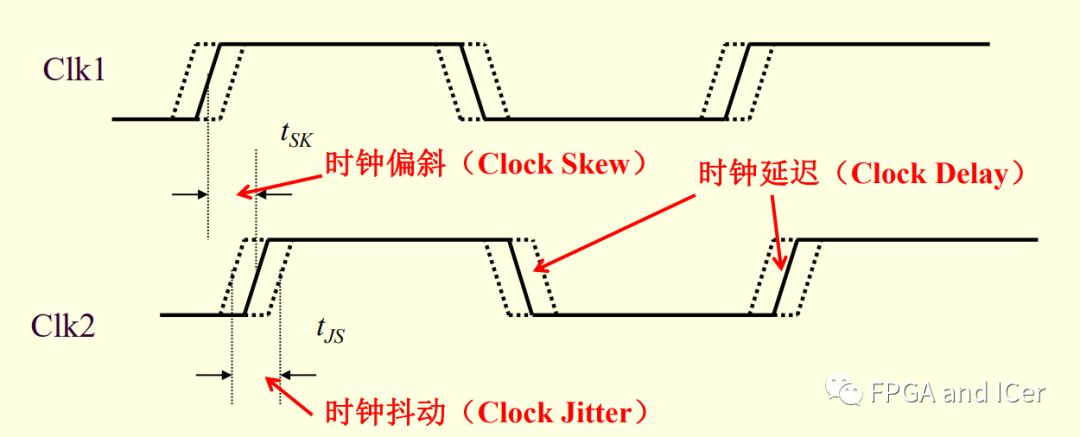

在數字設計中的非理想時鐘如下圖所示,和理想時鐘相對立,如果不滿足上述的理想時鐘的相關特點,可認為其實一個非理想時鐘。

非理想性時鐘

對上圖進行分析,假設CLK1、CLK2是同一個時鐘樹下的不同時鐘,此時,兩個時鐘邊沿的時間差就為時鐘偏斜,同時,對于某一個時鐘,在時鐘變化邊沿時,會有一定的隨機性,所以這里隨機的時鐘周期變化叫做時鐘抖動。

假設CLK1是CLK2的前級時鐘,所以上圖中兩個時鐘的邊沿的時間差即為時鐘延遲。

在上圖中其實不能很準確體現出時鐘延遲和時鐘偏斜的概念區別,貼出另外一個圖以供參考:

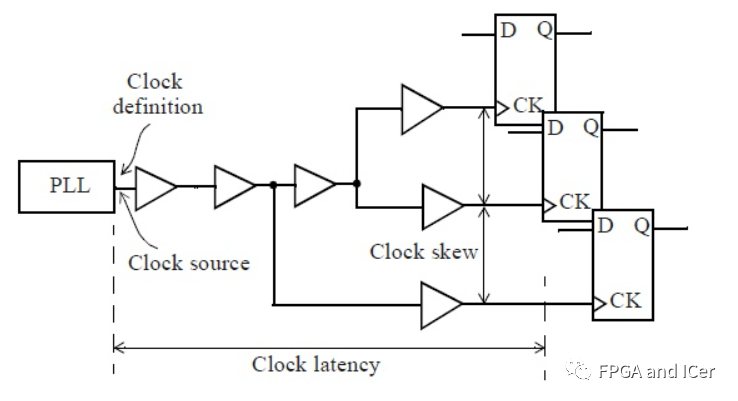

在下圖中很容易理解時鐘延遲和時鐘偏斜的概念:

- 時鐘延遲(clock latency)是指從時鐘源到終點所花費的總時間。

- 時鐘偏斜(clock skew)是指到達不同時鐘樹終點的時間差。

時鐘偏斜主要來自時鐘在空間上的不期望變化,時鐘延遲和時鐘抖動主要來自時鐘在時間上的不期望變化。

時鐘延遲(clock latency)

時鐘延遲 (clock latency)是指從時鐘源到終點所花費的總時間,主要針對的是一個時鐘,從時鐘源端輸出到所驅動的器件的時鐘輸入端的時間延遲。

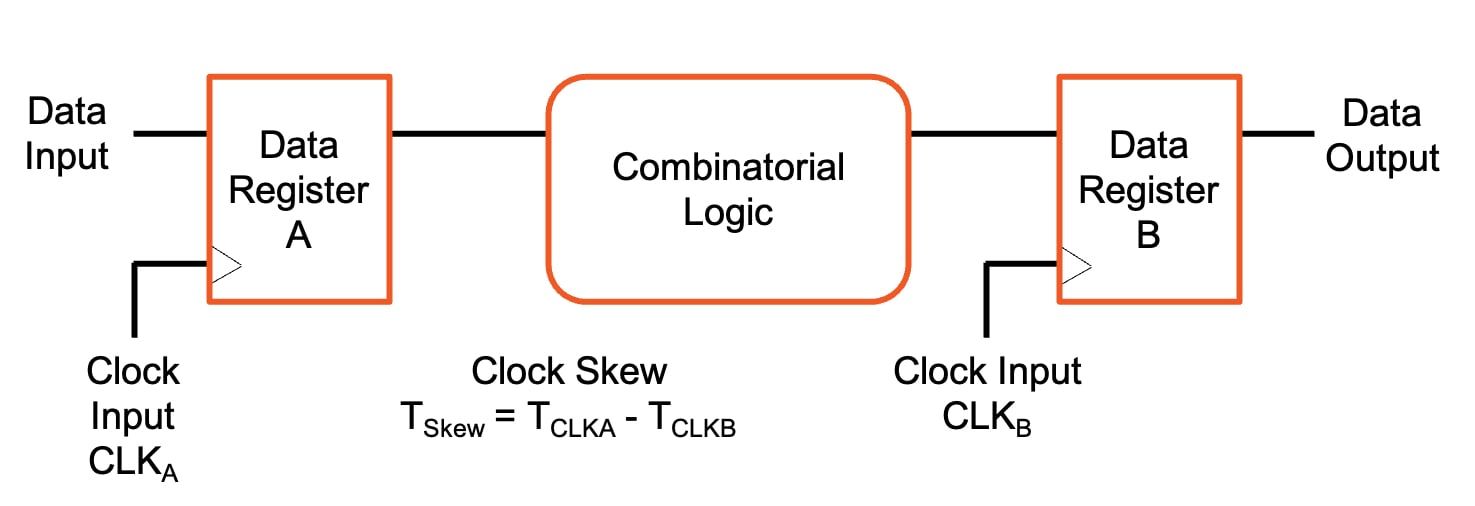

時鐘偏斜(clock skew)

時鐘偏斜(clock latency)是一對物理時鐘的標稱時間差與實際時間差之間的區別。理想情況下,時鐘應同時到達系統中所有的鐘控元件(鎖存器、觸發器、存儲器和動態門等),這樣系統才有一個共同的參考時間。實際中,時鐘到達各點的時間稍微有些差別,這個差別就叫 時鐘偏斜 。

兩個不同時鐘的時鐘延遲,就是時鐘偏斜。

時鐘偏斜發生在兩個時鐘信號之間,一般不會引起電路實際時鐘周期的變化,只會 導致時鐘相位的偏移 ;時鐘抖動可以發生在一個時鐘信號自身,會 引起時鐘周期的變化 。

時鐘偏斜與時鐘抖動統稱為 時鐘偏差 ,二者之和也叫 時鐘不確定性(uncertainty) 。邊沿之間的時鐘抖動有時也被歸于與時間相關的時鐘偏斜。

時鐘抖動(clock jitter)

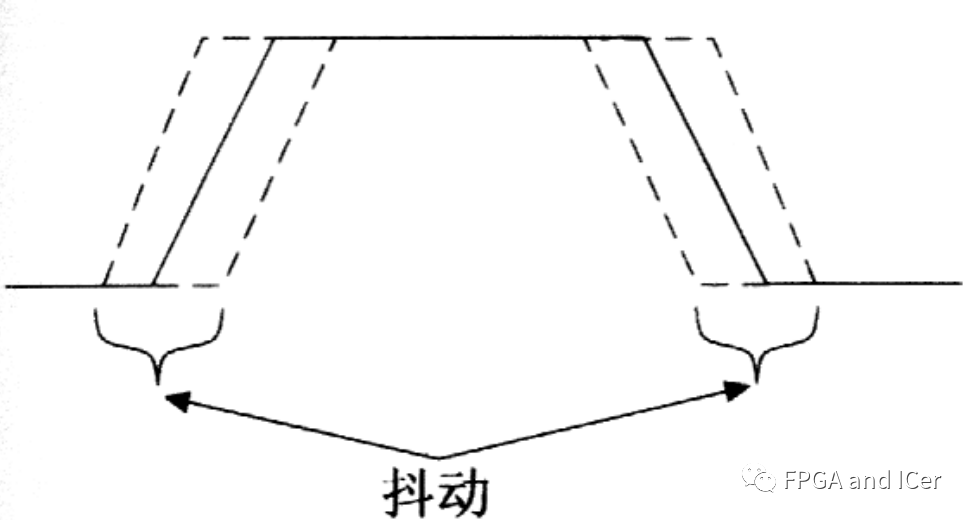

時鐘抖動(clock jitter) 是指芯片的某一個給定點上時鐘邊沿發生暫時的隨機變化,會導致時鐘周期的縮短或加長。

時鐘抖動

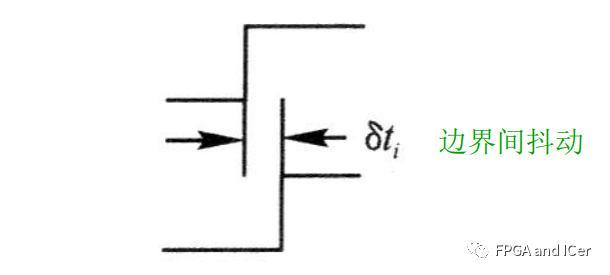

邊界間抖動(edge-to-edge) :時鐘邊沿相對與理想時鐘邊沿的最大變化值,實際上是隨時間變化的時鐘偏斜。

邊界間抖動

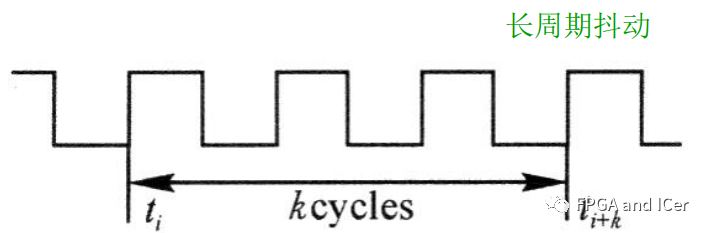

長周期抖動(k-cycle) :數個周期后邊沿之間的最大變化值,主要影響芯片間的時序同步,也叫絕對抖動。

長周期抖動

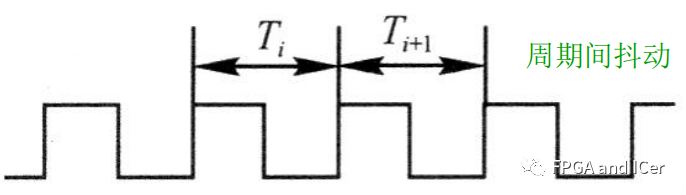

周期間抖動(cycle-to-cycle) :相鄰時鐘周期間的時變偏離,主要影響芯片內時序同步,也叫相對抖動。

周期間抖動

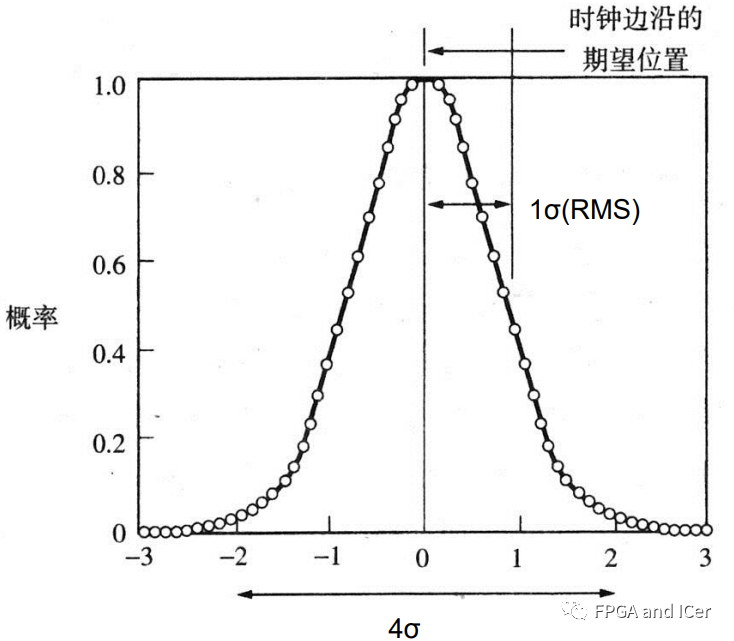

隨機抖動(random jitter) :由器件和導線的固有噪聲(如熱噪聲) 所致,為高斯分布,用均方根值(RMS)表征,無法預估。

隨機絕對抖動的高斯分布

確定性抖動 (deterministic jitter) :確定性抖動由非理想傳輸效應、串擾、電源浪涌等所致,為非高斯分布,用峰峰值表征,可以預估。

在邏輯綜合前,常采用理想時鐘(邏輯時鐘)+預設偏差的方式來模擬真實時鐘;在物理設計時,完成實際時鐘(物理時鐘)的設計,其偏差必須滿足系統要求。

- 邏輯時鐘(logical clock) :沒有時鐘偏斜的理想時鐘,邏輯設計者在用硬件描述語言描述系統行為時使用。

- 物理時鐘(physical clock) :帶有時鐘偏斜的實際時鐘,為了使系統達到預期行為,設計者不得不在時鐘偏差、功耗、金屬化資源利用率和設計代價之間尋求均衡。

- 全局時鐘(global clock) :為整個系統提供基準的單一時鐘。

布線對時序的影響

同一個時鐘下,驅動不同的觸發器,都需要在實際設計時候都需要進行布線,所以不同的觸發器之間布線長短也會有一定差異。

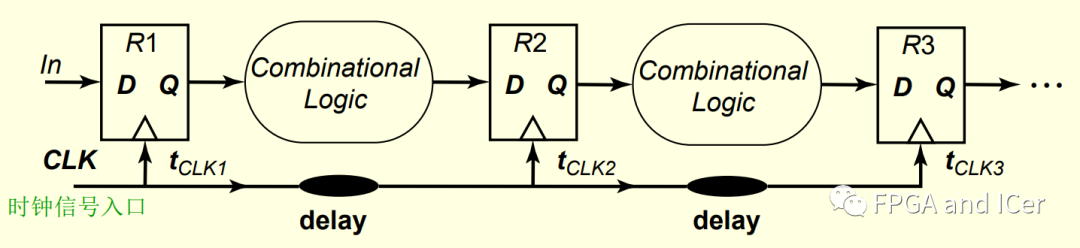

布線方向的影響:正偏差

時鐘布線方向與數據通過流水線方向一致會使得時鐘正偏差,也即,tskew > 0 。

好處:可采用更短的時鐘周期從而得到更高的時鐘頻率,有利于提高數據通過率。

壞處:需采用更長的保持時間,以免出現冒險競爭。

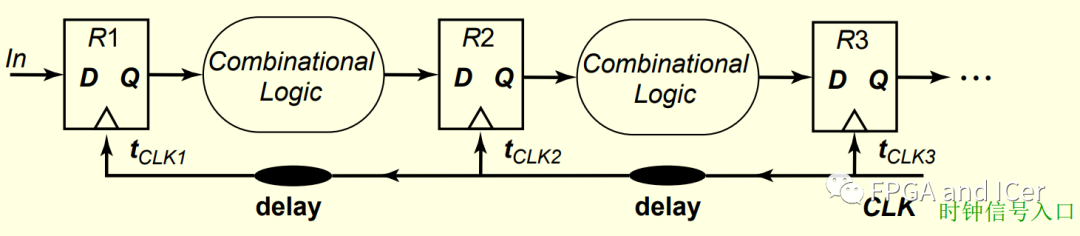

布線方向的影響:負偏差

時鐘布線方向與數據通過流水線方向相反會使得時鐘負偏差,也即,tskew < 0 。

好處:冒險競爭不易發生,提高了電路的健壯性。

壞處:加長了最小時鐘周期從而降低了時鐘頻率,不利于提高數據通過率。

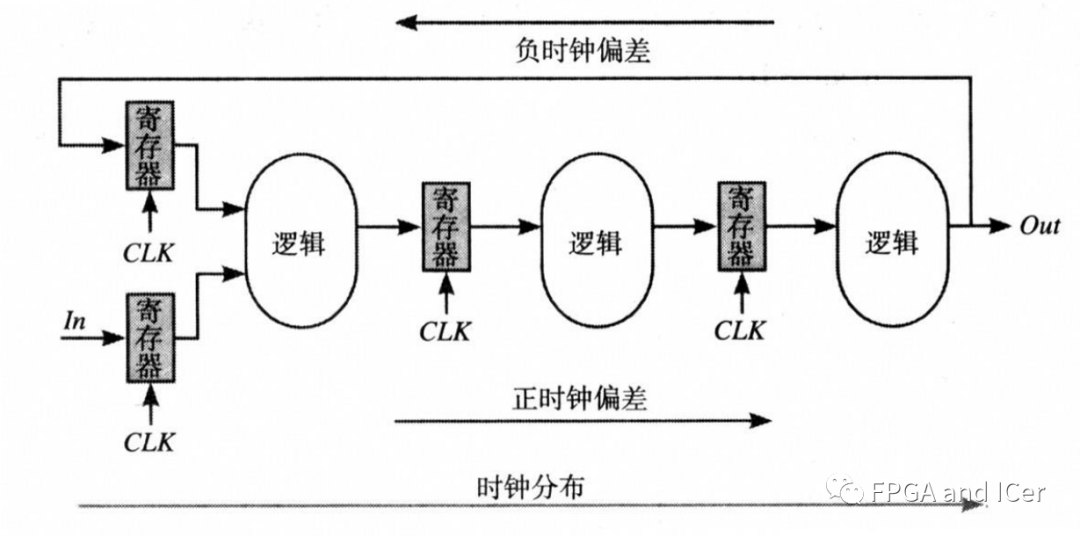

布線方向的影響:雙向電路

時鐘布線方向與數據通過流水線方向可能相同也可能相反,從而使正負偏差都存在。

一個較為理想的設計目標是使正、負偏差都很小,零偏差最好。

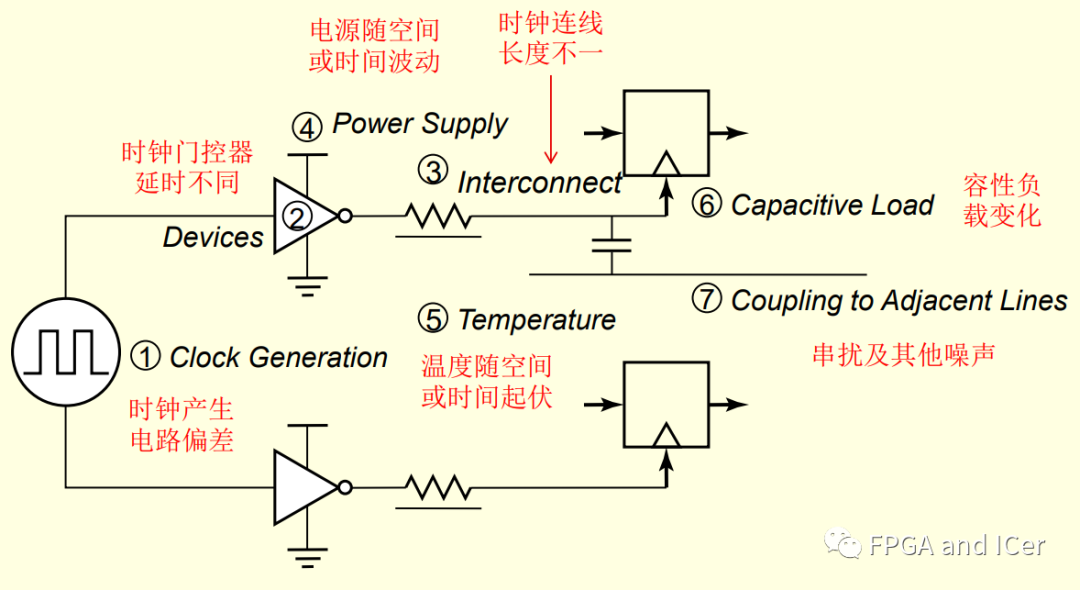

時鐘偏差的來源

時鐘偏差的來源大致如下圖所示:

時鐘偏差分析

結合上圖中的引起時鐘偏差來源,大致可對時鐘偏差進行分類,系統偏差、隨機(random)偏差、漂移(drift)偏差、抖動(jitter)偏差,不同類型的偏差的原因如下:

- 系統(systematic)偏差:時鐘產生器、時鐘門控器、電容負載、互連線的偏差,可預估并通過設計來糾正。

- 隨機(random)偏差:工藝離散引起元器件和互連線參數的隨機變化,無法預估,但可以測試,并用可校準延時元件來補償。

- 漂移(drift)偏差:與時間有關的環境因素(如溫度隨時間變化、溫度的空間梯度變化)變化所致,也可補償,但需實時。

- 抖動(jitter)偏差:高頻環境變化(如電源浪涌、串擾)導致的電路延時隨時間和空間的變化,最難以防范,因補償電路來不及對它進行響應。

下面針對其中幾個原因進行舉例分析。

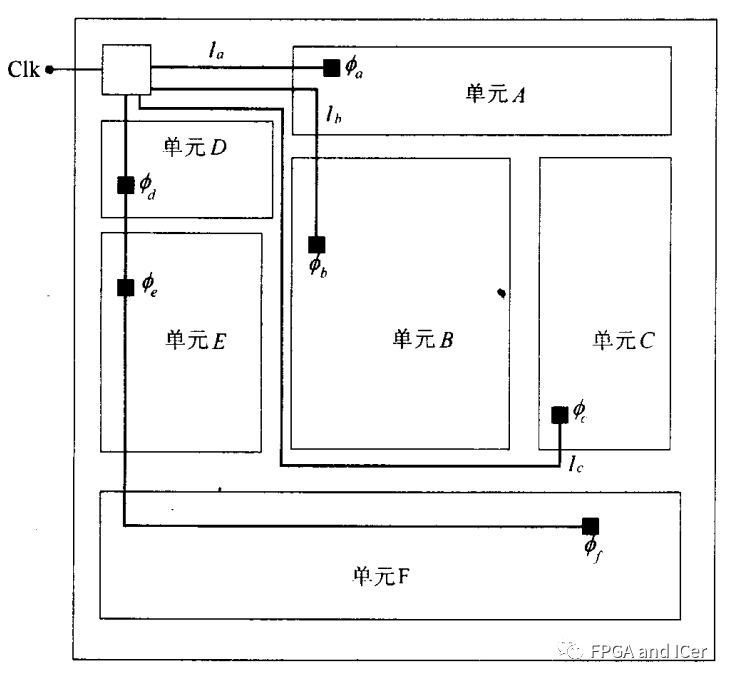

時鐘線長度不一引入偏差

由于時鐘在驅動不同單元時,不同單元布局分布在不同區域,所以使得時鐘扇出的信號進行實際布線的長度長短不一,從而引起了時鐘偏差,如下圖所示,La和Lb長度不同,所以時鐘對應到單元A和單元B的時鐘延遲不同,使兩個單元的時鐘存在偏斜。

電源變化引入偏差

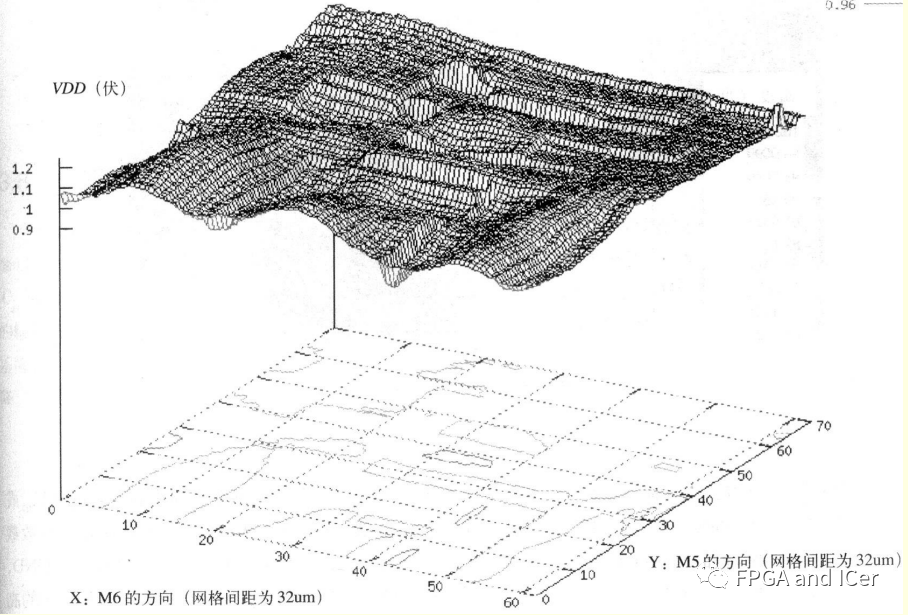

Itanium 2 處理器芯片電源電壓的空間分布:1.2V標稱電源電壓下的最大變化為±100mV,由此導致的延時變化為13%/100mV。

Itanium 2電源電壓的空間分布

溫度變化引入偏差

對Itanium 2的仿真結果表明,溫 度在芯片上的非 均勻分布達到 20℃時,會導致 1.5%的延時變化。

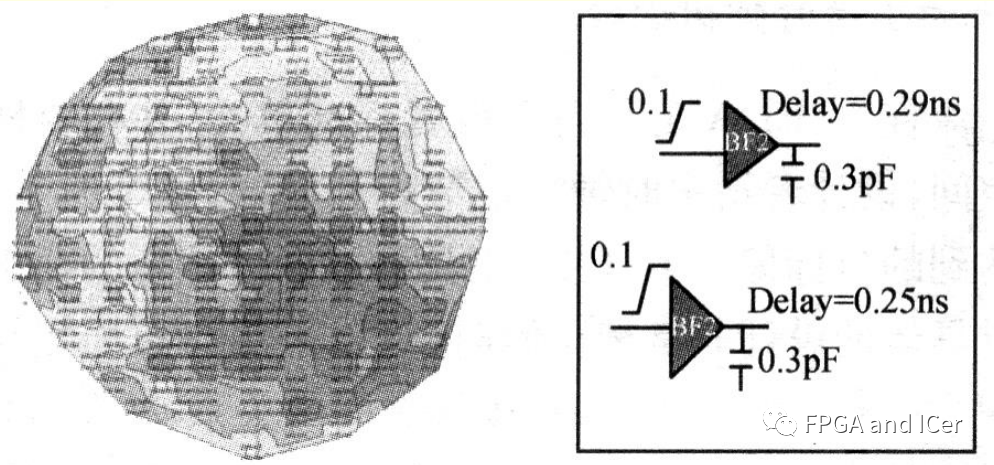

工藝變化引入偏差

工藝上變化也會引入時鐘的偏差,如溝道長度、閾值電壓和片上誤差。

溝道長度:Itanium 2的標稱值為180nm,工藝離散導致的偏差可能高達±12.5nm,這會導致±10%的延時變化。

閾值電壓:0.18um工藝下,小nMOS管(W<12.5um)、小pMOS管、 大nMOS管、大pMOS管的標準偏差分別為16.8、14.6、7.9、3.5mV, 這會導致一個標準偏差為2%的延時分布。

片上誤差 (on-chip variation, OCV)空間分布,相同的緩沖器單元因所處芯片位置 不同而產生的延遲誤差。

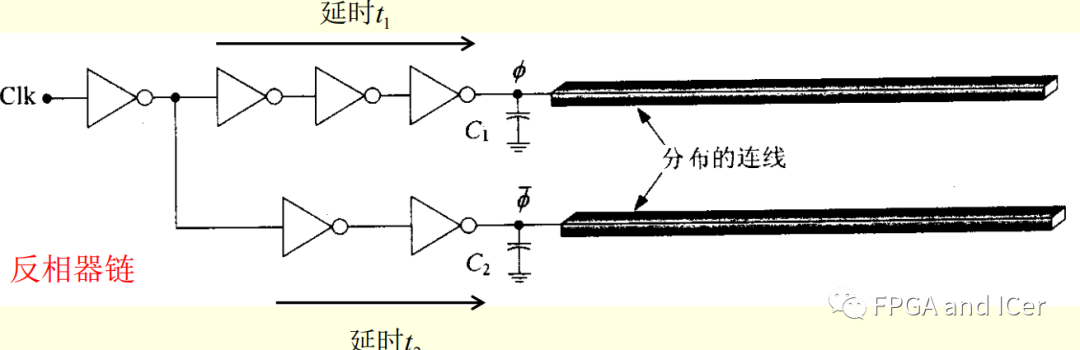

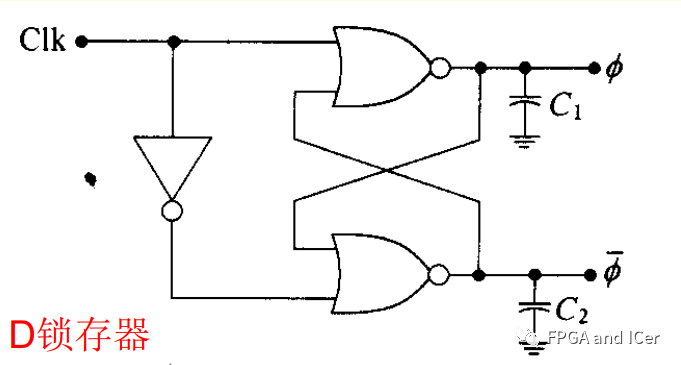

門控器引入偏差

反相器鏈的延遲差以及C1與C2的差會導致時鐘偏斜|t2 -t1 | 。采用邏輯努力技術合理設計反相器鏈的級數及門間面積比,可減少乃至消除此偏差。

下圖的D鎖存器的時鐘偏斜來源于反相器的延遲以及C1與C2的差。通過調整兩個NOR2門的面積 比,可對時鐘偏斜進行補償。

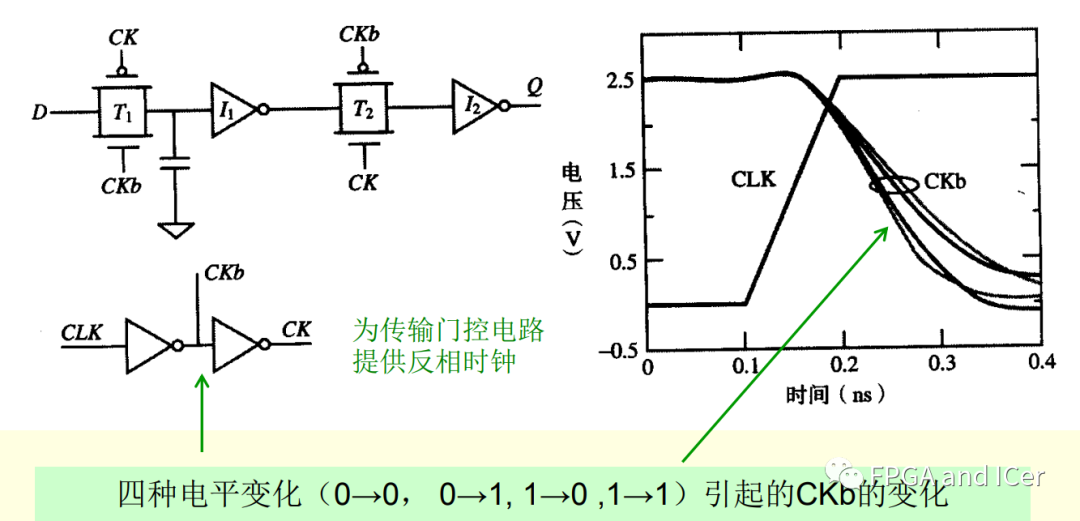

負載變化引入偏差

負載變化會引入時鐘偏差,柵電容與所加電壓有關,時鐘負載與鎖存器/寄存器的當前狀態及下一個狀態有關。如下圖所示,不同電平變化會影響時鐘負載的微小變化。

總結

- 時鐘延遲(clock latency) 是指從時鐘源到終點所花費的總時間。時鐘偏斜(clock skew) 是指到達不同時鐘樹終點的時間差。時鐘抖動(clock jitter) 是指芯片的某一個給定點上時鐘邊沿發生暫時的隨機變化,會導致時鐘周期的縮短或加長。

- 時鐘偏斜 主要來自時鐘在空間上的不期望變化,時鐘延遲和時鐘抖動 主要來自時鐘在時間上的不期望變化。

- 時鐘偏斜發生在兩個時鐘信號之間,一般不會引起電路實際時鐘周期的變化,只會 導致時鐘相位的偏移 ;時鐘抖動可以發生在一個時鐘信號自身,會 引起時鐘周期的變化 。

- 時鐘偏斜與時鐘抖動統稱為 時鐘偏差 ,二者之和也叫 時鐘不確定性(uncertainty) 。邊沿之間的時鐘抖動有時也被歸于與時間相關的時鐘偏斜。

- 布線方向會對時序造成正負偏差的影響,一個較為理想的設計目標是使正、負偏差都很小,零偏差最好。

- 時鐘偏差分為,系統偏差、隨機(random)偏差、漂移(drift)偏差、抖動(jitter)偏差,不同偏差的原因不同,可通過合理的設計將相應的影響規避或影響降至最低。

-

驅動器

+關注

關注

52文章

8168瀏覽量

146053 -

FPGA設計

+關注

關注

9文章

428瀏覽量

26489 -

ASIC設計

+關注

關注

0文章

33瀏覽量

10649 -

VDD

+關注

關注

1文章

311瀏覽量

33123 -

時鐘信號

+關注

關注

4文章

445瀏覽量

28512

發布評論請先 登錄

相關推薦

一文帶你深度了解大型多GHz時鐘樹中的相位偏差

BUFGMUX定時時鐘偏差太大

如何使用DCM減少時鐘偏差?如何使用DCM來增加時鐘?

如何通過PLL修復時鐘偏差?

時鐘網格與時鐘樹設計方法對比研究

大型時鐘樹設計時的相位偏差問題及方法建設

什么是時鐘偏斜?了解時鐘分配網絡中的時鐘偏斜

【世說知識】一文帶你深度了解大型多GHz時鐘樹中的相位偏差

談談非理想時鐘的時鐘偏差

談談非理想時鐘的時鐘偏差

評論