鎖相環(PLL),作為Analog基礎IP、混合信號IP、數字系統必備IP,廣泛存在于各類電子產品中。

本文以SoC中的PLL為例,對PLL規格及架構分別進行研究和確定。

先進行規格研究:

典型的PLL規格如下:

| 參數 | 示例 |

|---|---|

| 參考時鐘頻率 | 13MHz~76.8MHz |

| 輸出時鐘頻率 | 100MHz~2GHz |

| 鎖定時間 | <100uS |

| Period Jitter RMS | <2ps |

| 輸出時鐘duty cycle | 40%~60% |

| 功耗 | <5mA |

| 輸出時鐘頻率精度 | <±300ppm |

對于SoC中的數字系統,CPU、GPU、ISP、NPU等,PLL規格分別如下:

1)參考時鐘頻率

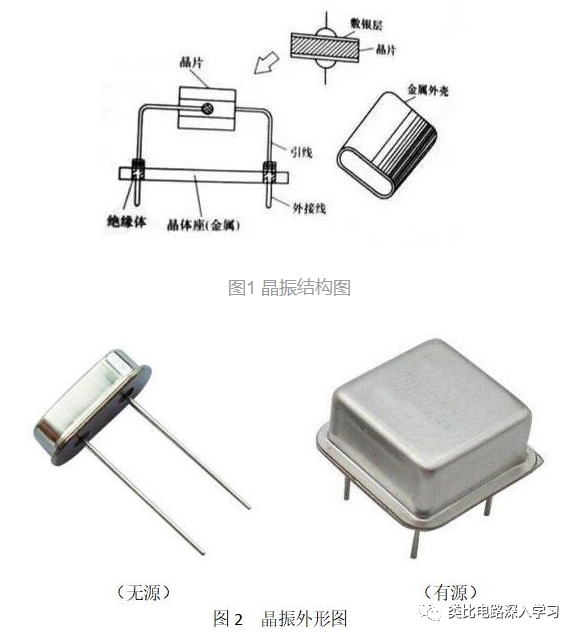

PLL參考時鐘一般來自于晶振(有源晶振或無源晶振),或者來自于系統中PCB上的其它芯片;

晶振的頻率選擇一般是,價格、精度要求、phasenoise需求、頻偏要求、溫度系數等因素折中考慮;

本設計僅考慮SoC數字系統,因此參考時鐘頻率考慮兼容常用的頻率,13MHz~76.8MHz,頻率精度<±300ppm;

2)輸出時鐘頻率

輸出時鐘頻率的下限,系統一般沒有要求,因為數字電路可以通過分頻器分頻實現;而頻率的上限在芯片規格定義中有規定,一般由數字IP spec、工藝、數字后端物理實現綜合決定。

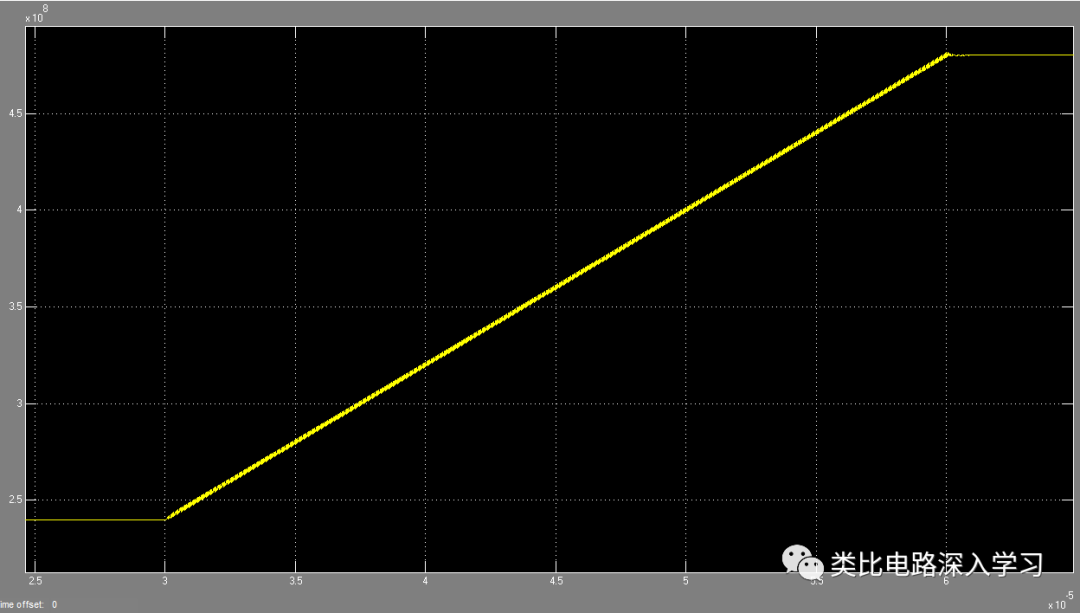

如果是給CPU提供時鐘,如果系統需要支持DVFS,那么PLL需要支持線性調頻;

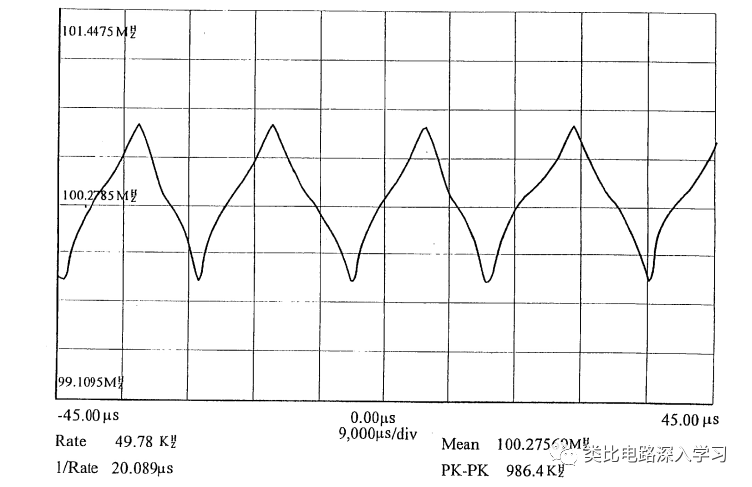

如果是給外設、接口提供時鐘,那么PLL可能需要支持展頻。

3)鎖定時間

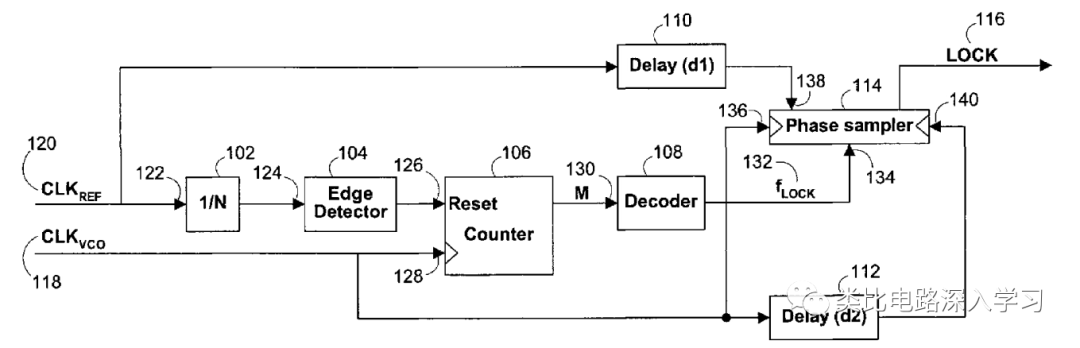

數字系統一般對于鎖定時間沒有嚴格的要求,Ring PLL一般鎖定時間都在200us以內,可以采用reference頻率數counter的“硬等”方式。更合理的方式是增加鎖定檢測電路lock detect,輸出標志鎖定的數字信號。

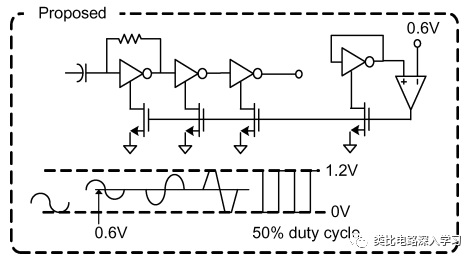

4)duty cycle

輸出時鐘占空比,如果直接從VCO送出來的時鐘,占空比會在40%~60%。為了得到45%~55%占空比時鐘,可以采用DCC、self-bias、二分頻等處理。

5)功耗

SoC PLL由于性能要求不高,其消耗總電流約為幾mA,對于數字系統而言占比很小。所以通常不會有特殊要求。

6)RMS Jitter

數字系統關心的是哪種jitter?jitter數值應該如何確定?

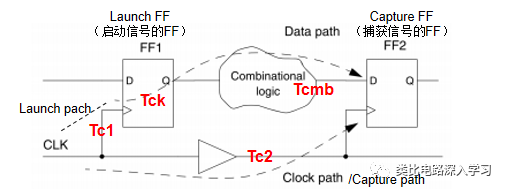

我們知道數字后端設計STA的兩個主要的指標,setup和hold。

本質是保證DFF的正常功能PVT下仍有一定的margin,

a) 上一個時鐘沿同步過來的數據,必須發生在下一個時鐘沿之前;

b) lauch DFF在當前時鐘沿得到的數據,必須發生在capture DFF當前時鐘沿之后。

從a)和b)可以得知,數字系統對于時鐘的要求是,相鄰時鐘沿最小的變化,也就是時鐘周期period最小的變化。

因此數字系統關心時鐘的jitter類型為Period Jitter,越小越好。

綜上SoC PLL的規格確定如下:

| 參數 | 示例 |

|---|---|

| 參考時鐘頻率 | 13MHz~76.8MHz |

| 輸出時鐘頻率 | 100MHz~2GHz |

| 鎖定時間 | <100uS |

| Period Jitter RMS | <2ps |

| 輸出時鐘duty cycle | 40%~60% |

| 功耗 | <5mA |

| 輸出時鐘頻率精度 | <±300ppm |

下面進行架構研究:

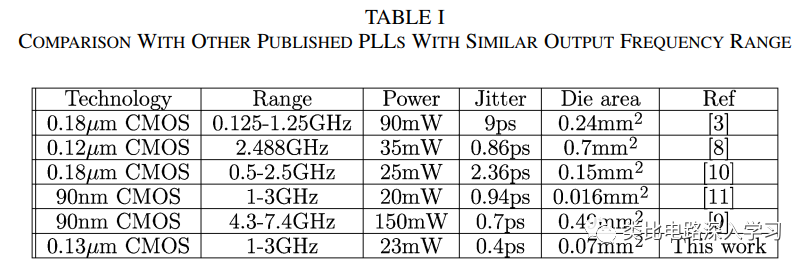

PLL的相位噪聲要求低、需要寬頻率調節范圍、小面積。因此PLL中的VCO采用環形振蕩器的結構,即Ring PLL。

PLL架構分為

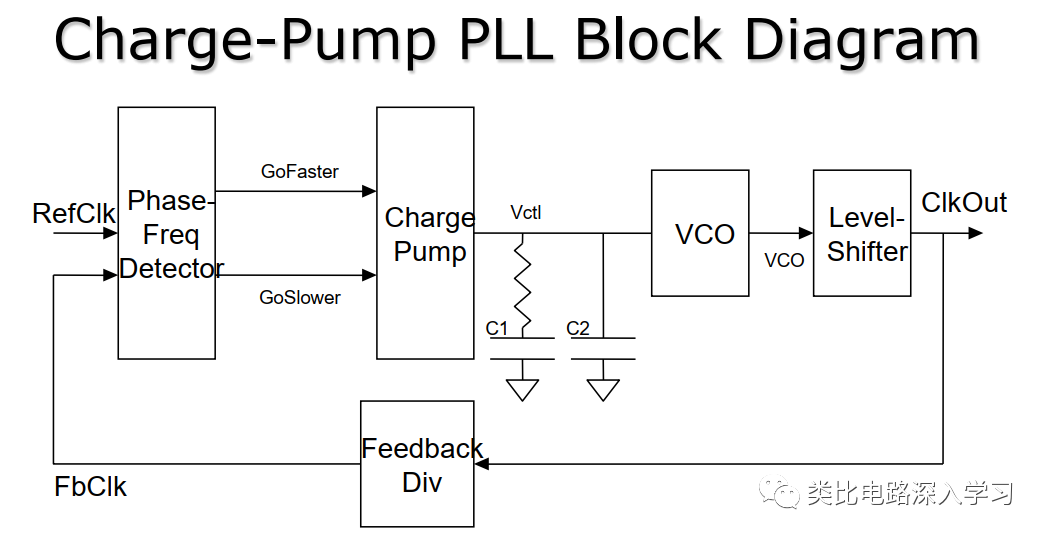

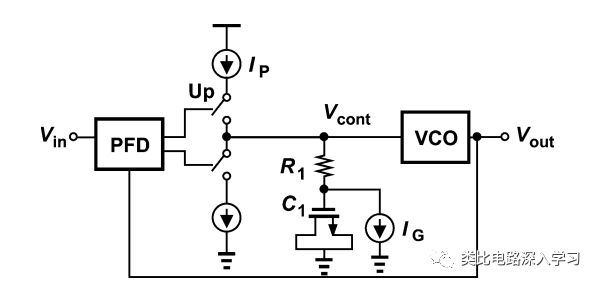

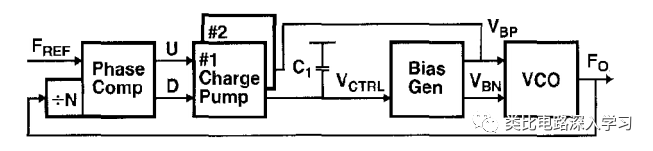

CP PLL(single-path loop filter/dual-path loop filter)

Self-bias PLL

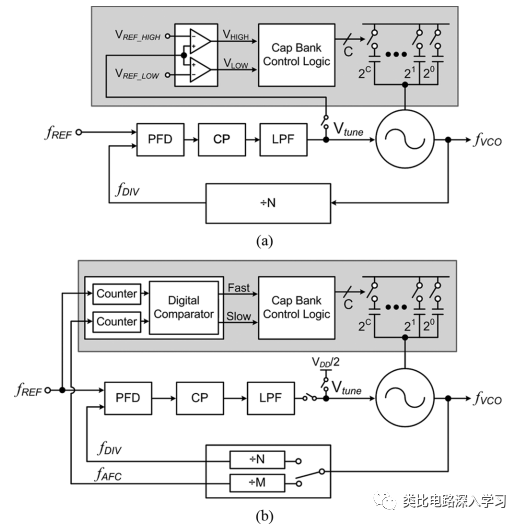

coarse/fine PLL

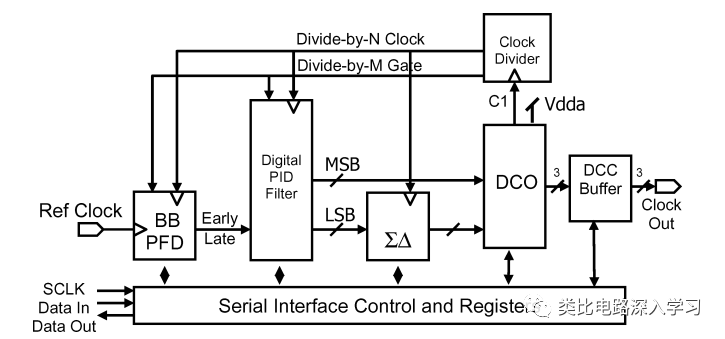

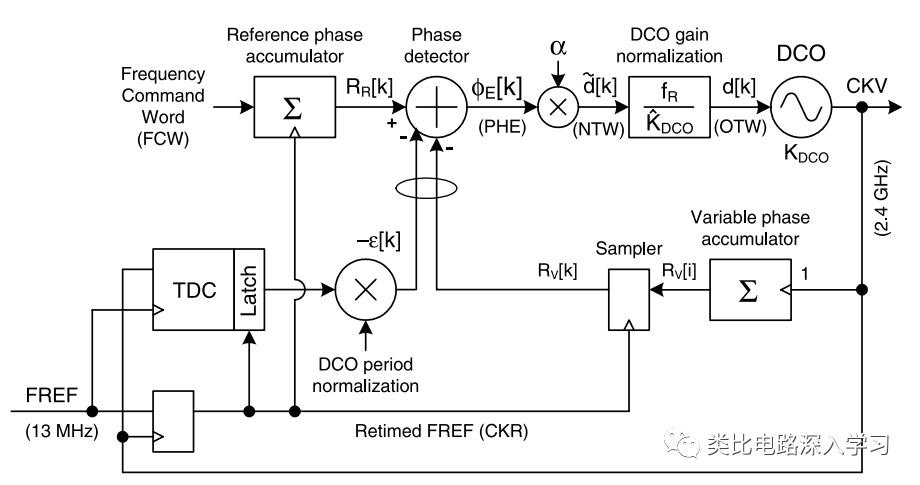

counter-based ADPLL

divider-based ADPLL

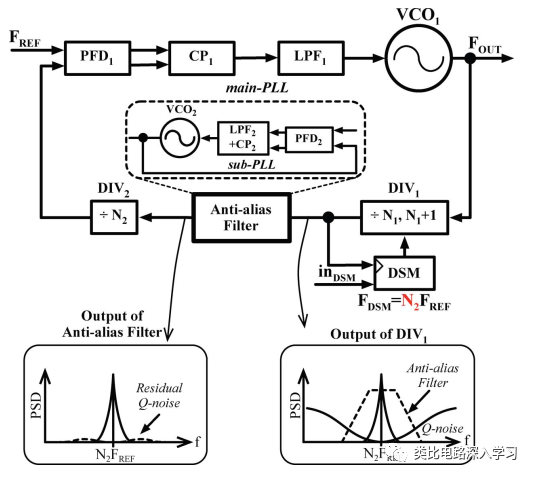

nested-PLL

本文將采用CP PLL(single-path loop filter),即最傳統也是最可靠的結構進行設計。子模塊結構的選擇將在設計中逐步展開。

-

鎖相環

+關注

關注

35文章

583瀏覽量

87697 -

混合信號

+關注

關注

0文章

469瀏覽量

64932 -

soc

+關注

關注

38文章

4122瀏覽量

217952 -

pll

+關注

關注

6文章

775瀏覽量

135052 -

數字系統

+關注

關注

0文章

142瀏覽量

20829

發布評論請先 登錄

相關推薦

LabVIEW鎖相環(PLL)

鎖相環(PLL)電路設計與應用

鎖相環(PLL)規格及架構研究

鎖相環(PLL)規格及架構研究

評論