曾經有一段時間,實際上是幾十年,制造更好的計算機芯片所需要的只是更小的晶體管和更窄的互連。DNA那個時代已經一去不復返了,雖然晶體管會繼續變得更小,但簡單地制造它們已不再是重點。

上周在比利時安特衛普舉行的ITF 2023 世界大會上,研究人員認為,現在保持計算速度呈指數級增長的唯一方法是一種稱為系統技術協同優化 (STCO) 的方案。它能夠將芯片分解成它們的功能組件,為每個功能使用最佳的晶體管和互連技術,并將它們重新拼接在一起以創建一個功耗更低、功能更好的整體。

Imec研發經理Marie Garcia Bardon說:“這將我們引向 CMOS 的新范式。” 正如總部位于比利時的納米技術研究組織所稱,CMOS 2.0 是一個復雜的愿景。但它可能是最實用的前進方式,其中的一部分已經在當今最先進的芯片中得到體現。

我們是怎么到這里的

Imec 研發副總裁Julien Ryckaert說,從某種意義上說,半導體行業在 2005 年之前的幾十年里被寵壞了。在那段時間里,化學家和設備物理學家能夠定期生產更小、功耗更低、速度更快的晶體管,可用于芯片上的每項功能,這將導致計算能力的穩步提高。

但此后不久,輪子開始脫離該計劃。設備專家可以想出出色的新晶體管,但這些晶體管并不能制造出更好、更小的電路,例如構成 CPU 主體的 SRAM 存儲器和標準邏輯單元。作為回應,芯片制造商開始打破標準單元設計和晶體管開發之間的障礙。稱為設計技術協同優化或 DTCO 的新方案導致專門設計用于制造更好的標準單元和存儲器的設備。

但 DTCO 不足以讓計算繼續進行。物理和經濟現實的局限性共同為通用型晶體管的發展設置了障礙。如Imec 的首席工程師Anabela Veloso解釋說,物理限制阻止了 CMOS 工作電壓降低到大約 0.7 伏以下,從而減緩了功耗的進展。轉向多核處理器幫助改善了這個問題一段時間。同時,輸入輸出限制意味著越來越需要將多個芯片的功能集成到處理器上。

因此,除了具有多個處理器內核實例的片上系統 (SoC) 之外,它們還集成了網絡、內存和通常專用的信號處理內核。這些內核和功能不僅具有不同的功率和其他需求,而且它們也無法以相同的速度變得更小。即使是 CPU 的高速緩存 SRAM,也不會像處理器的邏輯那樣快速縮小。

系統技術協同優化

讓事情擺脫困境與技術集合一樣是一種哲學轉變。根據 Ryckaert 的說法,STCO 意味著將片上系統視為功能的集合,例如電源、I/O 和緩存存儲器。“當你開始對功能進行推理時,你會意識到 SoC 不是這種同質系統,只是晶體管和互連,”他說。“它是功能,針對不同的目的進行了優化。”

理想情況下,您可以使用最適合它的工藝技術來構建每個功能。實際上,這主要意味著在自己的硅片或小芯片上構建每個。然后,您可以使用高級 3D 堆疊等技術將它們綁定在一起,這樣所有功能就好像它們在同一塊硅片上一樣。

這種想法的例子已經出現在高級處理器和人工智能加速器中。英特爾的高性能計算加速器 Ponte Vecchio(現在稱為英特爾數據中心 GPU Max)由 47 個小芯片組成,這些小芯片使用兩種不同的工藝構建,分別來自英特爾和臺積電。AMD 已經在I /O 小芯片上使用了不同的技術并在其 CPU 中計算小芯片,它最近開始為計算小芯片的高級高速緩存分離出SRAM 。

Imec 的 CMOS 2.0 路線圖走得更遠。該計劃需要繼續縮小晶體管,將電源和可能的時鐘信號移動到 CPU 的硅片下方,以及更加緊密的 3D 芯片集成。Ryckaert 說:“我們可以使用這些技術來識別不同的功能,分解 SoC,然后重新集成它,從而非常高效。”

晶體管將在未來十年內改變形式,但連接它們的金屬也會改變。最終,晶體管可能是由二維半導體而不是硅制成的堆疊設備。電力傳輸和其他基礎設施可以分層放置在晶體管下方。

持續的晶體管縮放

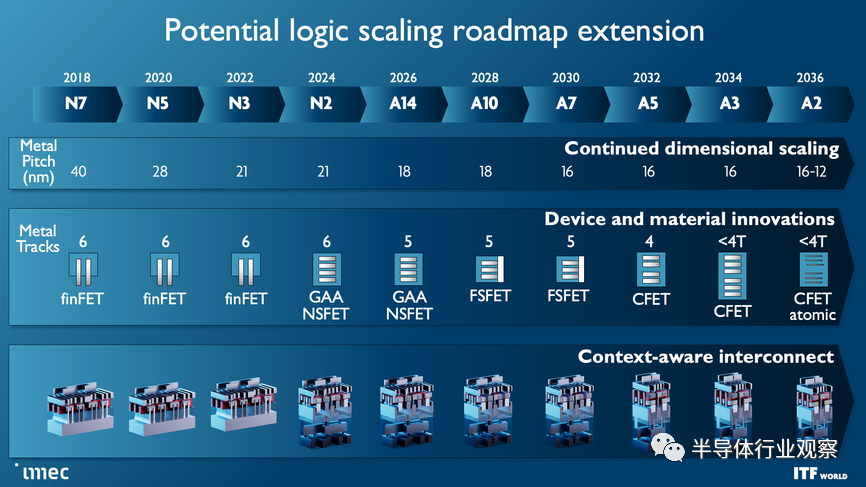

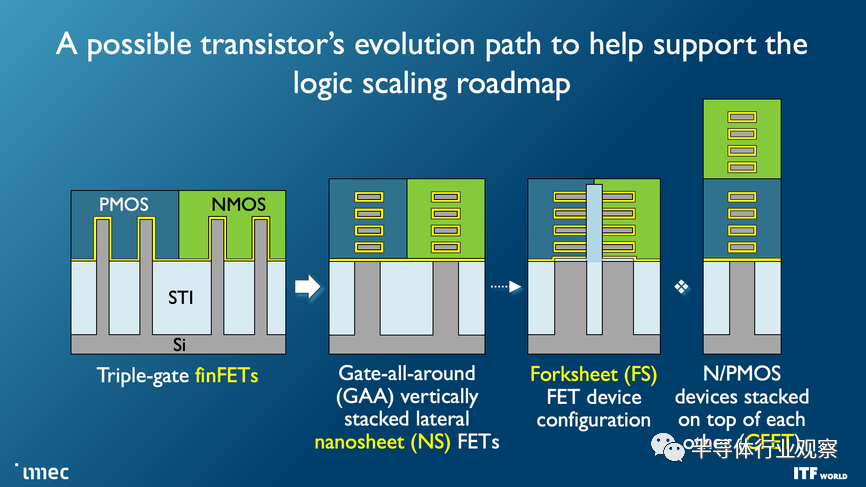

主要芯片制造商已經從為過去十年的計算機和智能手機提供動力的 FinFET 晶體管過渡到一種新的架構,納米片晶體管。最終,兩個納米片晶體管將在彼此之上構建,形成互補的 FET 或 CFET,Velloso 稱其“代表了 CMOS 縮放的終極”。

隨著這些設備按比例縮小和改變形狀,主要目標之一是縮小標準邏輯單元的尺寸。這通常以“軌道高度”來衡量——基本上,可以安裝在單元內的金屬互連線的數量。先進的FinFET和早期的納米片器件是六軌cell。移動到五個軌道可能需要一種稱為 forksheet 的間隙設計,它可以將設備更緊密地擠壓在一起,而不必使它們更小。然后 CFET 會將單元減少到四個軌道或可能更少。

根據 Imec 的說法,芯片制造商將能夠使用ASML 的下一代極紫外光刻技術生產出這一進展所需的更精細的特征。這項稱為高數值孔徑 EUV 的技術目前正在 ASML 建設中,而 Imec 是下一個交付的。增加數值孔徑,一個與系統可以收集光線的角度范圍相關的光學術語,可以產生更精確的圖像。

背面供電網絡

背面供電網絡的基本思想是從硅表面上方移除所有發送電力(而不是數據信號)的互連,并將它們放置在硅表面下方。這應該允許更少的功率損耗,因為功率傳輸互連可以更大且電阻更小。它還為信號傳輸互連釋放了晶體管層上方的空間,可能導致更緊湊的設計。

將來,更多的可能會被轉移到硅片的背面。例如,所謂的全局互連——那些跨越(相對)遠距離以傳輸時鐘和其他信號的互連——可以位于硅片下方。或者,工程師可以添加有源功率傳輸設備,例如靜電放電安全二極管。

3D整合

進行 3D 集成的方法有多種,但當今最先進的是晶圓到晶圓和芯片到晶圓的混合鍵合。這兩個提供了兩個硅芯片之間最高密度的互連。但這種方法要求兩個芯片設計在一起,因此它們的功能和互連點對齊,使它們可以作為一個芯片,技術人員的主要成員 Anne Jourdain 說。Imec R&D 有望在不久的將來每平方毫米產生數百萬個 3D 連接。

進入 CMOS 2.0

CMOS 2.0 將分解和異構集成發揮到極致。根據哪些技術對特定應用有意義,它可能會產生一個包含嵌入式內存、I/O 和電源基礎設施、高密度邏輯、高驅動電流邏輯和大量緩存存儲器層的 3D 系統。

要達到這一點,不僅需要技術開發,還需要工具和培訓來辨別哪些技術可以真正改進系統。正如 Bardon 指出的那樣,智能手機、服務器、機器學習加速器以及增強現實和虛擬現實系統都有非常不同的要求和限制。對一個人有意義的事情對另一個人來說可能是死胡同。

審核編輯 :李倩

-

芯片

+關注

關注

453文章

50406瀏覽量

421822 -

CMOS

+關注

關注

58文章

5680瀏覽量

235144 -

機器學習

+關注

關注

66文章

8377瀏覽量

132409

原文標題:芯片微縮最新路線圖,2036年實現0.2nm

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

2024學習生成式AI的最佳路線圖

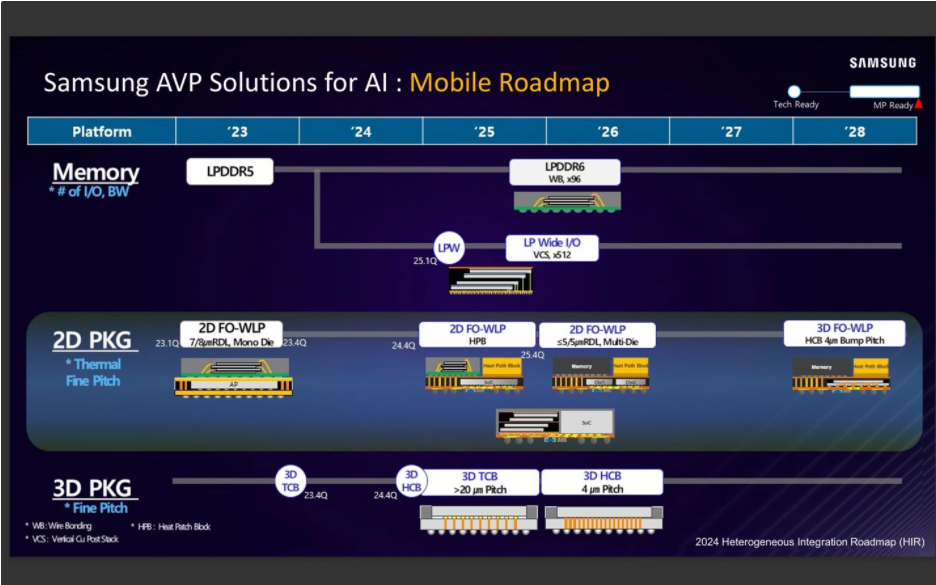

三星電子公布2024年異構集成路線圖,LP Wide I/O移動內存即將面世

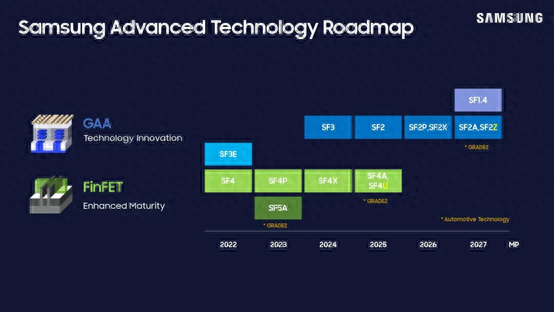

三星公布最新工藝路線圖

三星芯片制造技術路線圖出爐,意強化AI芯片代工市場競爭力

英飛凌為AI數據中心提供先進的高能效電源裝置產品路線圖

iPhone升級路線圖曝光:1年后才配12G內存,2026年有折疊屏

北京開源芯片研究院加入甲辰計劃,預計2036年實現全信息產業

事關衛星物聯網!LoRaWAN 2027 發展路線圖重磅公布

安霸發布5nm制程的CV75S系列芯片,進一步拓寬AI SoC產品路線圖

美國公布3D半導體路線圖

納微半導體發布最新AI數據中心電源技術路線圖

納微半導體發布最新AI數據中心電源技術路線圖

英特爾晶圓代工業務再升級,新路線圖出爐

芯片微縮最新路線圖,2036年實現0.2nm

芯片微縮最新路線圖,2036年實現0.2nm

評論