SystemVerilog是一名芯片驗(yàn)證工程師,必須掌握的一門(mén)語(yǔ)言,其中Function Coverage是必須要懂的知識(shí)點(diǎn)之一;

看完這篇,應(yīng)該就會(huì)寫(xiě)Function Coverage了;

一、概述

有一定基礎(chǔ),想直接看用法,直接看第二部分——實(shí)現(xiàn)(強(qiáng)調(diào)!代碼部分要精讀,文字略抽象,例子好理解)。

功能覆蓋率(Function Coverage)是衡量驗(yàn)證完備性的重要標(biāo)準(zhǔn)之一。

其用于度量驗(yàn)證中已執(zhí)行的測(cè)試點(diǎn)(cover point)占設(shè)計(jì)規(guī)范的比例,從而避免功能驗(yàn)證的遺漏。或者說(shuō),F(xiàn)unctional coverage是驗(yàn)證工程師基于對(duì)DUT的認(rèn)識(shí)來(lái)對(duì)驗(yàn)證feature進(jìn)行分解后,將需要覆蓋的點(diǎn)進(jìn)行分析后寫(xiě)出,因此對(duì)于DUT Spec的信息提取非常重要。

Functional_coverage可以檢查:

1. 你關(guān)心的場(chǎng)景是否覆蓋完備;2. 驗(yàn)證工程師構(gòu)造的隨機(jī)激勵(lì)的隨機(jī)程度/合理性;3. 從Spec中提取的feature點(diǎn)是否覆蓋完備;...

Function Coverage通過(guò)編寫(xiě)coverage group, coverage points和bins等來(lái)構(gòu)造收集“容器”。這里我們不介紹Assertion Coverage, Code Coverage等,以后會(huì)單獨(dú)介紹。

收集Function Coverage的相關(guān)驗(yàn)證文件是由驗(yàn)證工程師定義編寫(xiě)的,靈活度很高,所以更需要謹(jǐn)慎對(duì)待,這是個(gè)Review的過(guò)程,一般需要編寫(xiě):unit_coverage.sv + unit_coverage_interface.sv + top.sv。

1. unit_coverage.sv (unit_cov.sv),可能包含多個(gè)功能覆蓋模型coverage group,構(gòu)造的收集“容器”,收集過(guò)程在這里實(shí)現(xiàn);2. unit_coverage_interface.sv(unit_cov_if.sv),定義unit_cov.sv中需要用到的interface;3. top.sv,將unit_cov_if.sv中定義的interface與DUT中對(duì)應(yīng)的interface連接起來(lái);

二、實(shí)現(xiàn)

功能覆蓋率模型/覆蓋組(cover group):

覆蓋組是使用cover group構(gòu)造定義的。

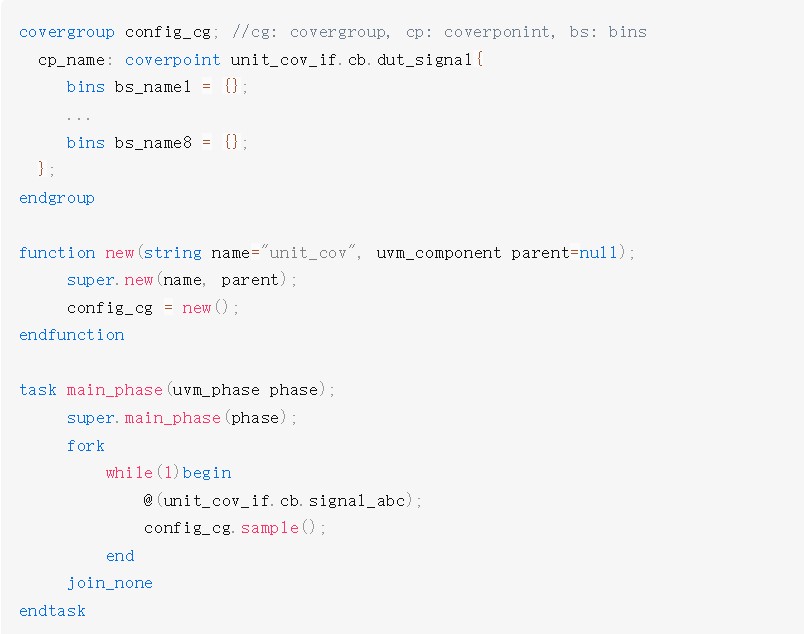

ex1: 會(huì)在指定的signal_abc變化時(shí)才采樣

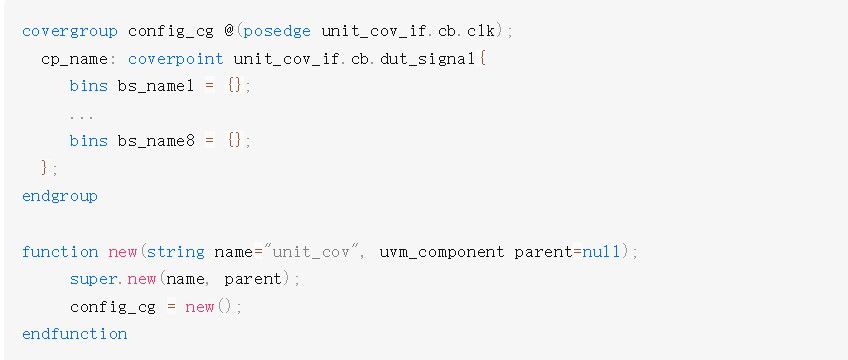

ex2:在時(shí)鐘上升沿((posedge)采樣。

覆蓋點(diǎn)(cover ponit):

覆蓋點(diǎn)是使用cover ponit和bins構(gòu)造定義的。

一個(gè)覆蓋組可以包含一個(gè)或多個(gè)覆蓋點(diǎn)。每個(gè)覆蓋點(diǎn)都與“ bins”關(guān)聯(lián)。“bins”可自動(dòng)創(chuàng)建,也可以明確定義。

ex1:自動(dòng)創(chuàng)建bins

為coverpoint變量范圍的每個(gè)值自動(dòng)創(chuàng)建一個(gè)bins,這稱(chēng)為自動(dòng)或隱式bins。

對(duì)于“ n”位的整數(shù)coverpoint變量,將創(chuàng)建2^n個(gè)bin,但是最多為64個(gè),當(dāng)2^n大于64時(shí),每個(gè)bin不再是一個(gè)值,而是2^n/64

ex2:明確定義bins

該方式--- 常用,這里重點(diǎn)看每個(gè)bins定義代表的不同意義。

在覆蓋點(diǎn)標(biāo)識(shí)符(cover point)之后,在大括號(hào){}中顯式聲明bins,其中聲明bins名稱(chēng)和變量值/范圍。

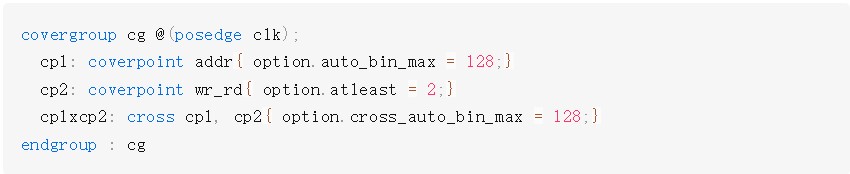

ex3:交叉覆蓋(cross)

覆蓋選項(xiàng)(cover options)

at_least

每個(gè)bins的最小匹配/采樣次數(shù)。默認(rèn)值為“ 1”,默認(rèn)情況下,數(shù)值采樣了1次就可以計(jì)入有效的bin(已覆蓋)。可以通過(guò)修改at_least來(lái)修改每個(gè)bin對(duì)應(yīng)的最小采樣次數(shù),注意,如果低于at_least數(shù)值,則該bin不算被覆蓋。在covergroup里使用 option.at_least,會(huì)影響所有的coverpoint里的bin。在coverpoint里使用 option.at_least,只影響該coverpoint下的bin,但coverpoint中使用會(huì)覆蓋covergroup中的使用。

auto_bin_max

沒(méi)有為coverpoint明確定義bins時(shí)自動(dòng)創(chuàng)建bins的最大數(shù)量。默認(rèn)值為“ 64”。

cross_auto_bin_max

沒(méi)有默認(rèn)值,它是無(wú)界的。

如果對(duì)一個(gè)covergroup實(shí)例化了很多次,那么SV默認(rèn)會(huì)把所有實(shí)例的覆蓋率合并在一起。 option.per_instance = 1,表示covergroup的每一個(gè)實(shí)例的覆蓋率都要單獨(dú)計(jì)算。

goal

不論covergroup或是coverpoint的目標(biāo)覆蓋率皆是100%,不過(guò)也可以通過(guò)option.goal=value,來(lái)降低覆蓋率目標(biāo),這個(gè)選項(xiàng)只會(huì)影響覆蓋率報(bào)告。

......

更多options和關(guān)于Function Coverage更詳細(xì)的描述/用法去翻閱《system verilog官方手冊(cè)》:《IEEE Standard for SystemVerilog — Unified Hardware Design, Specification, and Verification Language》的第19章。

-

Verilog

+關(guān)注

關(guān)注

28文章

1343瀏覽量

109985 -

時(shí)鐘

+關(guān)注

關(guān)注

10文章

1720瀏覽量

131364 -

DUT

+關(guān)注

關(guān)注

0文章

189瀏覽量

12338

原文標(biāo)題:【看即會(huì)用】SystemVerilog實(shí)用知識(shí)點(diǎn):覆蓋率之Function Coverage

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文詳解Modelsim代碼覆蓋率功能使用

為什么覆蓋率分析師沒(méi)有證明電阻器已經(jīng)過(guò)測(cè)試?

關(guān)于SpinalHDL中的驗(yàn)證覆蓋率收集簡(jiǎn)單說(shuō)明

重點(diǎn)厘清覆蓋率相關(guān)的概念以及在芯片開(kāi)發(fā)流程中跟覆蓋率相關(guān)的事項(xiàng)

Systemverilog覆蓋率的合并和計(jì)算方式

Verilog代碼覆蓋率檢查

IP開(kāi)發(fā)時(shí)如何考慮復(fù)用覆蓋率

嵌入式代碼覆蓋率統(tǒng)計(jì)方法和經(jīng)驗(yàn)

統(tǒng)計(jì)嵌入式代碼覆蓋率的方法和經(jīng)驗(yàn)

SystemVerilog實(shí)用知識(shí)點(diǎn):覆蓋率之Function Coverage

SystemVerilog實(shí)用知識(shí)點(diǎn):覆蓋率之Function Coverage

評(píng)論