ASIC設計在尺寸和復雜性上不斷增加,現代FPGA的容量和性能的新進展意味著這些設計中的2/3能夠使用單個FPGA進行建模。然而,這些設計中仍然保留有1/3(那就是說,所有ASIC設計中的1/9)要求一個基于多個FPGA的原型開發板。

在不太遙遠的過去,對ASIC設計團隊而言,在這類情況下主要的解決方案就是在內部建立他們自己的定制多個FPGA的原型開發板。然而,今天,使用現成的多個FPGA原型開發板——例如,由Synplicity公司的原型開發伙伴生產的開發板——與合適的設計工具相結合能夠節省數周時間,否則的話將花費幾個月的驗證時間以及在NRE費用上花費數萬美元。

本文首先討論了ASIC驗證能夠采用的主要技術。接著,文章考慮了與使用一個現成的產品相比,建立一個定制的多個FPGA的原型開發板的優勢和缺陷。,論文介紹了目前的用于驗證大型設計的分割和綜合設計工具,其采用內部開發或現成的多個FPGA的原型開發板。

可供選擇的驗證技術

今天高端ASIC,例如那些在手機、通訊、圖形子系統以及信號處理應用中使用的,經常包含多個CPU和DSP內核,其結合了硬件加速器、外圍設備、接口和存儲器管理內核。(由于這些討論的目的,術語ASIC被假設包括了ASSP和SoC器件。)所以,為了滿足芯片的市場需求,盡可能早的在設計階段開發、端口、集成、調試和驗證任何嵌入式軟件的內容。

ASIC的RTL全功能驗證——其本身與任何嵌入式軟件——是ASIC設計過程中耗費時間和困難的部分之一。統計表明今天ASIC設計中的70%要求重制。除了費用極其昂貴之外,重制能夠引起項目失去其市場空間,這將嚴重損害公司的聲譽和金融底線。

對ASIC設計者開放的三個主要驗證選擇是仿真,模擬和FPGA原型開發。

*仿真:基于軟件的仿真被廣泛使用,但即使在一個真正的高端(并且,相對昂貴)的計算機平臺運行時,其運行比實際的ASIC硬件慢六到十個數量級,這使得其成為一項極大花費時間并且效率極差的技術。為了提供整個系統的尺寸認識,軟件仿真能夠典型地達到僅僅幾Hz相當的速度(那就是,設計的系統時鐘相對真實時間每秒鐘的幾個周期)。實際上,這意味著僅僅在一小部分設計中能夠實現廣泛的軟件驗證。

*模擬:基于硬件的模擬是另一個可供選擇的方法,但它仍然比實際的ASIC硬件至少慢三個數量級,因為大量的有關的復用技術將驗證速度減慢到僅僅500 KHz到2 MHz。此外,這種方法在預算和資源方面(依賴于模擬器的大小,每個相等的門電路成本能夠從25美分到一美元)是極其昂貴的。設計者需要的是一種可供選擇的方法,這將允許他們以較低的風險和成本投放市場。

*基于FPGA的原型開發:在許多情況下,“快速”驗證設計是必要的。例如,就視頻處理芯片來說,部分驗證可能包含評估視頻輸出流的主觀品質。相似地,在嵌入式軟件中驗證硬件要求極高的速度。其答案就是使用運行在10到80 MHz速度下的多個FPGA原型開發板,其相等于(或相當于)真實時間的ASIC速度(“真實激勵輸入,真實響應輸出”)。當將設計定制開發板與使用現成的開發板進行比較時,后者——當與恰當的設計工具結合時——能夠削減數周時間,不然的話,將花費數月的驗證時間并且(在每個相等的門電路為一美分的典型值下)節省數萬美元的NRE費用。

所關心的同樣是,除了提供一個軟件開發平臺和硬件的軟件驗證之外,該公司設計ASIC簡單地要求盡可能快的完成設計的全部功能;例如,證明硬件可以進行商業展示。

全定制與現成的原型開發板

大約在本文寫作前的三至五年,所有多個FPGA的原型開發板是“建立你自己的”全定制品種。相反,今天有著眾多現成的多個FPGA的原型開發板供應商群體。

提供一些參考,傳統的硬件模擬目前的市場是每年一億美元。比較起來,在過去幾年中,沒有任何人真正注意到,現成的多個FPGA的原型開發板工業已經增長到硬件模擬市場規模的四分之三。

工程師認為任何通用的都是次的。事實上,工程師經常希望建立他們自己的定制原型開發板,因為他們認為其性能將更好,他們相信與真實的世界接口將更容易,這些接口將更接近于他們想要的,他們認為這將減少項目成本,并且這將減少產品推向市場的時間。讓我們依次列出這些觀點:

*更好的性能:在包含了兩個或三個以上FPGA的原型開發板情況下,定制實現方式將超過它的現成對應物的性能是非常不可能的。這是因為設計這樣一塊電路板要求非常高水平的知識和經驗,這只能通過在幾年內設計數代這樣的電路板得到提高。

*消除創新:如果一項ASIC設計適合單個的FPGA,然后設計和實現一塊定制的電路板是相對簡單的。比較起來,在一項要求兩個FPGA的ASIC設計的情況下,該問題變得非常令人感興趣;并且,當使用三個或更多的FPGA時,事情變得按指數規律增加復雜性。

*消除接口:如果一項ASIC設計適合單個的FPGA,然后有一些令人信服的原因來設計定制電路板。其中一個原因是,在同一塊卡上按照任何接口邏輯實現該FPGA通常是有意義的。然而,在多個FPGA的原型開發板的解決方案中,通過使用很的現成電路板以及集中努力在特制的接口卡設計上,接口問題幾乎總是很簡單的。

*減少成本:設計和實現高端多個FPGA原型開發板要求大量的設計工程師和版圖工程師,這將比簡單的購買現成的電路板增加非常大的成本。

*減少產品推向市場的時間:即使對一家設計和實現多個FPGA原型開發板的公司而言,高端電路板的制作能夠很容易的花費掉9個月(并且這假設多個工程師和版圖設計師分多班倒班工作)的時間。不必驚訝,一個非的團隊將幾乎肯定花費更長的時間,這能夠很容易的造成項目落后于它的進度表,并且失去它的市場空間。作為一個多個FPGA原型開發板設計問題復雜性的例子,考慮來自Dini集團的DN8000K10電路板。Dini集團是Synplicity原型開發計劃的合作伙伴成員。

DN8000K10是一個USB 2.0主機邏輯原型系統,其能夠用二到十六個高容量的FPGA來組裝。在其的配置中,該電路板能夠被用于代表保守值相當于24,000,000 ASIC門的原型設計。

DN8000K10的設計和實現共花費九個月的時間。為該項目的一部分,六位版圖工程師分兩班輪班工作了幾個月。終的產品是28層的電路板,其芯片間通訊是在350 MHz下采用低壓差分信號(LVDS)實現的。(在設計管腳受限的情況下,每個LVDS管腳對支持集成的SERDES,這能夠提供高達10:1的復用。)在這一復雜度上,噪聲的處理問題和信號完成性問題要求很高的知識和經驗水平。這一水平的電路板完全超過了今天現成的自動布線工具能夠找到解決方案的能力的一至兩個數量級;所以,每個管腳是“手工挑選”,并且每條路徑是“手工連接”——沒有使用自動布線(除了該電路板周圍的外圍設備之外)。

手工分割和綜合多個FPGA設計

在手工分割的情況下,任何ASIC中心結構(門控時鐘,Synopsys的DesignWare?實例等),在原始的RTL源代碼中,在進行分割之前,不得不手工將它們翻譯為與它們的FPGA相等同的代碼。除其它東西之外,這直接導致了兩個分離的代碼流,這可能失去同步,從而導致在FPGA原型和ASIC之間所代表的功能不同。

當開始分割處理時,工程師們嘗試將不同的功能模塊組集合在一起,在這里每組在不同的FPGA上實現。這種組合(分割)以門級的傳統方式實現。近,一些流程支持在RTL級分組,此時每個分成的組通過傳統的FPGA綜合工具,并且僅在這一點上,不同FPGA的實際資源利用是已知的。

所有這些方案都有一個問題,就是對于不同組的面積和資源的影響而言,工程師們是“臨時的盲人”,這導致了許多耗時的迭代。首先,工程師根據“A模塊可能將消耗‘xxx’的資源,而模塊B可能要求‘yyy’的資源”而進行“估算”。這些估算是根據大量“分組”命令,然后綜合(在基于RTL分割的情況下),然后是結果的分析,以及然后是大量的“取消組”和“再次分組”命令來估算不同的實現方式。

該任務由于這一事實而進一步混淆,該事實就是這些原型經常被FPGA上的I/O管腳的數量所限制;一個無效的解決方案很容易耗費一個器件上100%的I/O資源,然而與此同時,僅僅其相對少量的內部邏輯資源可以實現。為了克服這些I/O限制,I/O的多重分組和/或在多個FPGA中復制同一個邏輯模塊是必要的。(為了達到特定的性能目標,邏輯復制也是經常要求的。)

假設在這種原型中使用的每個FPGA可能有超過1000個管腳,一項管理連接的電子表格方法能很容易地包含幾千個單元。不足為奇地是,記錄分配給每個FPGA的模塊和連接矩陣(在不同FPGA之間的連接)是一項繁重的任務,這將是資源密集型的、耗時的以及容易出錯的。

自動分割和綜合多個FPGA設計

來自Synplicity的CerTIfy? RTL原型開發工具是業內時間長和強大的多個FPGA分割和綜合工具。很令人感興趣的是,當CerTIfy軟件在上世紀90年代晚期創立時,對ASIC設計團隊而言,沒有任何現成的多個FPGA原型開發板能夠得到。在那時,CerTIfy軟件被設計成一個ASIC團隊設計他們自己的定制的多個FPGA原型開發板的輔助工具。

使用CerTIfy軟件,工程師們能夠定義電路板上的FPGA的數量和類型以及它們之間的互連線。隨后,該數據被用于對通過多個FPGA進行ASIC設計自動地分割RTL,并且將被分割的RTL綜合成用于FPGA編程的配置文件。

一旦工程師們已經使用Certify工具來定義電路板的基本結構,來自該軟件的輸出之一是描述FPGA以及它們之間連接的網表。以Verilog來描述的該網表的格式由Synplicity定義,并且是的*.vb(Verilog模版)格式。

設計團隊希望建立他們自己的定制電路板今天仍然使用這種技術。這一點使得Synplicity的*.vb格式很快變成這種類型應用的事實上的工業標準。現在,每個現成的多個FPGA原型開發板供應商采用通用的*.vb文件交付他們的電路板,其作為定義每塊開發板結構的輸入被讀入到Certify軟件。

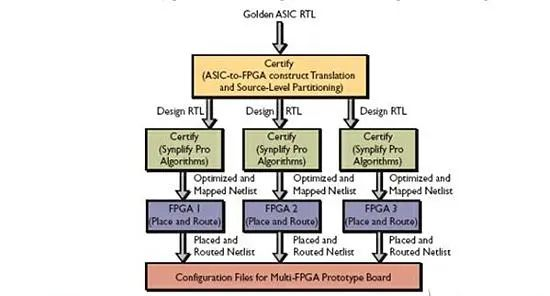

Certify工具能夠采用Verilog、VHDL和混合語言進行設計。該流程中的個要素是采用Certify軟件,自動將任何ASIC專用代碼轉換為相當的FPGA結構。就目前現成的多個FPGA原型開發板而言,用戶簡單地通知軟件使用下拉式列表框的開發板的類型,該列表框包括來自所有主要第三方供應商所提供的開發板。(換句話說,如果這是一塊定制的電路板,Certify工具有能力建立一個在傳輸過程中的“虛擬的”多個FPGA開發板,接下來這塊虛擬的開發板能夠作為建立真實電路板的基礎來使用。)接下來,Certify軟件用于通過多個FPGA自動分割設計(圖 2)。

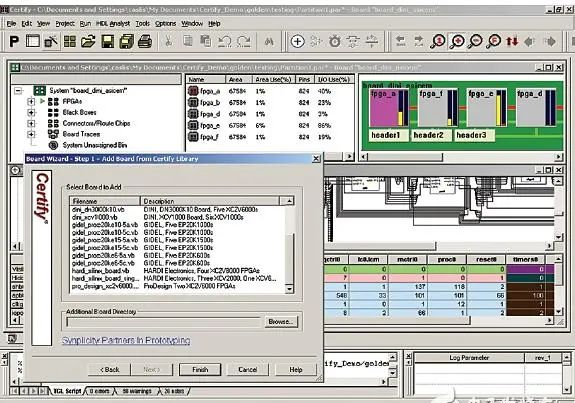

與Certify軟件緊密集成在一起的是Synplicity的HDL分析器,其以的層次化的模塊圖以及接著綜合相應的門級電路的形式,自動地產生設計的技術獨立的圖形視圖。Certify和HDL分析器工具在HDL源代碼和模塊級以及門級電路之間,支持全雙向交叉探測,所以允許設計者在設計以及定位感興趣的信號和邏輯功能之間,進行快速定位。除設計的各種其他視圖之外,Certify軟件提供一個形成原型開發板的FPGA的圖形表示(第6頁圖3)。這些虛擬器件中的每一個有兩個關聯的“溫度計型”顯示:其反映I/O的應用和器件的其他面積/資源應用。

以I/O和相關的邏輯資源以及FPGA和在FPGA之間的布線資源的認識為基礎,Certify軟件能夠自動地實現管腳分配和交互地執行分割——通過簡單地拖曳代碼模塊和將它們下拉到不同的FPGA——或者兩種技術可以混合使用。

Certify軟件提供大量非常強大的工具來幫助分割任務。例如,接下來的分割,軟件能夠分析結果和向用戶提出使用Certify管腳復用(CPM)的時機,信號的復合設置是一起復用來減輕在相關器件I/O資源上的負載。除了在多個器件上促進邏輯復制外,Certify工具也提供位片應用,其中寬的數據路徑結構能夠?裂成更小的分支。此外,Certify軟件提供成熟的“撕裂”能力,借此將大的模塊分解成更小的部分(這些部分能夠依次分配給不同的FPGA)。

作為一個候選的分割實現方式就是建立,其他非常有用的特性使其能夠被命名和保存。這允許用戶維持對多個可選擇的分割方案的控制。這種能力能夠與Certify軟件的影響分析特征一道使用,其允許用戶就在該多個FPGA開發板上能夠得到的面積和I/O而論,估計布局和/或移動邏輯。而不是用戶不得不推測這個邏輯應該被分配給哪個FPGA,影響分析產生關于以那個分割決定為基礎的特定信息。

一旦分割已經被執行,Certify軟件用于綜合與不同的FPGA器件有關的代碼流。該工具使用同一個基本的綜合技術,就是起重要作用的Synplicity的主導市場的Synplify Pro? FPGA綜合引擎。例如,Certify軟件充分利用Synplicity的BEST? (Behavior Extracting Synthesis Technology?)算法,其分析RTL和在主要綜合步驟前實現優化。并且,Certify工具以擁有Synplify Pro軟件的先進的綜合能力為自豪,例如資源共享、寄存器平衡、重定時、復制以及再次綜合。

這個過程一個關鍵的方面是Certify軟件把不同的FPGA簡單看作設計層次中一個額外的層。這意味著該工具提供針對性能優化時序路徑的獨特能力,甚至當這些路徑越過多個FPGA時(Certify軟件也能夠提供一個時序,其告知設計者原型在硬件被編程之前能夠達到的性能)。

總結

建立ASIC原型設計的必要性正在不斷增加,按照系統要求其實現是“飛速”地。達到這一性能水平的節省成本的技術就是,建立基于FPGA的原型開發。已經證明有九分之一的ASIC設計師使用多個FPGA的原型開發板,這一趨勢正在不斷增長。在這種情況下,人們越來越普遍使用現成的原型開發板,這來自Synplicity的原型開發伙伴之一,包括Dini集團、Hardi電子、GiDel和Altera。

當使用與來自Synplicity的Certify RTL原型開發軟件時,與建立定制的原型開發板相比,這些技術的電路板在更低的成本上提供了更高的性能,并且減少了產品推向市場的時間。現成的多個FPGA的原型開發板和Certify軟件的組合意味著ASIC項目能夠節省數月的驗證時間,這是在所有的器件和系統層次,允許設計團隊與真實的硬件相比進行測試得出的結論,并且可以在設計過程中較早的發現難以察覺的問題。通過較早的允許硬件原型用于軟件開發和系統集成,可以更進一步的縮短產品推向市場的時間。

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:利用FPGA開發板進行ASIC原型開發的技巧

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601804

原文標題:利用FPGA開發板進行ASIC原型開發的技巧

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

正點原子fpga開發板不同型號

正點原子和野火開發板哪個好

ARM開發板與FPGA的結合應用

NXP FRDM-MCXC444開發板在RT-Thread環境下的上手過程

linux開發板和單片機開發的區別

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰的任務!

米爾NXP i.MX 93開發板的Qt開發指南

RL78/G24快速原型開發板資料包大全

PY32系列單片機開發板 常用型號都有 支持Keil,IAR進行開發

利用FPGA開發板進行ASIC原型開發的技巧

利用FPGA開發板進行ASIC原型開發的技巧

評論