剛剛初學VerilogHDL的時候,感覺語言風格很像C語言,編程也是完全用軟件的思想去寫,但是使用過FPGA和學習了數(shù)集之后,才醒悟出何為“硬件思想”,本節(jié)主要介紹一下西交邱志雄老師一門課中的VerilogHDL描述方法。

VerilogHDL可綜合的四大法寶:always、if-else、case、assign ,本文將圍繞這四大法寶來講述。

有可綜合的法寶,那么可綜合風格禁止出現(xiàn)的情況:function、for、fork-join、while等。

** If-else的硬件映射及優(yōu)化**

01

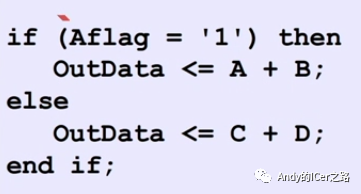

if-else的映射硬件結(jié)構(gòu)是多路選擇器Multiplexing Hardware(簡稱Mux)。

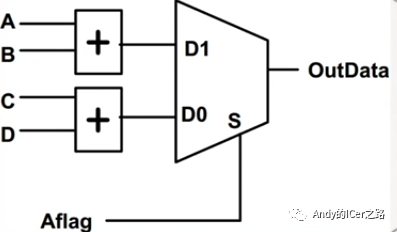

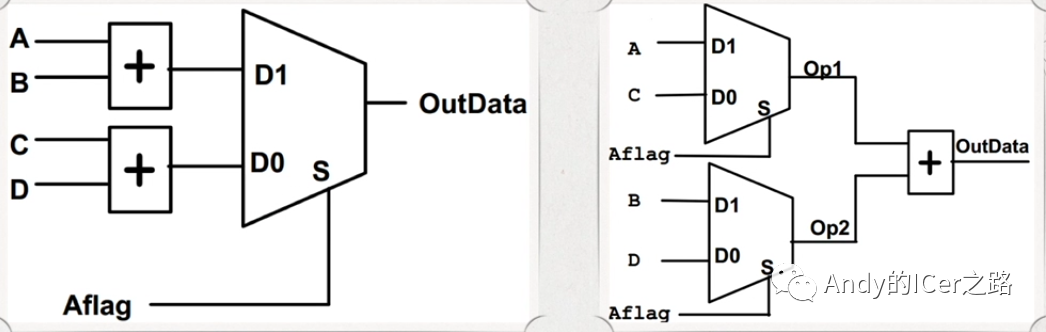

我們來看看上面的第一段代碼,我們心中要出現(xiàn)該代碼描述的電路,該電路由兩個加法器和一個Mux組成。

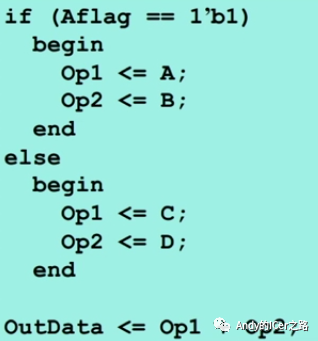

接下來我們看第二段代碼:

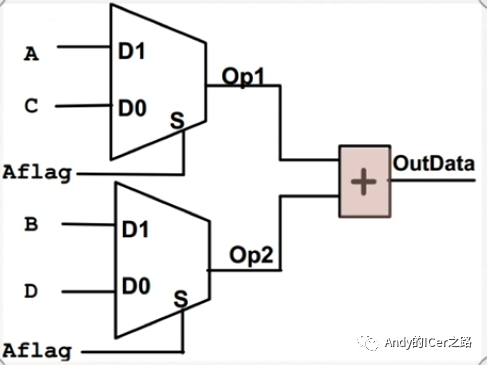

該段代碼描述的電路應(yīng)該是兩個Mux和一個加法器組成:

兩段代碼描述的功能都一樣,但是電路面積卻不一樣,第二段代碼描述的電路少了一個加法器多了一個Mux,在同一個工藝庫下,二輸入Mux的晶體管數(shù)量比一位半加器少,因此第二段代碼描述的電路減少了硬件的面積。

從面積的角度看,第二段代碼更優(yōu),但是真的可以說第二段代碼比第一段代碼好嗎?很顯然,一般這么問,答案都為否定。

我們從傳播延遲的角度再來分析一下這兩個電路:

1、左圖的數(shù)據(jù)通道的延遲是一個加法器和一個Mux,控制通道的延遲是一個Mux。

2、右圖的數(shù)據(jù)通道的延遲依然是一個加法器和一個Mux,控制通道的延遲卻是一個加法器和一個Mux。

很顯然第二段代碼描述電路(右圖)的控制通道延遲比較大,如果Aflag到來的延遲比較晚的話,那么第二種電路的性能就會比第一種差。

綜上所述,在設(shè)計的時候要根據(jù)輸入約束,再來選擇兩種不同的設(shè)計:是先加后選,還是先選后加。

** If的優(yōu)先級問題**

02

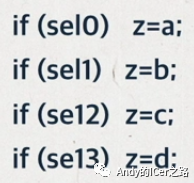

多if語句具有優(yōu)先級的判斷結(jié)構(gòu),即輸入信號是有不平等關(guān)系的,最后一級選擇信號具有最高優(yōu)先級,具有優(yōu)先級的多選結(jié)構(gòu)會消耗組合邏輯,而且這種寫法比較亂,一般不推薦這種寫法。(case語句是無優(yōu)先級的)

但是在某些設(shè)計中,有些信號要求先到達(如關(guān)鍵使能信號、選擇信號等),而有些信號需要后到達(如慢速信號、有效時間較長的信號等),此時則需要用if...if... 或者 if...else if...結(jié)構(gòu),一般最高優(yōu)先級給最遲到的關(guān)鍵信號。

電路之大敵——Latch

03

latch由電平觸發(fā),非同步控制,所以非常 容易產(chǎn)生毛刺(glitch) ,這是很大的危害,這對于下一級電路是極其危險的,而且靜態(tài)時序分析會變得極為復雜,因此只要能用D觸發(fā)器的地方就不用latch。

易引入latch的途徑:使用不完備的條件判斷語句,如if缺少else,case缺少default。

邏輯復制 均衡負載

04

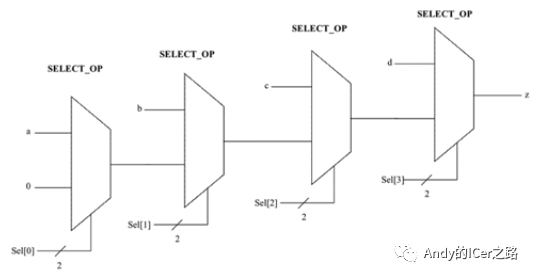

通過邏輯復制,降低關(guān)鍵信號的扇出,進而降低該信號的傳播延遲,提高電路的性能。

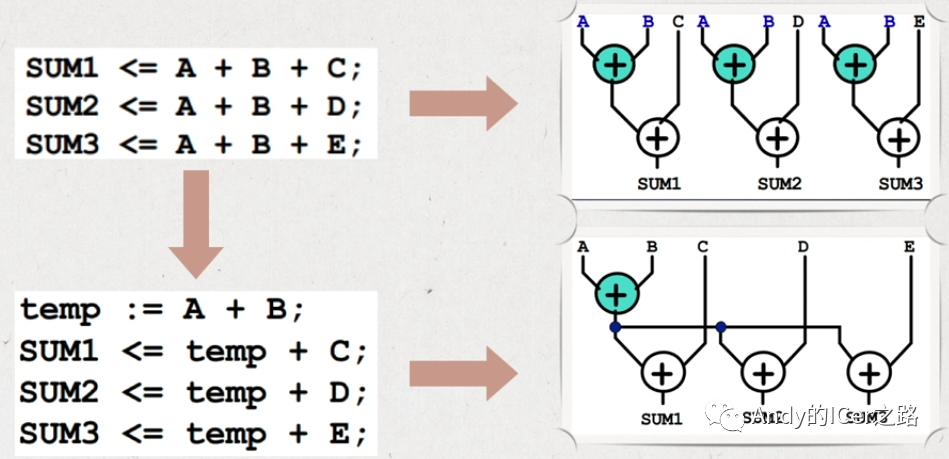

資源共享 減小面積

05

如果電路中存在較多的公共單元,可以通過資源共享,來減小電路的面積,但是一般來說,共享會降低電路性能,所以還是要根據(jù)性能和面積而進行取舍。

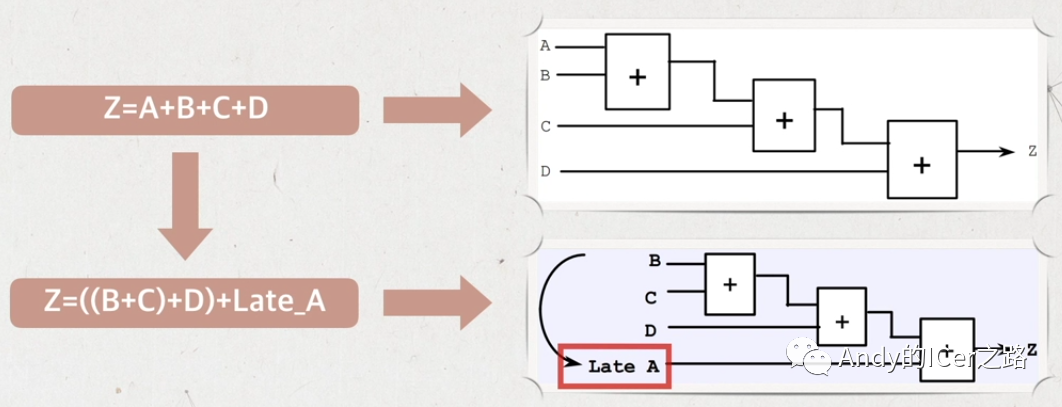

邏輯重組 降低延時

06

在電路設(shè)計中,可以根據(jù)信號的延時,對這些資源進行順序的重排,以降低傳播延時。如下圖所示,信號A延遲比較高,可以把它盡可能地放到后面隱藏其延遲。

邏輯賦值

07

在時序電路中必須使用非阻塞賦值(<=), 組合邏輯電路必須使用阻塞賦值(=)。

-

晶體管

+關(guān)注

關(guān)注

77文章

9641瀏覽量

137876 -

時序電路

+關(guān)注

關(guān)注

1文章

114瀏覽量

21682 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30093 -

VerilogHDL語言

+關(guān)注

關(guān)注

0文章

2瀏覽量

5788 -

多路選擇器

+關(guān)注

關(guān)注

1文章

22瀏覽量

6517

發(fā)布評論請先 登錄

相關(guān)推薦

高質(zhì)量VerilogHDL描述方法

高質(zhì)量VerilogHDL描述方法

評論