在RTL編碼中考慮延時

01

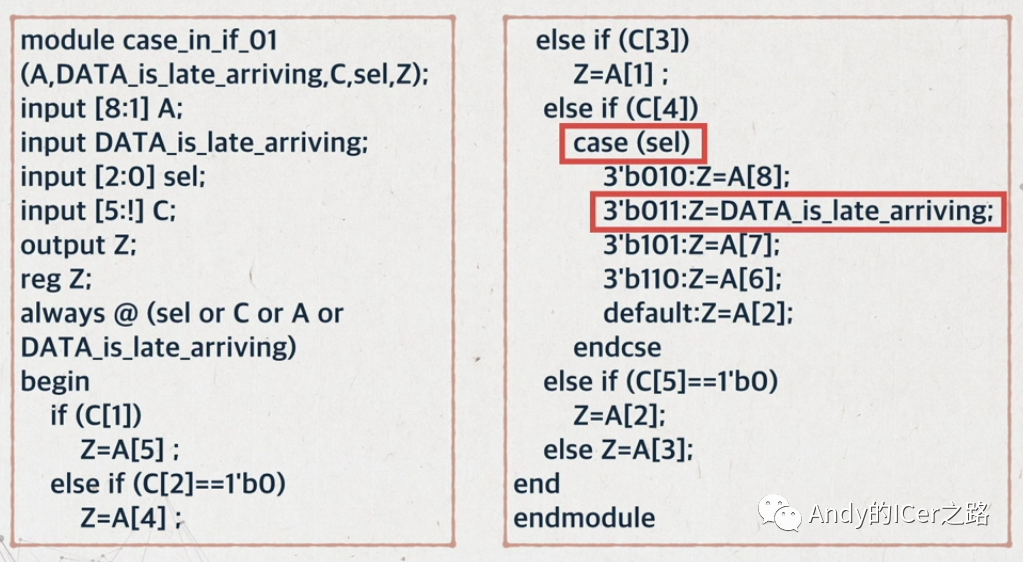

看下面一段代碼,第四個else if 分支中的數(shù)據(jù)信號DATA_is_late_arriving延時比較高,要怎么處理,將電路的性能提高?

一般最高優(yōu)先級給最遲到的關(guān)鍵信號,因此要將DATA_is_late_arriving這個信號單獨拿出來分析,代碼如下:

再來看下面一段代碼以及其電路圖,假設(shè)A信號到來比較晚,如何修改能夠提高電路性能?

核心思想還是將延遲高的信號往后面優(yōu)先級更高的地方放 ,只需做小小修改即可,代碼如下:

在RTL編碼中考慮面積

02

隨著芯片工藝的進步和生產(chǎn)成本的降低,其實面積已經(jīng)顯得沒有時序問題那么重要。一般綜合過程中可以對面積進行優(yōu)化,但是在RTL設(shè)計的時候還是需要盡量減小面積的開銷,這樣可以達到事半功倍的效果。

例如RTL代碼中的一個“+”可能對應(yīng)著一個64位的加法器,所以條件語句中的比較運算,我們要判斷其必要性,是否能用更簡單的運算代替。

比如判斷A是否小于32(if(A<32)),可以改成判斷A的第五位是否為0(if(A[5]==1'b0)),這兩種表達形式是等價的,但是后者的判斷條件更節(jié)省面積,相當(dāng)于用一個1bit的邏輯門代替一個6bit的比較器,如果我們遇到定值的比較都可以這么操作。

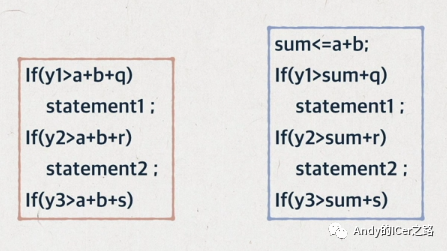

如果必須使用復(fù)雜的運算符,則應(yīng)考慮是否可以資源共享,盡管電路邏輯綜合工具也會在綜合的過程中采用資源共享的方法進行優(yōu)化,但是,綜合器的策略是有限的,因此,在編寫RTL的時候,應(yīng)該盡量考慮共享,而不是把這項工作完全留給綜合工具。

如上面的代碼所示,右邊是修改之后的代碼,這樣可以減少兩個不必要的加法器,實際的設(shè)計中資源共享可能不會像這樣明顯,因此平時應(yīng)該按照這樣的思路多多練習(xí)。

還有一種情況就是關(guān)于多比特位的信號問題, 多比特位操作意味著成倍使用資源 ,在使用多比特位的信號時,看看這個信號是否所有比特位都需要參與操作,如果不是,則可以只對需要的部分比特進行操作。例如訪問RAM的地址有8比特,而寫入操作時從0開始,每隔32個地址寫入一個值,地址的產(chǎn)生可以有兩種寫法。顯然右邊這種寫法操作的比特位會比左邊的代碼少。

在RTL編碼中考慮功耗

03

一個電路中的功耗影響因素主要以下4個因素: 該點電路的翻轉(zhuǎn)次數(shù)、電路的工作頻率、該點的電容還有電壓值 。

但是負載電容、工作電壓和工作頻率這些都是RTL設(shè)計無法改變的因素,因此在RTL級設(shè)計主要考慮盡量降低電路的翻轉(zhuǎn)頻率。

主要措施包括如下:

①門控時鐘;

②增加使能信號,使得部分電路只有在需要工作時才工作;

(門控時鐘與增加使能的區(qū)別是:門控時鐘是關(guān)掉時鐘,而使能關(guān)閉的是電路的功能,但是時鐘仍然在翻轉(zhuǎn),顯然門控時鐘更好)

③對芯片各個模塊進行控制,在需要工作時才工作;

④除了有用信號和時鐘的翻轉(zhuǎn)會消耗功耗,組合邏輯產(chǎn)生的毛刺也會大量消耗功耗。但是毛刺在設(shè)計中無法避免,因此,只有盡量減少毛刺在電路中的傳播,才可以減少功耗。即在設(shè)計中,盡量把產(chǎn)生毛刺的電路放在傳播路徑的最后。另外可以使用一些減少毛刺的技術(shù);

⑤對于有限狀態(tài)機,可以通過低功耗編碼來減少電路的翻轉(zhuǎn),比如將二進制編碼改為獨熱碼、格雷碼等。

在RTL編碼中考慮布線問題

04

如果可以在RTL編碼階段考慮代碼,可能對布線產(chǎn)生的影響就可以避免最后出現(xiàn)無法布通的情況。

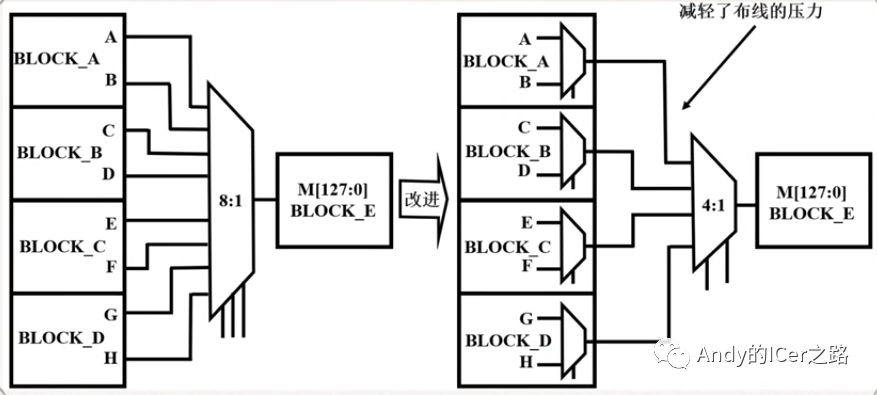

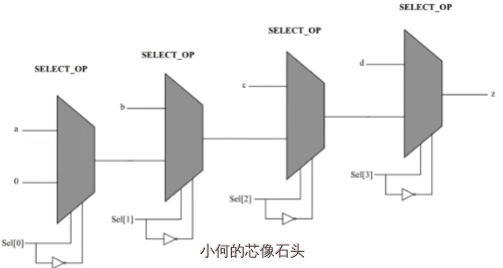

熱點是指設(shè)計的功能需要在一個面積內(nèi)占用大量的布線資源。熱點產(chǎn)生原因:RTL編碼時使用了特定的結(jié)構(gòu),如很大的mux。

這種結(jié)構(gòu)產(chǎn)生的熱點,在綜合的時候,導(dǎo)致的延遲是看不出來的,只有到了布線階段才能給看到它的負面影響。因此,我們在RTL階段應(yīng)該重視這種電路,及早發(fā)現(xiàn)可能在布線階段產(chǎn)生的問題。

如果設(shè)計的功能中確實需要采用很大的mux,可以通過其他方式改變他的結(jié)構(gòu)。其基本的思想就是將一個大的mux分解為多級較小的mux。

-

RAM

+關(guān)注

關(guān)注

8文章

1367瀏覽量

114533 -

比較器

+關(guān)注

關(guān)注

14文章

1636瀏覽量

107103 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30092 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59706 -

門控時鐘

+關(guān)注

關(guān)注

0文章

27瀏覽量

8943

發(fā)布評論請先 登錄

相關(guān)推薦

【設(shè)計技巧】PCB設(shè)計中考慮電磁兼容(上)

【設(shè)計技巧】PCB設(shè)計中考慮電磁兼容(下)

新手求助UPF低功耗設(shè)計能否在RTL仿真中實現(xiàn)呢?

介紹RTL設(shè)計引入的后端實現(xiàn)過程中的布線問題

基于RTL的16位嵌入式微控制器(A8096)的設(shè)計

RTL功耗優(yōu)化

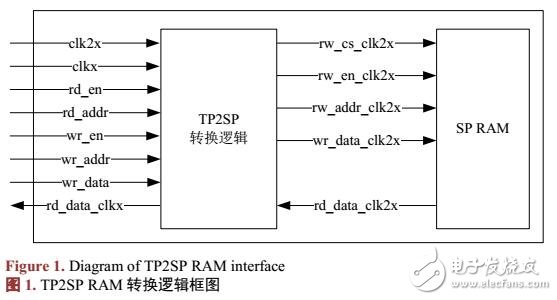

TP RAM的面積及功耗優(yōu)化

現(xiàn)代SAR和∑-Δ型模數(shù)轉(zhuǎn)換器的主要優(yōu)勢之一是在設(shè)計中考慮了易用性

芯片RTL設(shè)計中如何做到低功耗設(shè)計

在RTL設(shè)計中如何做到低功耗設(shè)計

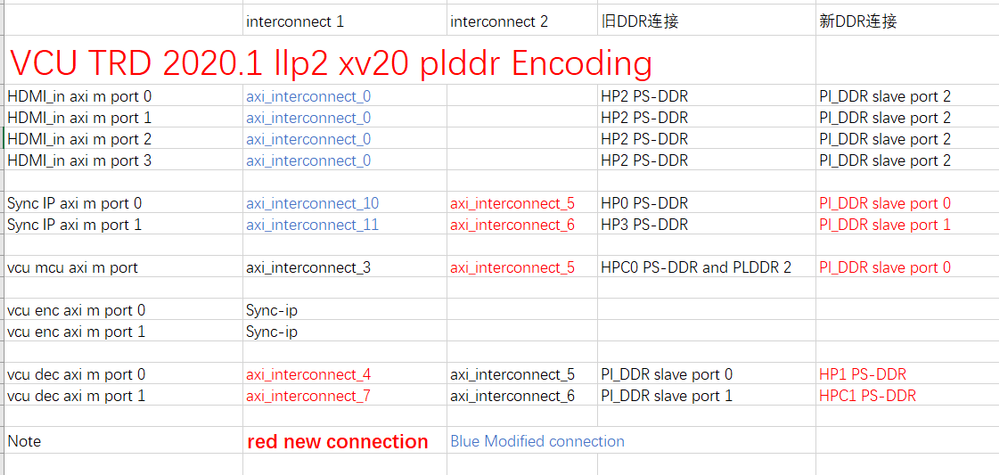

ZCU106在PLDDR實現(xiàn)超低延時編碼

如何通過優(yōu)化RTL減少功耗

在RTL編碼中考慮延時、面積、功耗與布線的問題

在RTL編碼中考慮延時、面積、功耗與布線的問題

評論