數據通信快速發展,相關應用迅速普及,為滿足海量的數據吞吐需求,改善傳輸延時,通信系統和數據中心的傳輸速度和處理能力變得至關重要。時鐘芯片作為這些高性能通信系統和數據中心中必不可少的核心芯片,其性能及可靠性將直接影響系統的誤碼率和穩定性。

一. 5G通信與時鐘同步

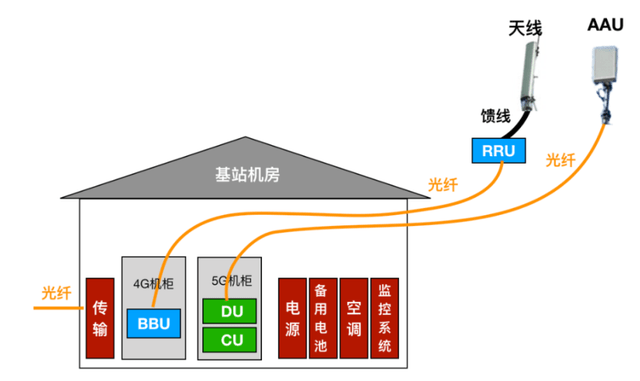

5G基站設備相比于4G基站,設備的功耗和傳輸容量增加,基站站點的配套設備需要進行相應的升級擴容。通過采用多載波聚合和大規模天線陣列等技術來實現高速率、低延時。它匯聚了多頻點協同傳輸數據和多天線通道同步收發數據等技術,而這些技術都對時鐘有高度嚴格的同步要求。

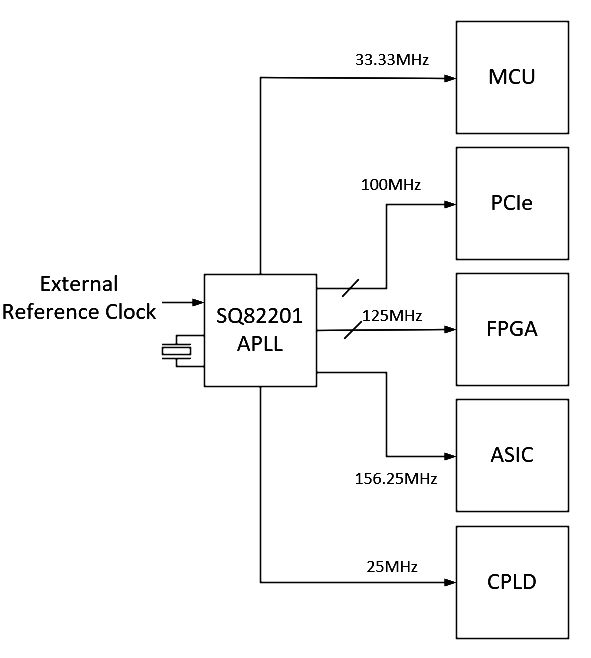

矽力杰最新推出SQ82201 是一款10路輸出的高性能時鐘發生器,集成模擬鎖相環,具有強大的頻率合成、抖動濾除、超低時延等功能。廣泛應用于5G AAU,小基站,通信系統,服務器等。有效滿足各類通信設備的時鐘同步需求。

二. 矽力杰時鐘發生器方案

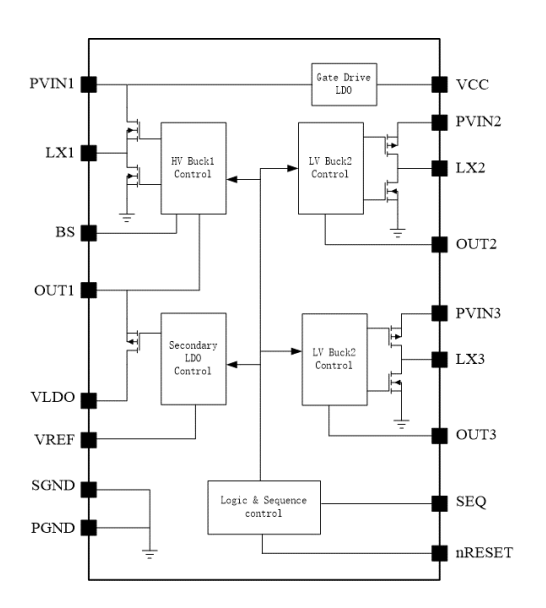

SQ82201 是一款10路輸出的高性能時鐘發生器,其中包括3路LVPECL差分輸出和7路單端輸出。SQ82201內部集成低噪聲鑒相器(PFD),電荷泵(CP),環路濾波器,低相位噪聲高頻壓控振蕩器(VCO)和輸出整數分頻器。

SQ82201 高性能10路輸出時鐘發生器

◆ 7路單端LVCMOS輸出:

? 一個單端LVCMOS的33.33 MHz CPU時鐘

? 六路單端LVCMOS輸出用于參考時鐘緩沖

◆ 3路差分LVPECL輸出對

◆ 可選擇的外部晶體或單端輸入參考源

◆ 為25MHz并聯諧振晶體設計的晶振接口

◆ 156.25MHz輸出, RMS相位抖動: <0.15ps (12kHz~20MHz)

◆ 電源噪聲抑制PSRR: -80dBc

◆ 電源電壓: 3.3V

◆ 緊湊型封裝: QFN6×6-40

◆ 工作溫度: -40~85°C

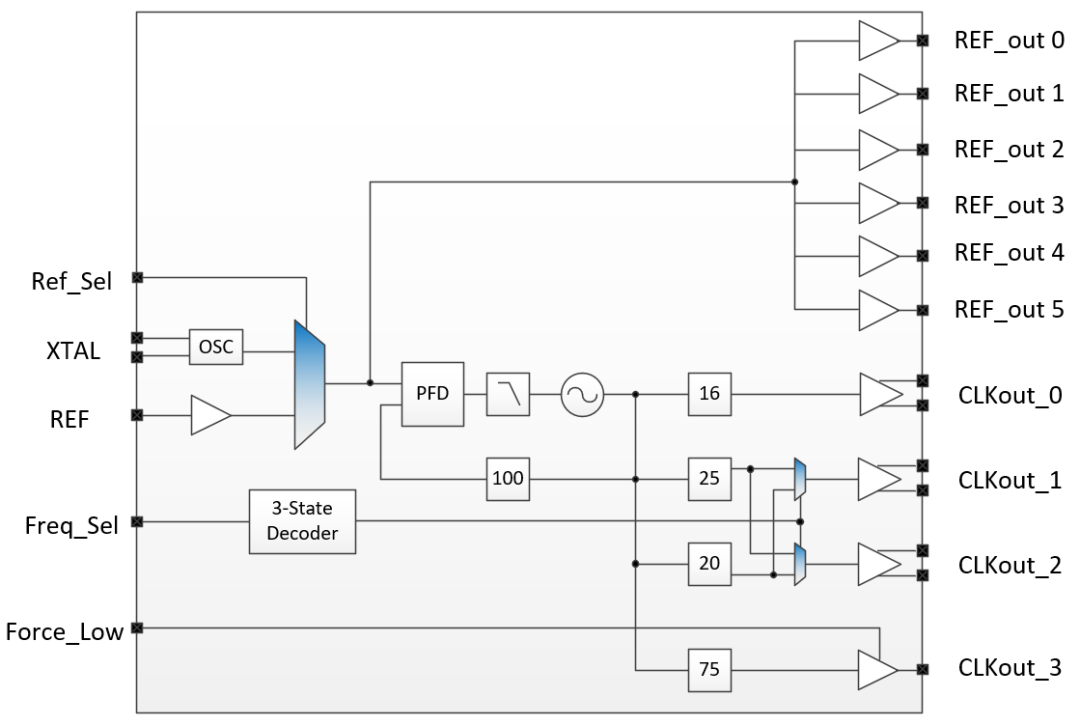

如圖為SQ82201系統框圖,SQ82201能夠通過硬件管腳選擇本地無源晶振或者外部參考時鐘。同時也支持通過硬件管腳選擇輸出頻點組合以及輸出使能。

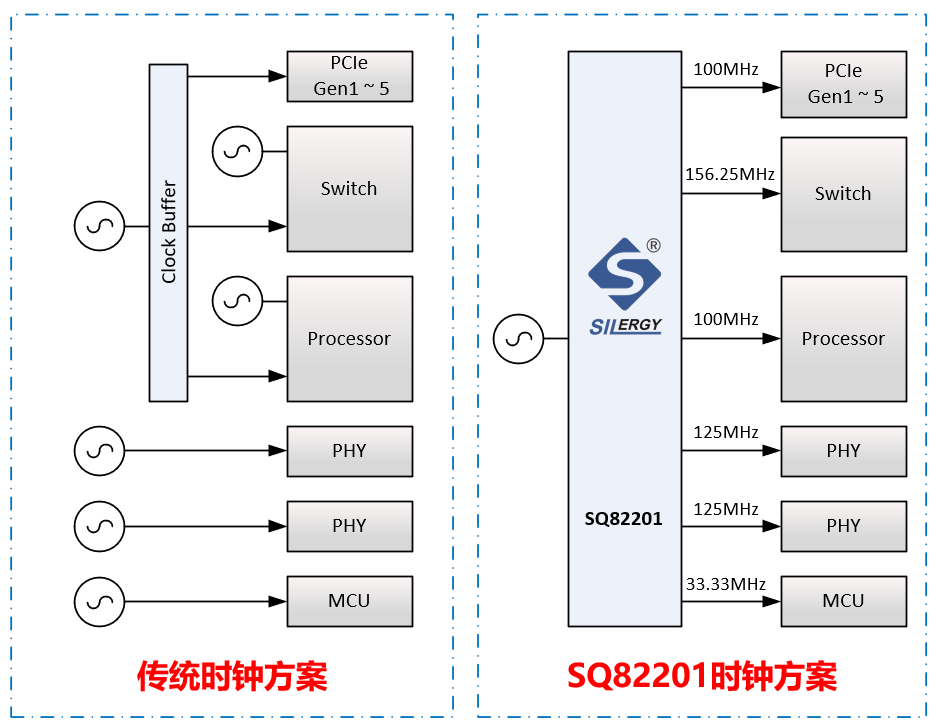

傳統的系統設計中,各個數字芯片需要的工作時鐘信號頻率各不相同。在設計中采用多個獨立的晶振時鐘源給各個數字芯片提供時鐘信號,往往會造成系統成本高,電路板面積大,設計復雜,且會產生各芯片間時鐘無法同步的問題,給系統設計帶來額外的開銷。

當系統采用SQ82201時鐘發生器,即可通過其中的高性能高頻VCO鎖定輸入選定的參考時鐘。同時產品內部集成整數分頻器,可實現輸出多路頻率各不相同的高性能時鐘,滿足系統多個芯片的時鐘頻點和性能需求。高集成度的時鐘發生器,能夠進一步縮小芯片及外圍電路尺寸,有助于滿足現有和未來的基站通信的設計需求。

三. 應用場景

在衡量時鐘信號質量時經常會提到抖動和相位噪聲,二者分別從時域和頻域的維度表征時鐘信號短期頻率穩定度。

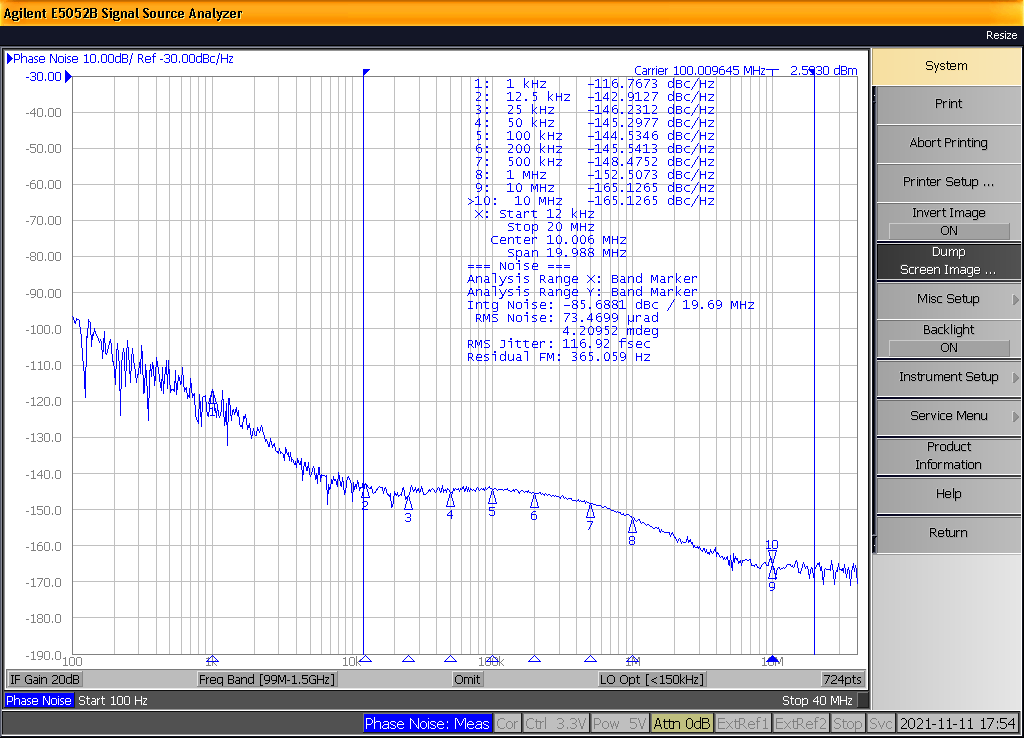

SQ82201差分輸出抖動分別如下所示:

156.25MHz: 109fs (12kHz~20MHz)

100MHz: 116fs (12KHz~20MHz)

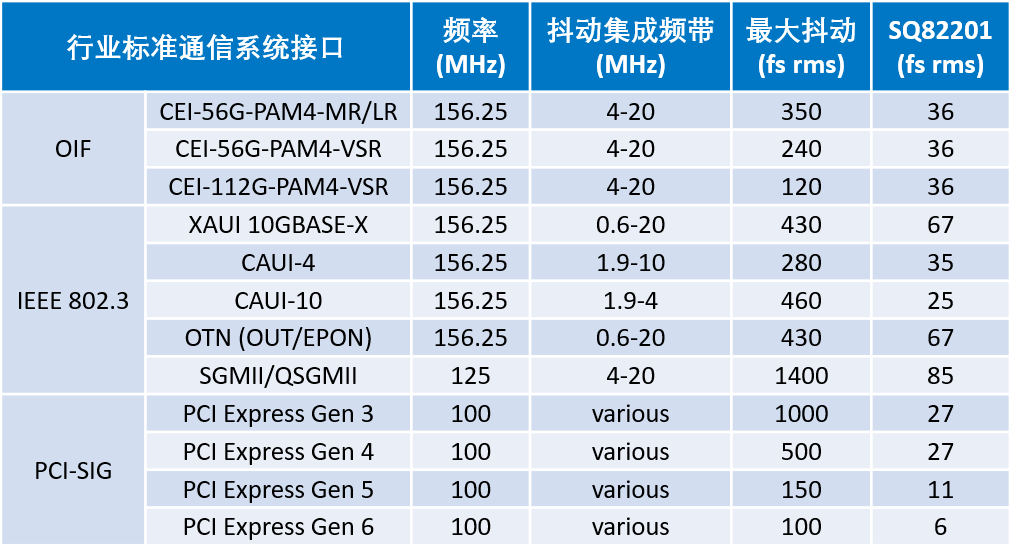

目前主流的數據通信系統中,由于各個系統的數據速率、收發通道時鐘恢復電路的帶寬不同,對于鏈路時鐘抖動的要求和積分帶寬會略有不同。

SQ82201優越的抖動性能,符合當前所有主流通信系統時鐘抖動的要求,為客戶提供高集成度,極簡外圍電路的時鐘發生器解決方案,有效滿足5G通信等應用領域的時鐘同步需求。

審核編輯黃宇

-

數據通信

+關注

關注

2文章

430瀏覽量

33737 -

5G

+關注

關注

1353文章

48380瀏覽量

563443 -

矽力杰

+關注

關注

3文章

61瀏覽量

1141

發布評論請先 登錄

相關推薦

機載數據通信終端模擬系統設計Design of Airbor

數據通信的基本概念

無線移動數據通信,無線移動數據通信是什么意思

數據通信,數據通信原理是什么?

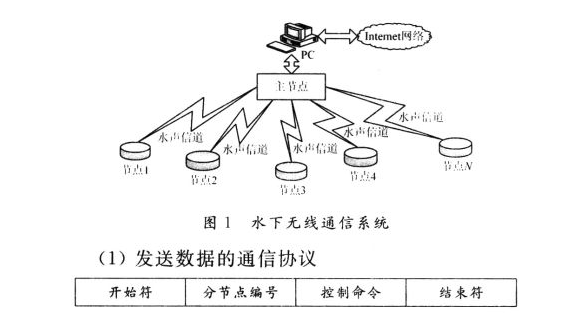

數據通信協議的簡介_數據通信協議有哪些

詳談數據通信的傳輸損耗分類和原理

SILERGY矽力杰數據通信的“指揮官”!

SILERGY矽力杰數據通信的“指揮官”!

評論