系統(tǒng)芯片 (Sxstem on Chip,SoC)通過軟硬件結(jié)合的設(shè)計和驗證方法,利用芯核復(fù)用及先進制造工藝,將多個原本獨立的功能(如邏輯電路、存儲器、混合信號和微處理器等)集成到單一芯片上,具有高集成度、高速度、體積小、成本低、功耗低等優(yōu)點。系統(tǒng)級封裝( System in Package, SiP)與SoC 不同的是,SiP 是采用不同芯片進行并排或疊加的封裝方式,而 SoC 則是將多個功能模塊集成在單芯片上。

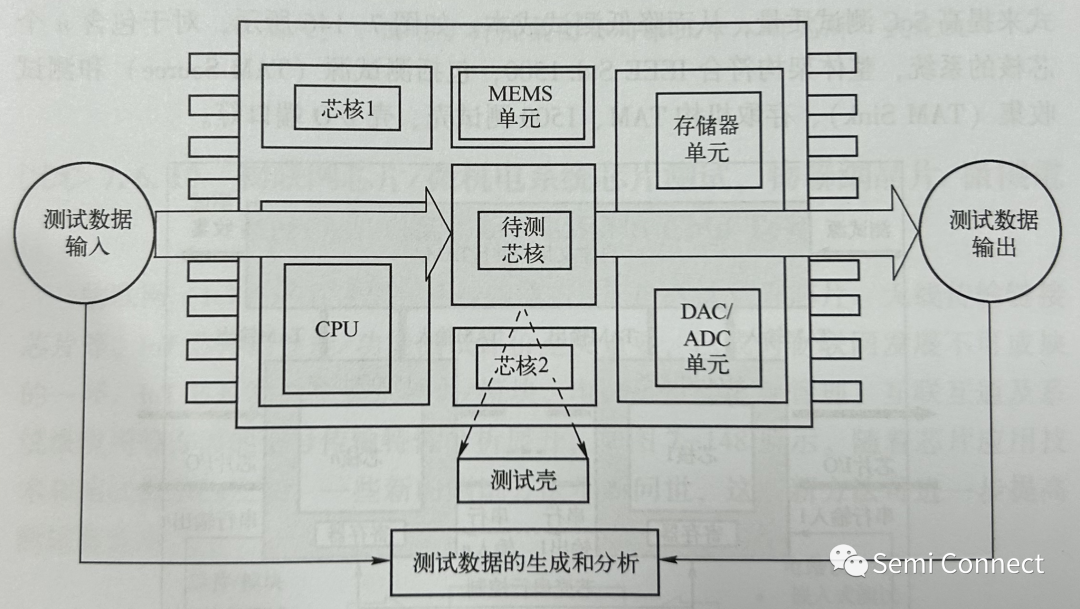

SoC 設(shè)計是一種基于嵌人式芯核的設(shè)計,其測試的關(guān)鍵是核復(fù)用帶來的核測試復(fù)用問題。另外,SoC 集成了不同來源、不同類型、不同設(shè)計的芯核,測試時還需要解決測試數(shù)據(jù)輸人和輸出的有效傳輸、嵌人式芯核互異性等問題;此外在內(nèi)核測試的基礎(chǔ)上,還要完成芯核互連和系統(tǒng)級測試。圖所示的是 SoC 內(nèi)嵌芯核測試訪問機制。由圖可見,它是通過訪問測試殼實現(xiàn)對芯核的測試存取的。

為了解決基于核的SoC 測試問題,必須建立 SoC 測試隔離、測試存取、測試控制和測試觀察的規(guī)范和標(biāo)準(zhǔn),如IEEE制定的 IEEE Std. 1149.1 (Test AccessPort and Boundary - Scan Architecture , IEEE Std. 1500 ( Testability Method forEmbedded Core - based Integrated Circuits) F IEEE Std. 1450 ( Test InterfaceLanguage ( STIL) for Digital Test Vector Data)等一系列的標(biāo)準(zhǔn)。

TEEE Std. 1149. 1 標(biāo)準(zhǔn)自1990年公布以來,邊界掃描技術(shù)已被廣泛接受和重視。掃描鏈將邏輯測試存取端子整合到電路內(nèi)部,通過掃描操作提供可控制性和可觀測性的人口,使電路的物理測試存取端子得以簡化。在此基礎(chǔ)上,JTAC還推出了 IBEE Std. 1149.4(用于數(shù)模混合電路)和IEEE Std. 1149.7(減少了測試引腳)等標(biāo)準(zhǔn)。

IEEE Std. 1450 標(biāo)準(zhǔn)旨在提供一個通用的測試向量圖形描述語言,該語言在EDA 仿真工具和 ATE 上不需要轉(zhuǎn)換即可使用. 建立了 EDA 和 ATE 之間的無縫鏈接。其中,IEEE Std. P1450.1 提出了標(biāo)準(zhǔn)測試接口語言(Standard TestInterface Language),該語言將替代傳統(tǒng) BDA 仿真的 VCD、WGL波形文件等。

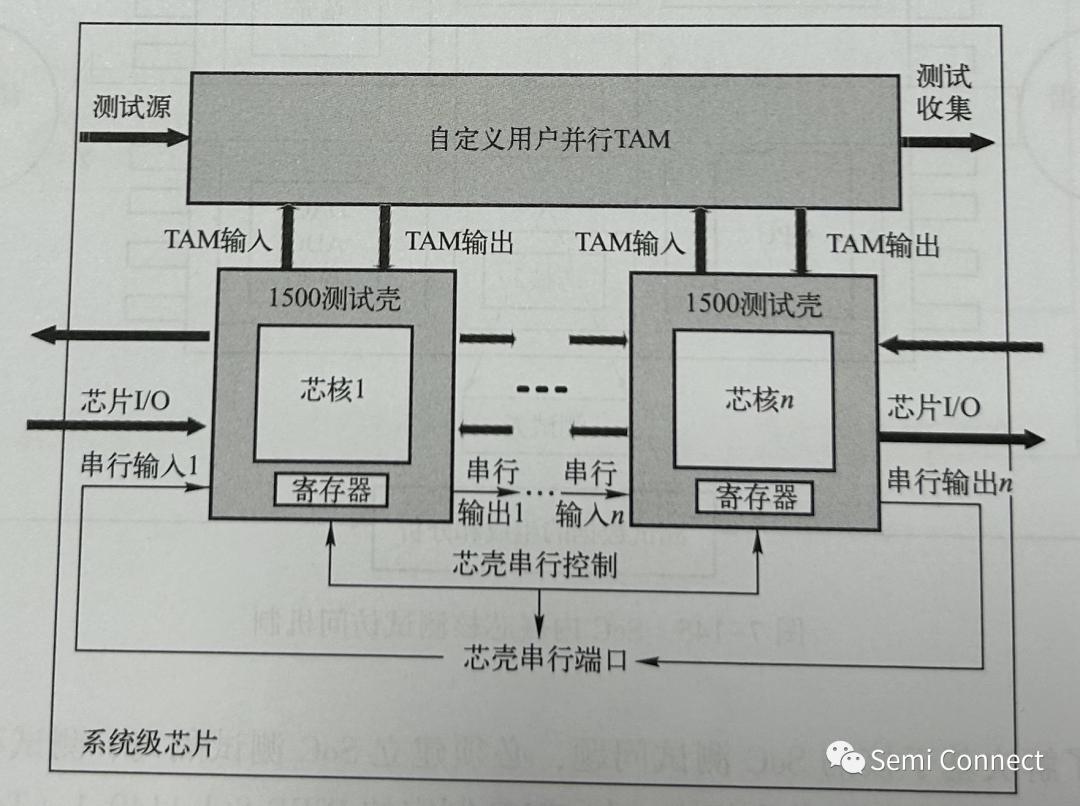

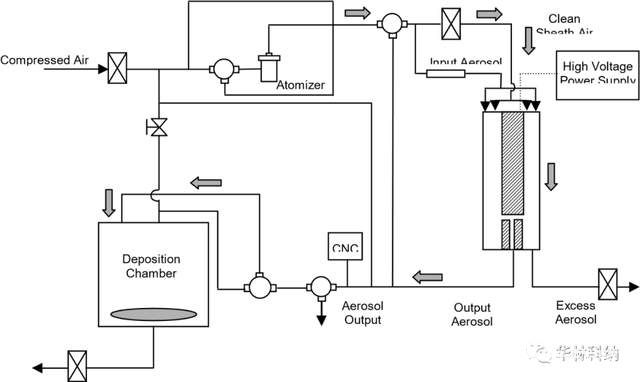

IEEE Std. 1500 提出了一種可擴展的標(biāo)準(zhǔn)架構(gòu),適用于實現(xiàn)嵌人式內(nèi)核和相關(guān)電路的測試復(fù)用和集成。IEEE Std. 1500 提出的標(biāo)準(zhǔn)架構(gòu)具有串行和并行測試訪問機制(Test Access Mechanism),以及豐富的指令集,可用于 SoC 內(nèi)核互連和系統(tǒng)測試。此外,IBBE Std. 1500 定義丁支持內(nèi)核隔離和保護的特性,通過改進設(shè)計文件自動轉(zhuǎn)化效率,促進可測性測試設(shè)計 (DFT)技術(shù),以區(qū)通過改進訪問方式來提高 SoC 測試質(zhì)量,從而降低測試成本。如圖所示,對于包含幾個芯核的系統(tǒng),整體架構(gòu)符合 IEEE Std. 1500,包括測試源(TAM Source)和測試收集(TAM Sink)、存取機構(gòu)TAM、1500 測試殼、殼V/0端口等。

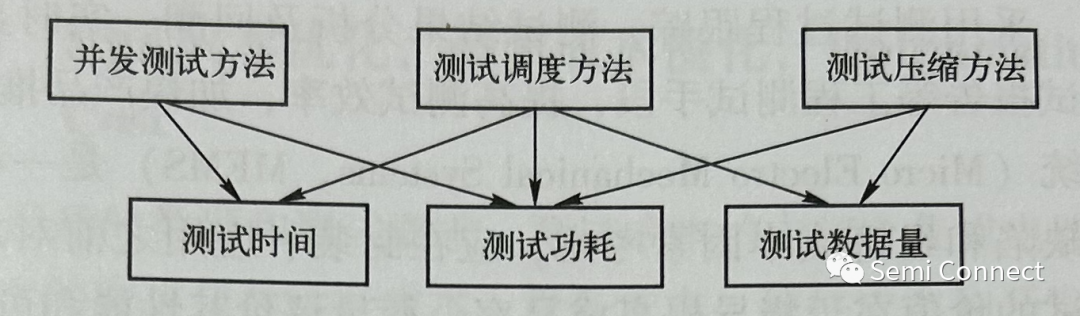

IEEE 標(biāo)準(zhǔn)可有效地解決 SoC 的測試實現(xiàn)。SoC測試的另一個問題是測試成本。降低SoC測試成本的有效方法是減少測試時間,這一點可采用并發(fā)測試測試調(diào)度和測試壓縮等方法得以實現(xiàn)。并發(fā)測試通過同時對被測 SOC 中的多個功能模塊進行測試,從而將測試時間減少到最長單路徑時間。

測試調(diào)度通過合理分配嵌人式芯核的測試集和測試存取機制,從而達到多核測試、減少總線冗余時間和避免測試沖突的目的。SoC 集成度和復(fù)雜度的日益提高,以及高故障覆蓋率的需求,導(dǎo)致測試數(shù)據(jù)日益劇增,測試壓縮通過設(shè)計優(yōu)化測試激勵響應(yīng)壓縮方法和測試策略,達到減少測試存儲通道數(shù)據(jù)量、降低測試功耗和縮短測試時間的效果。圖所示的是測試優(yōu)化方法和目標(biāo)。

審核編輯:劉清

-

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42581 -

存儲器

+關(guān)注

關(guān)注

38文章

7455瀏覽量

163623 -

微處理器

+關(guān)注

關(guān)注

11文章

2247瀏覽量

82331 -

SoC設(shè)計

+關(guān)注

關(guān)注

1文章

148瀏覽量

18764 -

sip封裝

+關(guān)注

關(guān)注

4文章

64瀏覽量

15503

原文標(biāo)題:系統(tǒng)芯片測試,系統(tǒng)晶片測試, SoC Test

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Smiths Interconnect正式推出高性能Volta系列探針頭,用于晶片級芯片封裝測試

晶片驗證測試及失效分析pdf

***國家晶片系統(tǒng)設(shè)計中心VHDL培訓(xùn)教材

晶片邊緣蝕刻機及其蝕刻方法

倒裝芯片和晶片級封裝技術(shù)及其應(yīng)用

Aigtek高壓放大器在壓電雙晶片動力學(xué)研究中的應(yīng)用

半導(dǎo)體工藝—晶片清洗工藝評估

LED封裝晶片便攜式推拉力測試機

系統(tǒng)芯片與晶片測試

系統(tǒng)芯片與晶片測試

評論