點擊上方藍字關注我們

采樣就是采集模擬信號的樣本。通常采樣指的是下采樣,也就是對信號的抽取。其實,上采樣和下采樣都是對數字信號進行重采,重采的采樣率與原來獲得該數字信號的采樣率比較,大于原信號的稱為上采樣,小于的則稱為下采樣。上采樣是下采樣的逆過程,也稱增取樣或內插。

本文介紹一種使用Virtex-6器件和WebPACK工具實現實時四倍上采樣的方法。

許多信號處理應用都需要進行上采樣。從概念上講,對數據向量進行M倍上采樣的簡單方法是用實際頻率分量數的(M-1)倍個零填充數據向量的離散傅里葉變換(DFT)[1],然后將零填充向量轉換回時域[1,2]。但這種方法計算量很大,因此不能在FPGA內部高效實現。在本文介紹的高效并行實時上采樣電路中,每個ADC時鐘可產生M個上采樣值,其中M是所需的上采樣倍數。在我們的Virtex-6 XC6VLX75T FPGA實現方案中,上采樣倍數M為4,可以作為較普遍方法的一個實例。

我們并行上采樣方法的總體概念源于某些作者所稱的“窗口SINC插值”,這種方法在文獻資料[3,4]中有一些非常精彩的專文介紹。

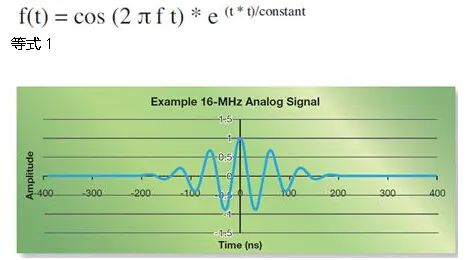

為了更好的說明,現以圖1中所示的16MHz模擬信號為例。該信號的表達式為:

圖1 - 展示上采樣過程的16MHz信號實例

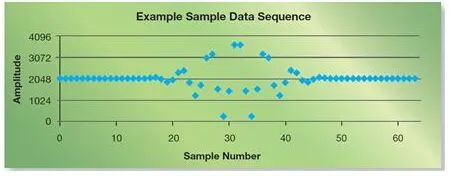

如果用12位ADC以80MHz的頻率對圖1所示的信號進行采樣或量化,輸入范圍為ADC完整輸入范圍的97.7%,則每個信號周期只能采樣五次,產生的樣本數據序列如圖2所示。如果對該示例數據序列進行四倍上采樣,則有效采樣率為320MHz,每個信號周期能夠提供20個樣本。雖然您可以使用本文介紹的方法進行更高倍數的上采樣,但為了說明起見我們還是使用M=4的上采樣。

圖2 - 本圖是12位ADC,輸入范圍為ADC完整輸入范圍的97.7%,用80MHz或每周期五次頻率對圖1的模擬信號采樣得到的樣本數據序列實例。

當然,還可以通過直接在ADC生成的數據序列的每個實際樣本值之間插入(M-1)個零來獲得上采樣數據向量及所需的樣本數(公認效果較差)。該“零插入步驟”對應于復制頻域中的原始信號頻譜。通過對得到的“零填充”時域信號進行低通濾波,就能去除頻域中所需頻譜的“復本”,從而獲得上采樣數據向量。

FIR濾波器設計

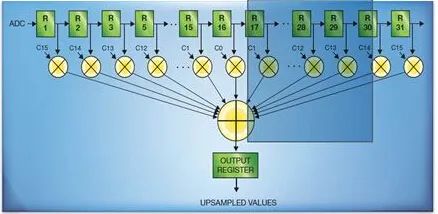

頻域中的理想(磚墻式)低通濾波器相當于在時域中用無限域Sinc函數作卷積。因此為近似化所需的卷積運算,可讓前述的零填充時域信號通過速率為ADC時鐘頻率M倍的對稱低通FIR濾波器,該濾波器拓撲結構與圖3所示的示例31抽頭FIR濾波器相同。用這種方法,我們可以實時生成上采樣數據向量。圖3中的R1、R2、...、R31代表速率為ADC時鐘頻率M倍的寄存器,C0、C1、…、C15代表FIR濾波器的系數。

圖3 - 當濾波器工作在基本ADC時鐘頻率的M倍頻率時,零插入步驟中使用31抽頭FIR濾波器每時鐘周期可生成一個上采樣數據值

需要說明的是,圖3所示的FIR濾波器中的大部分寄存器在任何特定時鐘間隔內都會包含0,而非實際的樣本數據。以M=4為例,當R1包含實際樣本數據時,R2、R3和R4將包含0。當R1包含實際樣本數據時,R5、R9、R13、R17、R21、R25和R29也將包含實際樣本數據,其余的寄存器將包含0。在下一時鐘間隔中,R2、R6、R10、R14、R18、R22、R26和R30將包含實際樣本數據。

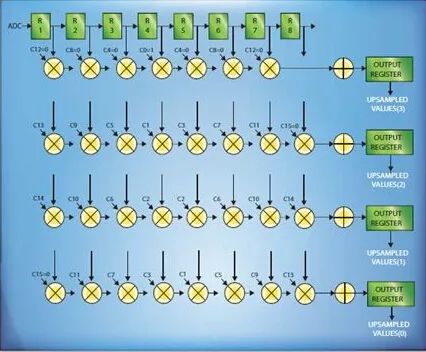

如圖3所示,由于在通過FIR濾波器的每M個樣本中有M-1個樣本為0,就M=4、使用31抽頭FIR濾波器的情況而言(如圖4所示),您可以將濾波器分解開,并行產生M個輸出。采用這種實現方案,并行FIR濾波器的工作頻率為ADC的基本時鐘頻率,而非ADC時鐘頻率的M倍。

圖4 - 通過在任何給定時鐘周期內對圖3中每四個寄存器中一個包含非零數據的寄存器進行觀察,可以拆解該濾波器,再讓濾波器在以基礎ADC時鐘頻率運行的情況下并行

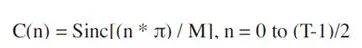

如圖4所示,您可以設定窗口SINC函數的系數Cw(n)來限度地減少實現該FIR濾波器所需的乘法器數量。對于T個抽頭的低通FIR濾波器而言,可通過下式得出系數:

等式2

這里的漢寧窗系數的計算方法為:

等式3

窗口SINC函數系數Cw(n)隨即通過對應的C(n)和H(n)值相乘即可得到,如:

等式 4

在M=4時,如果按上面介紹的方法計算31抽頭FIR濾波器的系數,令C0=1.0,C4=C8=C12=C15=0,則無需使用與圖4中這些系數有關的9個乘法器。此外,由于生成UPSAMPLED VALUE(1)每個系數會使用兩次,用戶可以“折疊”該實現方案,比如在相乘之前讓R1和R8相加,這樣就可以去掉四個乘法器。得到的設計僅使用18個乘法器每時鐘周期就可產生四個上采樣值。需要注意的是按上文介紹的設計方法,每個原始樣本值會原樣從并聯濾波器輸出。

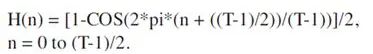

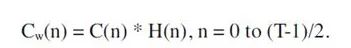

我們使用圖5所示的可綜合VHDL[5]模型評估圖4所示電路的性能。該VHDL實現方案假定樣本數據為12位,即可能來自美國模擬器件公司的AD9670八通道超聲前端集成電路的數據。濾波器系數表達為25位定點常數,以與集成到FPGA芯片上的乘法器輸入位數相匹配。來自ADC的輸入樣本先饋入與輸入引腳相連的寄存器(圖4中的R1),上采樣輸出值則使用與輸出引腳相連的寄存器。寄存器R2到R8屬芯片內部寄存器。寄存器R1到R8故意設定為15位寬度,以便為綜合后邏輯提供執行計算所需的動態余量。該設計能檢查溢出或下溢,還能將結果鉗制在有效范圍以內。

圖5 - 該VHDL源代碼使用單進程和25位定點系數實現圖4的濾波器拓撲結構。

無需流水線化

圖6顯示的是使用的WebPACK工具中提供的14.7版ISim仿真器對該VHDL模型進行仿真并將饋送圖2中的采樣/量化12位數據序列后得到的上采樣數據序列。每個原始的12位樣本均保持不變,原因上文已述。原始波形中每個實際樣本之間插入了三個新樣本。

圖6 - 該圖表顯示的是VHDL模型生成的上采樣數據序列

計算所得(上采樣所得)值與原始模擬信號中理想值之間的誤差為整個范圍的0.464%,平均誤差為整個范圍的0.070%。當然因初始量化步驟原因,在采樣/量化12位源矢量數據值中存在1/2 LSB的誤差(合整個范圍的0.012%)。

布局布線設計使用19個DSP48E1模塊,但占用的Virtex-6 Slice資源不足1%,無需流水線化即可運行在107MHz下。

我們使用WebPACK工具14.7版在XC6VLX75T-3FF484 Virtex-6 FPGA上實現這一上采樣器。布局布線設計占用該器件中288個DSP48E1模塊中的19個,但使用的Slice資源不足1%。終得到的上采樣電路能夠運行在107MHz下。無需讓濾波器流水線化即可實現這一性能。此外,我們還開發出了用流水線實現的版本,可以工作在217MHz以上。

雖然XC6VLX75T-3FF484是Virtex-6系列中的端成員,但芯片上仍集成有288個帶有25x18位乘法器的DSP48E1模塊。換言之,在理論上足以實現15個圖4所示的并行上采樣FIR濾波器。我們制作的原型環形陣列超聲系統使用了八套以80MHz的頻率運行在XC6VLX75T FPGA上的上采樣器,在波束成形之前對來自八通道Analog Devices AD9670超聲前端芯片的數據進行上采樣處理。在該系統中,上采樣器按仿真預測的方式運行,在以AD9670 ADC的基本時鐘頻率80MHz運行的情況下,能使用上采樣到320MHz的數據實時完成波束成形。

型Virtex-6 FPGA器件XC6VSX475T包含有2,016個25x18位乘法器,在理論上一個芯片就可以實現106個圖4所示類型的上采樣濾波器。

只要濾波器使用本文介紹的高效并行拓撲結構進行設計,就能夠使用實現在工作頻率為107MHz的XC6VLX75T-3FF484 FPGA上的FIR濾波器完成M=4倍的實時上采樣。原始數據樣本將原封不動通過濾波器,并行產生(M-1)=3個上采樣值。這種簡明的FIR濾波器設計方法無需借助復雜精密的濾波器設計工具就能提供優異的結果。本文介紹的思路稍加拓展,就可以使用更大的因數進行上采樣,或者是使用抽頭數更多的FIR濾波器降低計算出的上采樣值的誤差。

這種簡明的FIR濾波器設計方法無需借助復雜精密的濾波器設計工具就能提供優異的結果。

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:使用FPGA實現高效并行實時上采樣

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602037

原文標題:使用FPGA實現高效并行實時上采樣

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SXRTO(采樣擴展實時示波器)的5W1H

使用FPGA實現高效并行實時上采樣

使用FPGA實現高效并行實時上采樣

評論