DC/DC電源指的是直流轉直流的電路,有升壓降壓兩種電路,按理來說,LDO也是DCDC電源,但行業內只認為以開關形式實現的電源為DC/DC電源。

一,DC/DC基本拓撲

Buck、Boost型

電感電壓伏秒平衡定律

一個功率變換器,當輸入、負載和控制均為固定值時的工作狀態,在開關電源中,被稱為穩態。穩態下,功率變換器中的電感滿足電感電壓伏秒平衡定律:對于已工作在穩態的DC/DC功率變換器,有源開關導通時加在功率電感上的正向伏秒一定等于有源開關截至時加在該電感上的反向伏秒。

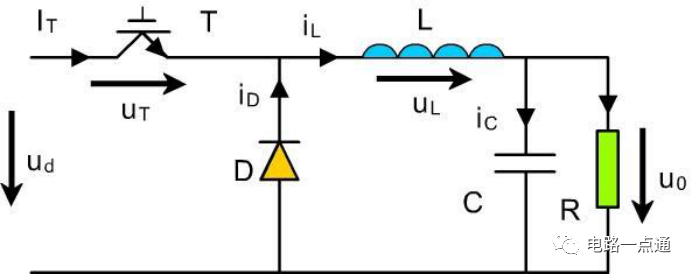

1. BUCK降壓型

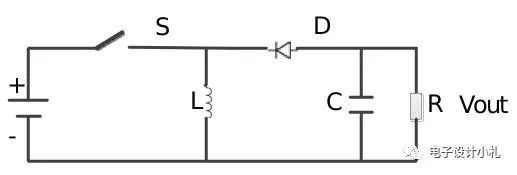

先來看一下原理圖

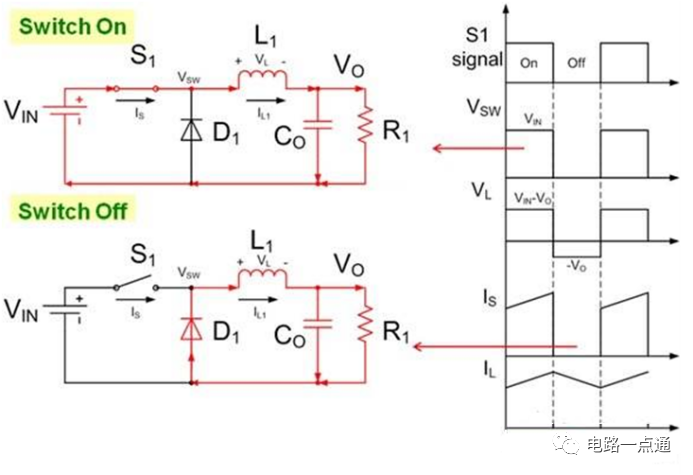

當PWM驅動高電平使得NMOS管S1導通,忽略MOS管的導通壓降,電感電流呈線性上升,此時電感正向伏秒為:V*Ton=(Vin-Vo)*Ton

當PWM驅動低電平使得NMOS管S1截至時,電感電流不能突變,經過續流二極管形成回路(忽略二極管壓降),給輸出負載供電,此時電感電流下降,此時電感反向伏秒為:V*Toff=Vo*(Ts-Ton)

根據電感電壓伏秒平衡定律可得:(Vin-Vo)*Ton=Vo*(Ts-Ton)

即 Vo=D*Vin (D為占空比)

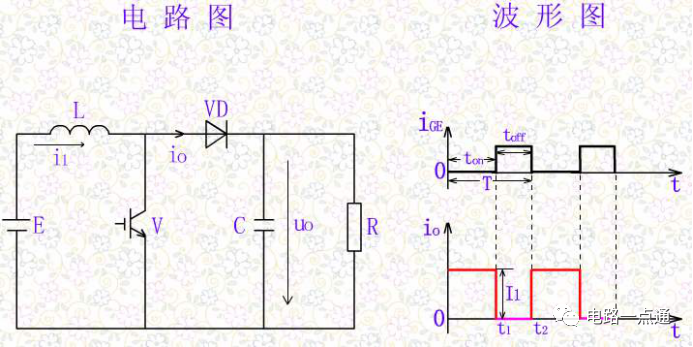

2.BOOST升壓型

和BUCK電路類似的分析方法,當MOS管導通時,電感的正向伏秒為:Vin*Ton;當MOS管截至時,電感的反向伏秒為:(Vo- Vin)*(Ts-Ton)

根據電感電壓伏秒平衡定律可得:Vin*Ton=(Vo- Vin)*(Ts-Ton)

即 Vo=Vin/(1-D)

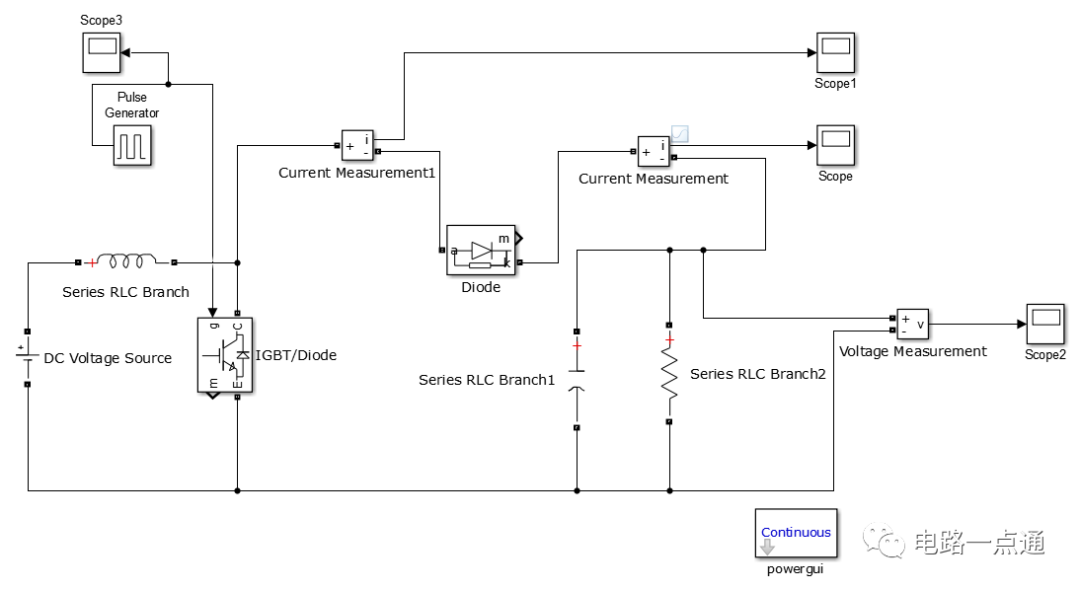

matlab仿真圖

仿真Vout升壓過程

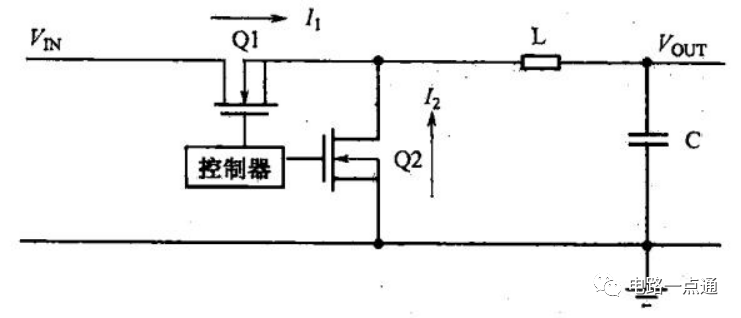

3.同步整流技術

由于二極管導通時至少存在0.3V的壓降,因此續流二極管D所消耗的功率將會稱為DC/DC電源主要功耗,從而嚴重限制了效率的提高。為解決該問題,以導通電阻極小的MOS管取代續流二極管。然后通過控制器同時控制開關管和同步整流管,要保證兩個MOS管不能同時導通,負責將會發生短路。

二、DC/DC電源調制方式

DC/DC電源屬于斬波類型,即按照一定的調制方式,不斷地導通和關斷高速開關,通過控制開關通斷的占空比,可以實現直流電源電平的轉換。DC/DC電源的調制方式有三種:PWM方式、PFM方式、PWM與PFM的混合方式。

1.PWM(脈沖寬度調制)

PWM采用恒定的開關頻率,通過調節脈沖寬度(占空比)的方法來實現穩定電源電壓的輸出。在PWM調制方式下,開關頻率恒定,即不存在長時間被關斷的情況。

優點:噪聲低、效率高,對負載的變化響應速度快,且支持連續供電的工作模式。

缺點:輕負載時效率較低,且電路工作不穩定,在設計上需要提供假負載。

2.PFM(脈沖頻率調制)

PFM通過調節開關頻率以實現穩定的電源電壓的輸出。PFM工作時,在輸出電壓超過上閾值電壓后,其輸出將關斷,直到輸出電壓跌落到低于下閾值電壓時,才重新開始工作。

優點:功耗較低,輕負載時,效率高且無需提供假負載。

缺點:對負載變化響應較慢,輸出電壓的噪聲和紋波相對較大,不適合工作于連續供電方式。

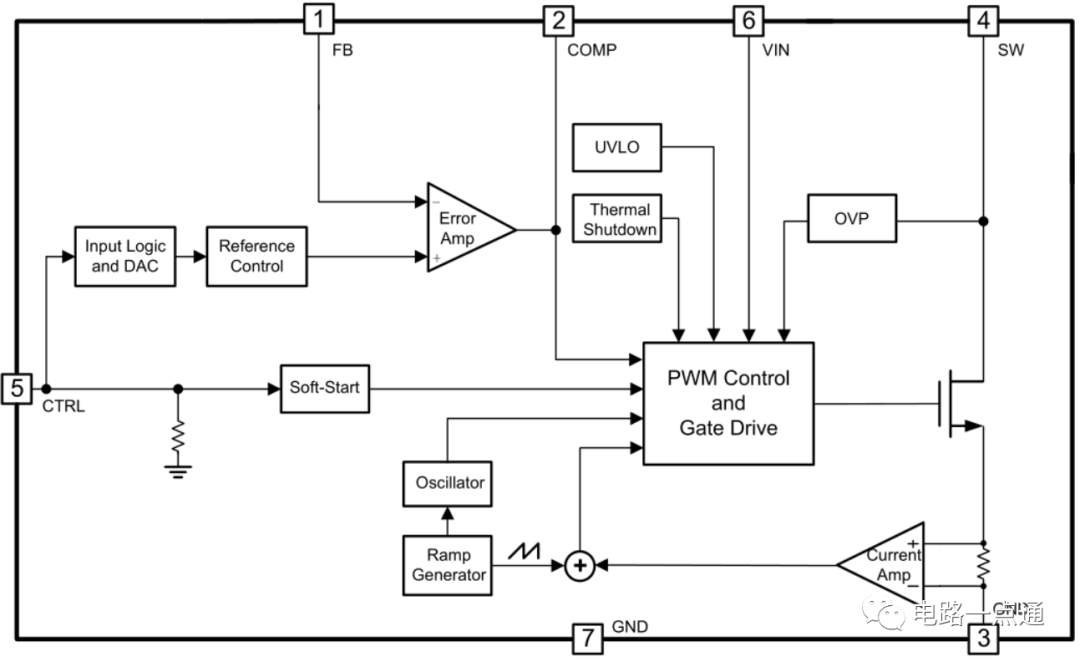

三、DC/DC芯片的內部構造

接下來我們來看看DC/DC電源芯片內部的單元模塊,并且給大家看看基本拓撲與電源芯片的聯系,先來看一個圖。

一款電源背光IC的內部原理框圖

誤差放大器的作用就是將反饋電壓(FB引腳電壓)與基準電壓(200mv)的差值進行放大,然后再用該信號去控制PWM輸出信號的占空比。

2.Thermal Shutdown 溫度保護:當溫度高于限定值,芯片停止工作。

3.soft start軟啟動電路:用于電源啟動時,減小浪涌電流,使輸出電壓緩慢上升,減小對輸入電源的影響。

四、DC/DC電路的硬件設計參數選擇標準

1.設置輸出電壓:先選擇合適的R2,R2過小會導致靜態電流過大,從而導致加大損耗;R2太大會導致靜態電流過小,而導致FB引腳的反饋電壓對噪聲敏感,一般在數據手冊中有推薦值范圍參考。選定R2,根據輸出電壓計算R1的值,R1=((Vout-Vref)/Vref)*R2。電壓選定以后,開關電源會自動調節占比總,取得我們想要的電壓。

2.電感:電感的選擇要滿足直到輸出最小規定電流時,電感電流也保持連續。在電感選取過程中需要綜合輸出電流、紋波、體積等多個因素進行考慮。較大的電感將導致較小的紋波電流,從而導致較低的紋波電壓,但是電感越大,將具有更大的物理占用面積,更高的串聯電阻和更低的飽和電流。電感感值越小,開關電源PWM信號的頻率就越高,一般開關電源很少有好過10MHz的開關頻率,大部分在100K~1MHz之間,所需要的功率電感值在2.2uH~22uH之間。

3.輸出電容:輸出電容的選擇主要是根據設計中所需要的輸出紋波的要求來進行選取。電容產生的紋波:相對很小,可以忽略不計;電容等效電感產生的紋波:在300KHz~500KHz以下,可以忽略不計;電容等效電阻產生的紋波:與ESR和流過電容電流成正比,該電流紋波主要是和開關管的開關頻率有關,基本為開關頻率的n次諧波,為了減少紋波,讓ESR盡量小。需要在開關電源輸出端增加pF級電容,減少百兆級噪聲的干擾。

免責聲明:本文轉自網絡,版權歸原作者所有,如涉及作品版權問題,請及時與我們聯系,謝謝!

-

模擬技術

+關注

關注

17文章

469瀏覽量

39708 -

張飛電子

+關注

關注

54文章

175瀏覽量

12576

原文標題:(DC/DC)Buck、Boost電路原理、電源調制方式、芯片內部、設計參數

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

(DC/DC)Buck、Boost電路原理、電源調制方式、芯片內部、設計參數

(DC/DC)Buck、Boost電路原理、電源調制方式、芯片內部、設計參數

評論