目錄/contents

● 速度-面積互換原則概述

● 設計思想1:乒乓操作

● 設計思想2:串/并轉換

● 設計思想3:流水線設計

● 設計思想4:邏輯復制與模塊復用

01速度-面積互換原則概述

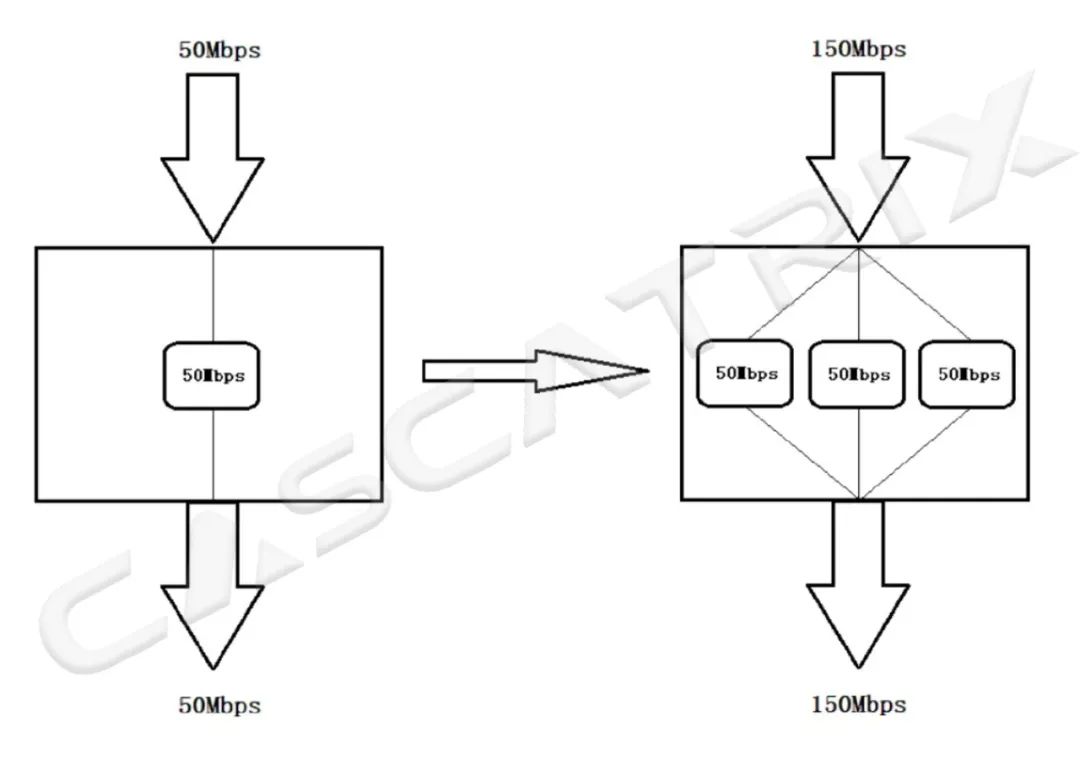

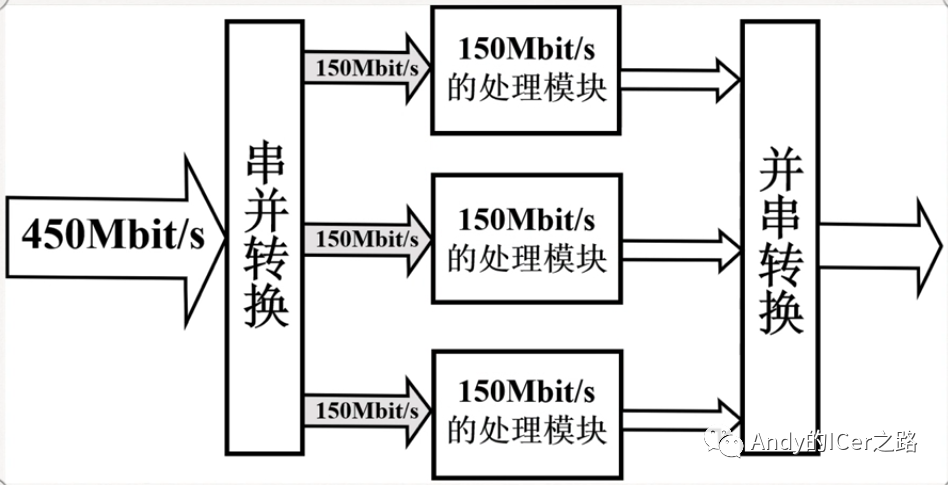

速度-面積互換原則是貫穿FPGA設計的重要原則:速度是指工程穩定運行所能達到的最高時鐘頻率,通常決定了FPGA內部寄存器的運行時序;面積是指工程運行所消耗的資源數量,通常包括觸發器(Flip-Flop)和查找表(Look Up Table)等資源。在FPGA設計過程中,速度的提高通常以面積擴增為代價,面積的縮減通常以速度的降低為代價。如何權衡二者的性能要求,在滿足時序(速度)要求的前提下盡可能節約邏輯資源(面積),是FPGA設計過程中需要考慮的重點。

例如,工程中占用一定的邏輯資源可以實現50Mbps的數據吞吐量,采用三倍的資源實現相應的功能,通過并行處理則可以實現150Mbps的數據吞吐量,從而實現用面積換速度的操作。

速度-面積互換原則的常用設計思想包括:乒乓操作、串/并轉換、流水線設計、邏輯復制與模塊復用。

02設計思想1:乒乓操作

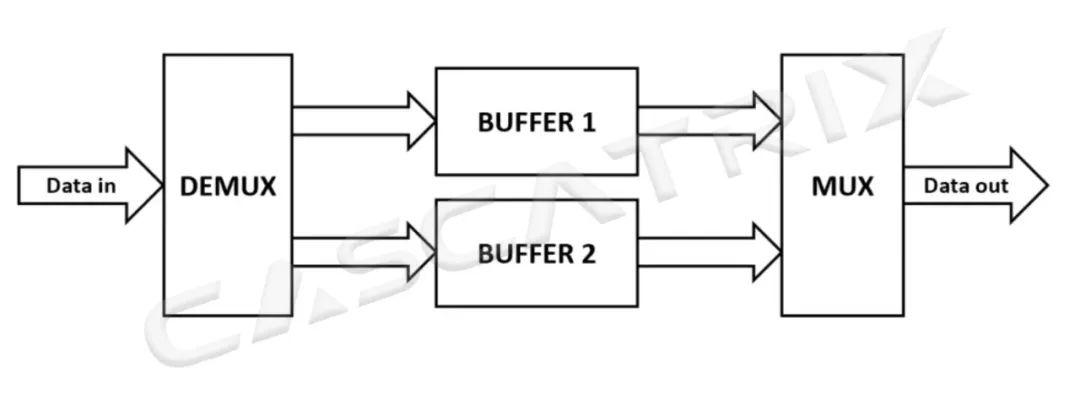

乒乓操作是一種常用的犧牲面積換取速度設計思想,常用于圖像數據傳輸等數據量較大且實時性要求較高的場景。乒乓操作的具體流程為:分配輸入數據進入多路緩存,常用緩存模塊包括RAM、FIFO等,隨后依次從多路緩存中輸出數據,從而保證數據高速傳輸的連續性。

以上述圖中所示模塊為例:在第一個周期,輸入數據流Data in通過DEMUX分配緩存在BUFFER1模塊中;在第二個周期,輸入數據流Data in通過DEMUX分配緩存在BUFFER2模塊中,同時,MUX將BUFFER1模塊中的緩存數據輸出到后續處理模塊;在第三個周期,輸入數據流Data in再次通過DEMUX分配緩存在BUFFER1模塊中,同時,MUX將BUFFER2模塊中的緩存數據輸出到后續處理模塊...如此反復循環切換,通過乒乓操作完成數據的緩沖與傳輸,保證數據流無停頓地持續傳輸。

乒乓操作經常應用于外部接口傳輸以圖像數據為代表的按幀劃分的數據。在圖像數據傳輸過程中,當前幀存入緩存BUFFER1的同時,顯示器用于顯示BUFFER2的圖像數據幀;下一幀存入BUFFER2的同時,顯示器用于顯示BUFFER1的圖像數據幀。乒乓操作保證顯示器瞬間完成圖像的切換,提高圖像數據傳輸的效率和穩定性,特別是在通信環境較差的情況下。

03設計思想2:串/并轉換

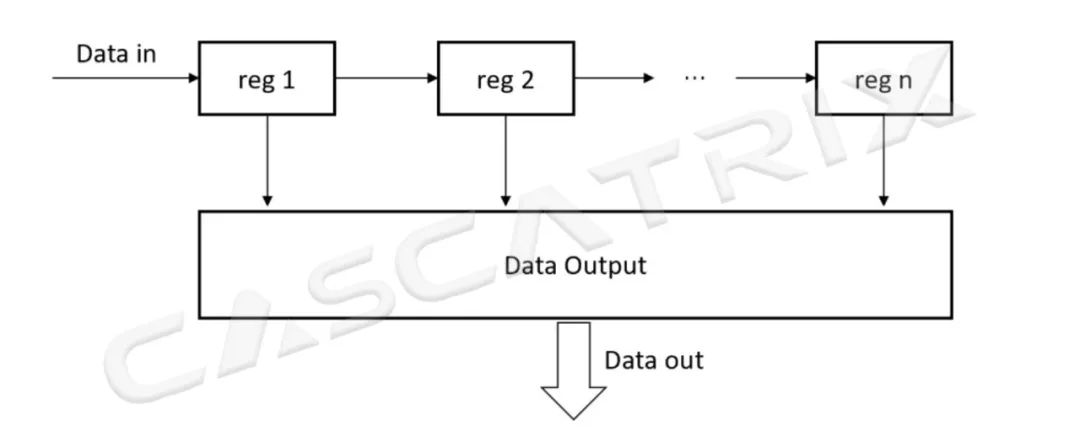

串/并轉換是體現速度-面積互換思想的另一種設計方案,在高速數據流處理中發揮重要的作用。串/并轉換通常將數據分成多個較小的數據塊,這些數據塊可以同時并行傳輸,從而提高數據的傳輸速率。

串/并轉換的實現方法多種多樣,根據數據數量的不同,可以選用寄存器、RAM、FIFO等實現。對于數量較小的設計通常可以采用移位寄存器實現。

以上述圖中所示模塊為例:串行輸入數據data in通過n個移位寄存器后,通過位寬為n的并行總線輸出數據data out。移位過程通常依賴于時鐘進行同步,因此,完成一個周期的n位串/并轉換需要消耗n個串行時鐘周期。例如,串行傳輸時鐘頻率為100MHz,若將串行數據轉為4bit并行數據輸出,并行傳輸的時鐘頻率將降低至25MHz,這是串入并出的基本設計思想。

串/并轉換通過犧牲面積換取數據帶寬,提高數據傳輸的吞吐量,從一定程度上提高了數據的傳輸速率,同樣體現出速度-面積互換思想。

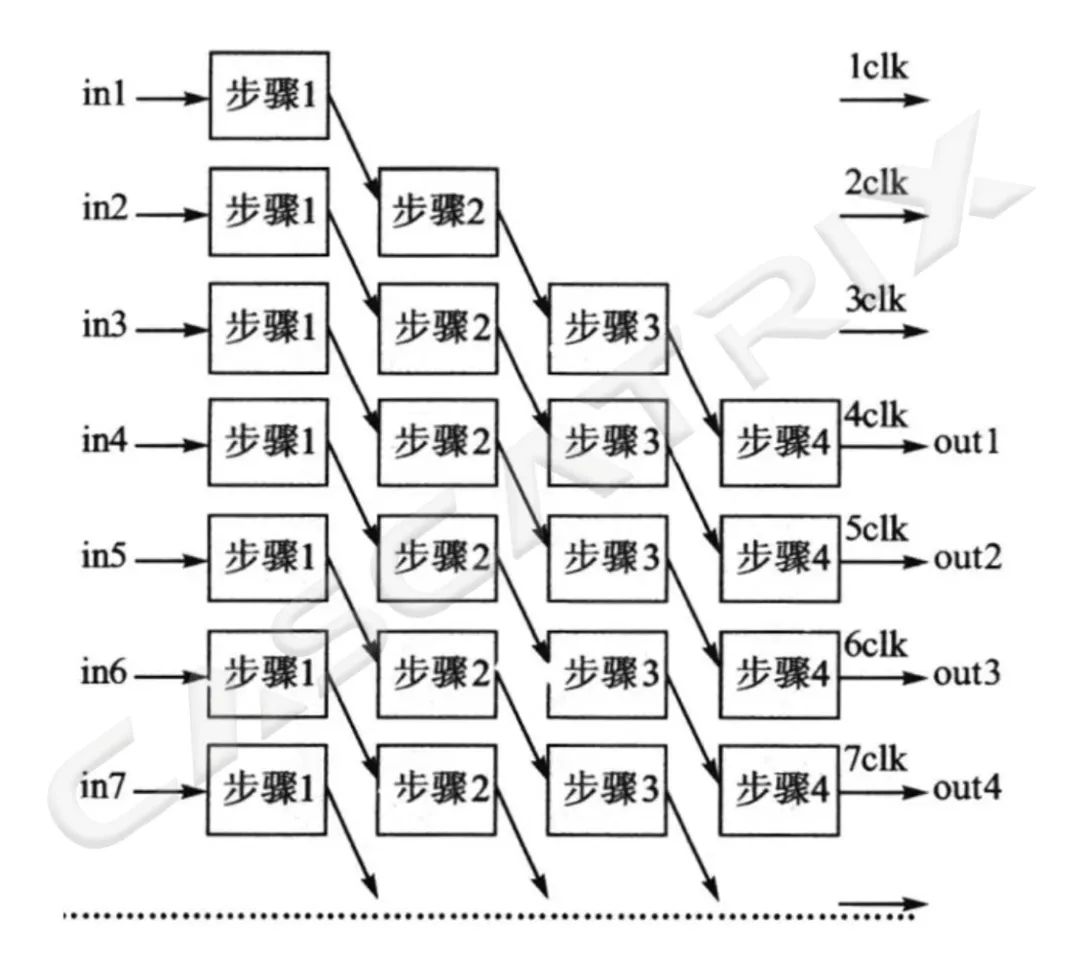

04設計思想3:流水線設計

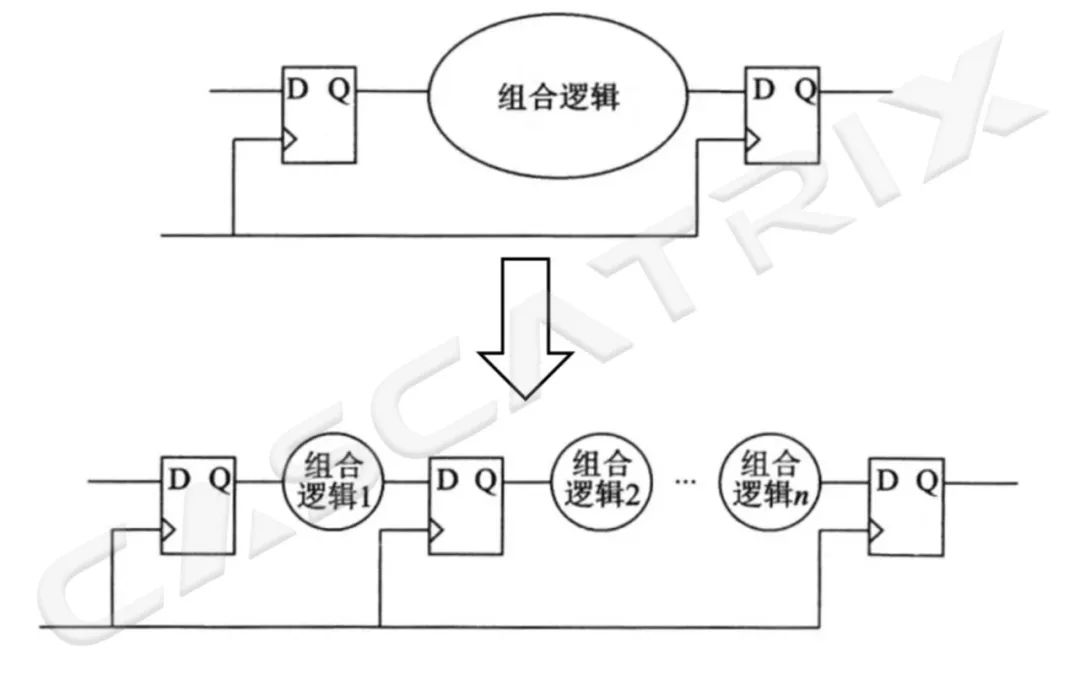

流水線設計通過處理模塊復制的方法提高數據流的處理速度,在高速信號處理領域發揮著重要作用。流水線設計主要應用于單向數據處理過程,即前一個模塊的輸出可以直接作為下一個模塊的輸入,運算處理不涉及反饋和迭代,那么可以考慮采用流水線設計方法提高系統的工作頻率。

以上述圖中所示模塊為例,當原設計在一個時鐘周期內實現一個較大的組合邏輯時,通過切割可以將較大的組合邏輯分解為多個較小的組合邏輯,分割后的組合邏輯需要在多個時鐘周期內完成。盡管分割后的設計需要更多的時鐘周期,但是這部分邏輯運行的時鐘周期會有明顯的提升,系統時鐘頻率提升后的耗時總體上優于提升前的單周期耗時,同時保證系統時序更加穩定可靠,尤其在當前組合邏輯所涉及的路徑是一條關鍵路徑時,采用流水線設計后,整個系統的性能將得到極大提升。

例如,當一個流水線設計需要四個時鐘周期時,輸入數據in1從第一個時鐘周期1clk開始,直到第四個時鐘周期4clk才處理完,但是在前四個周期處理完成后,每個時鐘周期內都會有處理完成的數據輸出。由此可見,流水線設計僅在開始時需要一定的處理時間,之后將不間斷地輸出數據,從而極大提高處理速度。如果不采用流水線設計對四周期處理過程進行分割,那么每個輸入數據的處理都將需要四個時鐘周期,而在耗費更多時鐘周期的同時,系統的時鐘頻率也受到極大限制,甚至出現時序紊亂的情況。

流水線設計犧牲面積換取時鐘頻率,從而提高數據的傳輸速率,這種設計思想在高速通信、高速信號采集、圖像處理等領域得到廣泛應用。

05設計思想4:邏輯復制與模塊復用

邏輯復制通過犧牲面積改善時序條件,從而降低信號的路徑延時,常應用于信號扇出(fan out)的調整。如果某個信號的扇出很大,即需要驅動的后記邏輯信號較多,為增強這個信號的驅動能力,通常需要加入多級Buffer,這在一定程度上增加了信號的路徑演示。此時可以復制生成這個信號的邏輯,用多路同頻同相的信號驅動后續電路,降低平均到每路的扇出,從而在滿足驅動能力的同時,避免多級Buffer造成的路徑延時。

模塊復用通過犧牲速率換取更低的資源占用面積,是邏輯復制的逆過程,可以極大降低硬件資源消耗。

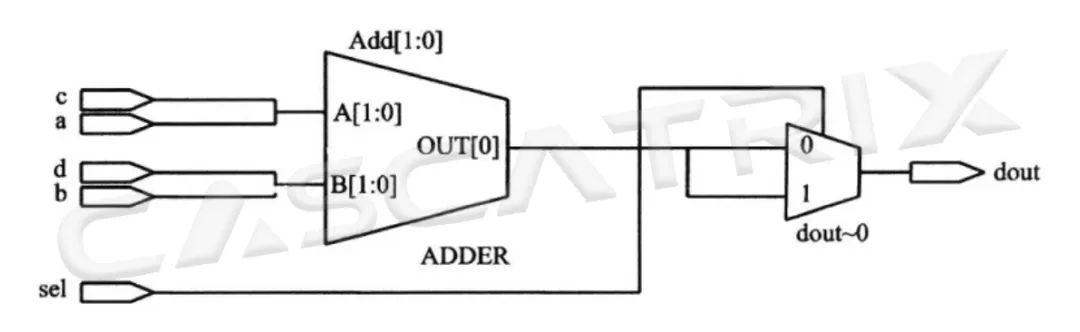

下面通過兩段代碼設計闡釋上述概念:

Ex1:

input a,b,c,d;

input sel;

output dout;

assign dout = sel ? (a+b) : (c+d);

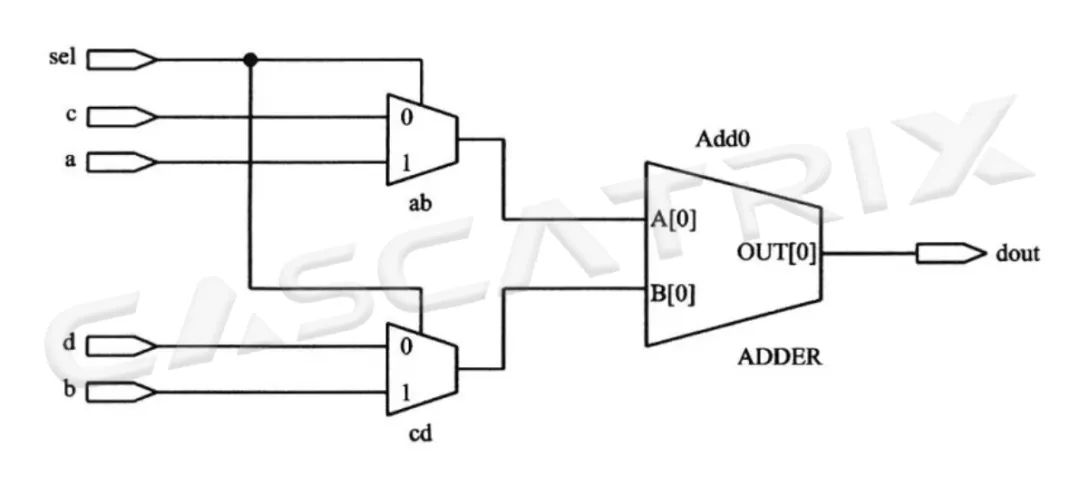

Ex2:

input a,b,c,d;

input sel;

output dout;

wire ac;

wire bd;

assign ac = sel ? a : c;

assign bd = sel ? b : d;

assign dout = ac + bd;

上述兩端代碼實現功能相同:Ex1綜合出的RTL視圖使用了兩個2選1數據選擇器和一個加法器;Ex2綜合出的RTL視圖使用了兩個加法器和一個2選1數據選擇器。Ex1占用更多的資源,但是處理速率更快;Ex2占用資源較少,但是處理速率較慢。

從一方面看,Ex1相對于Ex2是一種邏輯復制的過程,由于這個設計通過一個加法器就可以實現,但是為了提高處理速度,所以對加法器進行邏輯復制;從另一方面看,Ex2相對于Ex1是一種模塊復用的過程,通過復用加法器邏輯模塊,降低資源的消耗。

值得一提的是,當前很多綜合工具都可以自動設置最大扇出值。如果某個信號的扇出值大于最大扇出值,那么該信號將會自動被綜合工具復制。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602034 -

FPGA設計

+關注

關注

9文章

428瀏覽量

26489 -

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

流水線

+關注

關注

0文章

120瀏覽量

25629 -

RTL

+關注

關注

1文章

385瀏覽量

59710

原文標題:FPGA速度-面積互換原則設計

文章出處:【微信號:Carlinx FPGA,微信公眾號:Carlinx FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA速度-面積互換原則設計

FPGA速度-面積互換原則設計

評論