碳化硅 (SiC) 等寬帶隙器件可實現能夠保持高功率密度的晶體管,但需要使用低熱阻封裝,比如 TO-247。然而,此類封裝的連接往往會導致較高的電感。閱讀本博文,了解如何謹慎使用開爾文連接技術以解決電感問題。

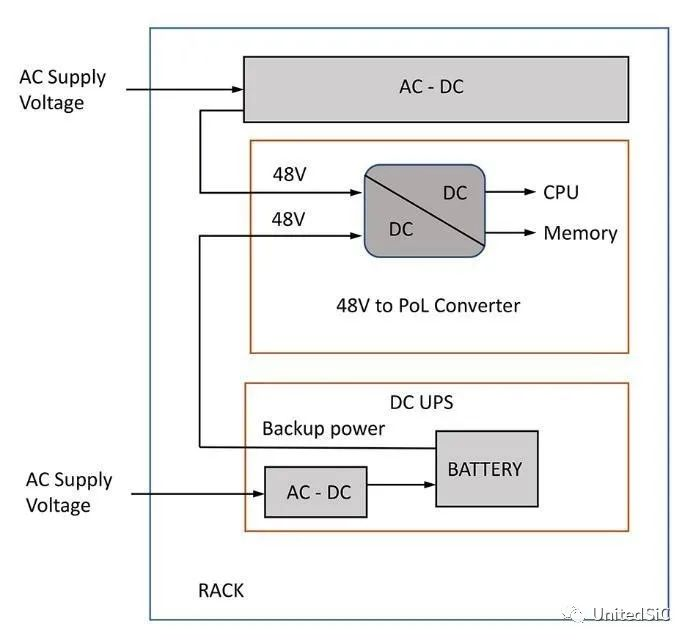

這篇博客文章最初由 United Silicon Carbide (UnitedSiC) 發布,該公司于 2021 年 11 月加入 Qorvo 大家庭。UnitedSiC 是一家領先的碳化硅 (SiC) 功率半導體制造商,它的加入促使 Qorvo 將業務擴展到電動汽車 (EV)、工業電源、電路保護、可再生能源和數據中心電源等快速增長的市場。

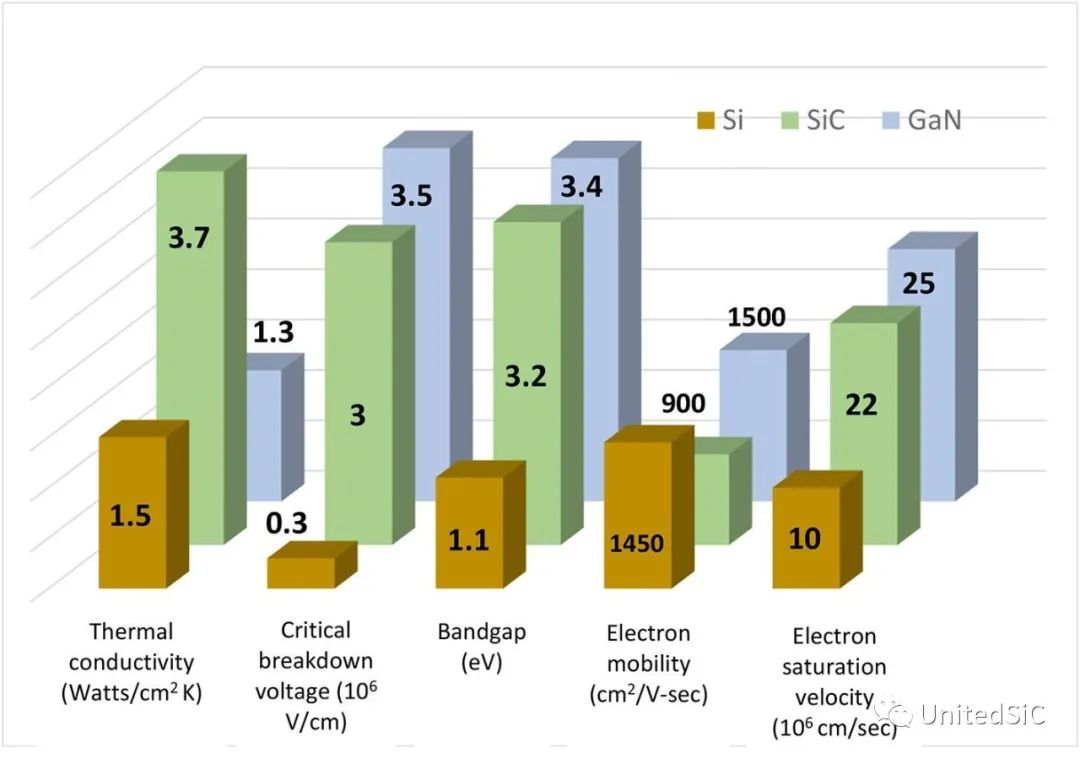

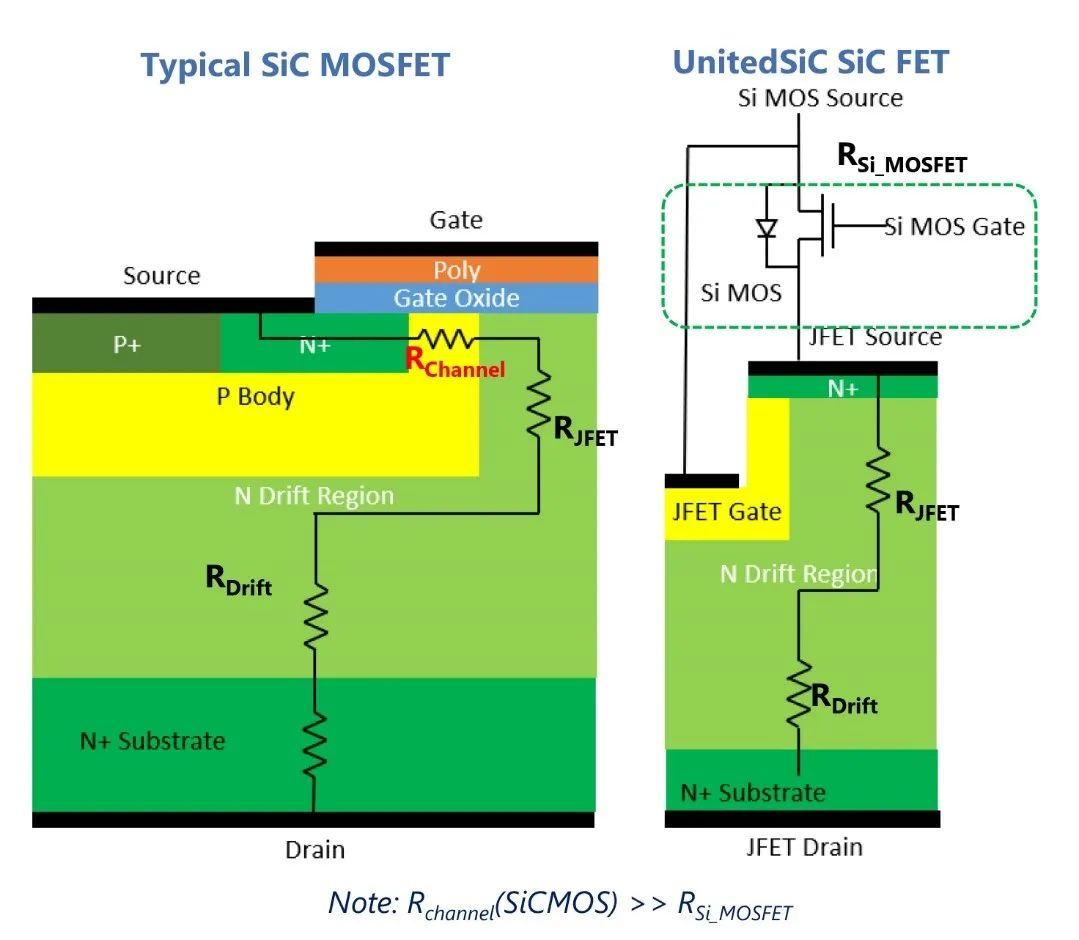

物理現象既會帶來優勢,也會產生弊端。采用碳化硅 (SiC) 等寬帶隙材料構建而成的器件,可為設計人員提供能夠保持高功率密度的晶體管,因為這些晶體管的傳導損耗和開關損耗較低,而且工作結溫高,開關速度快。高功率密度的晶體管對于實現更小的功率控制和轉換電路有非常大的幫助,但僅僅改變半導體材料是無法實現的,還需要使用低熱阻封裝,比如 TO-247,以便輕松散熱。不幸的是,這又是一個物理難題:TO-247 封裝的連接往往電感較高,這會限制開關速度。

物理現象有利有弊,而在這種情況下,使用開爾文連接技術可以解決電感問題。但是我們必須謹慎實現此類連接,以避免發生更糟糕的物理現象。

開爾文連接

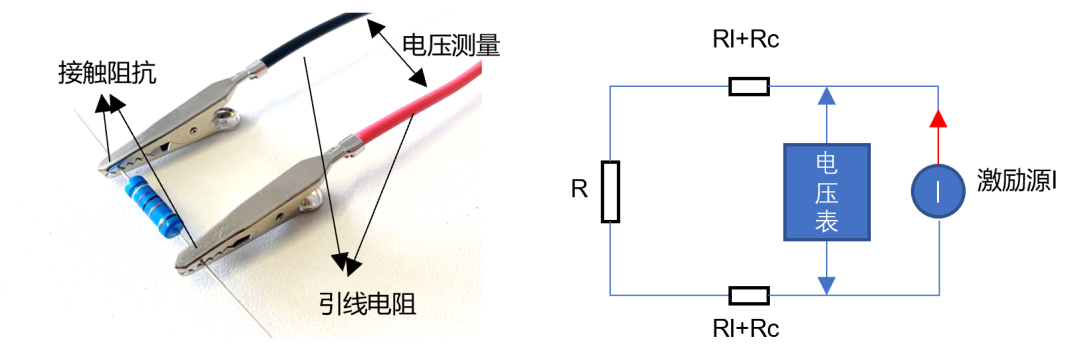

蘇格蘭/愛爾蘭實驗主義者開爾文男爵非常關注物理現象(如電流)的測量精度。他明白,要想通過檢測給定電流下低電阻導致的壓降,并結合使用歐姆定律來得出其阻值,就必須精確地測量電阻上的電壓,并且要將測量電壓的線路和載流路徑分開。這種方法被稱為開爾文連接。

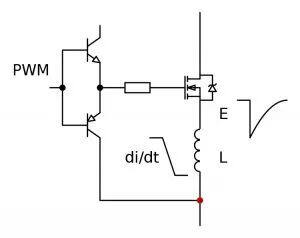

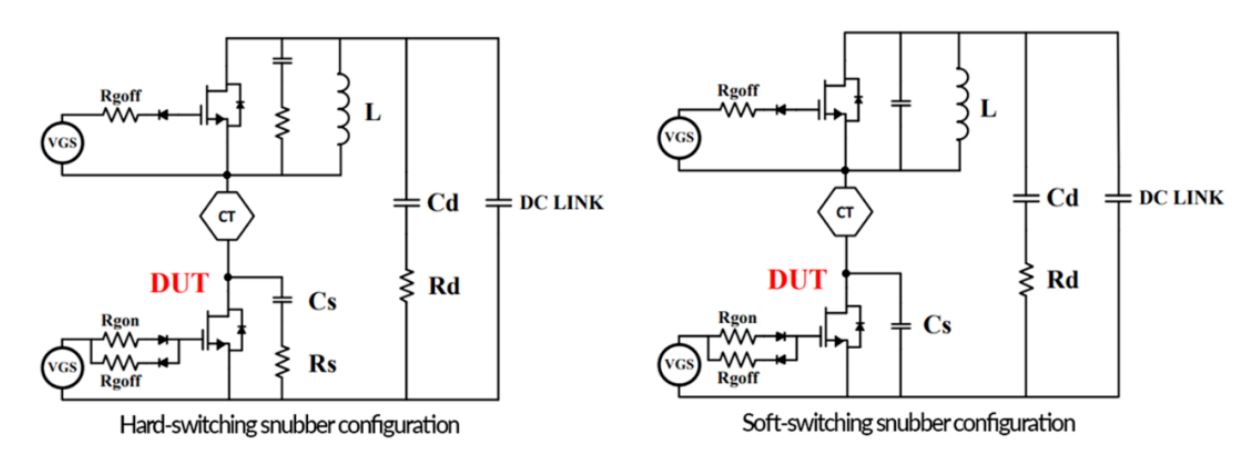

開爾文連接最初用于測量電路中適當位置的靜態電壓,但也可以用于在適當位置注入電壓。例如:當以高頻率驅動 MOSFET 開關的柵極時,器件的源連接就是柵極驅動電壓與漏極-源極電流的共用點。如果存在共源電感 L(如圖 1 中所示),則電流的變化就會影響柵極電壓,且影響程度與電感 L 和電流變化率成正比。在柵極被驅動關斷時,電感 L 兩端產生的電壓就會使柵極更長時間地保持接通狀態,從而降低電流減小的速度。相反,在接通期間,電感 L 上的電壓就會降低電流增加的速度。

控制引腳電感的影響

電感 L 來源于 MOSFET 的內部焊線,通常約為 1nH/mm。如果器件帶有引腳(比如 TO-247 封裝),則那些外部連接也會導致 L 增加。

圖 1:共源電感會產生瞬態柵極電壓,從而降低開關電流速度

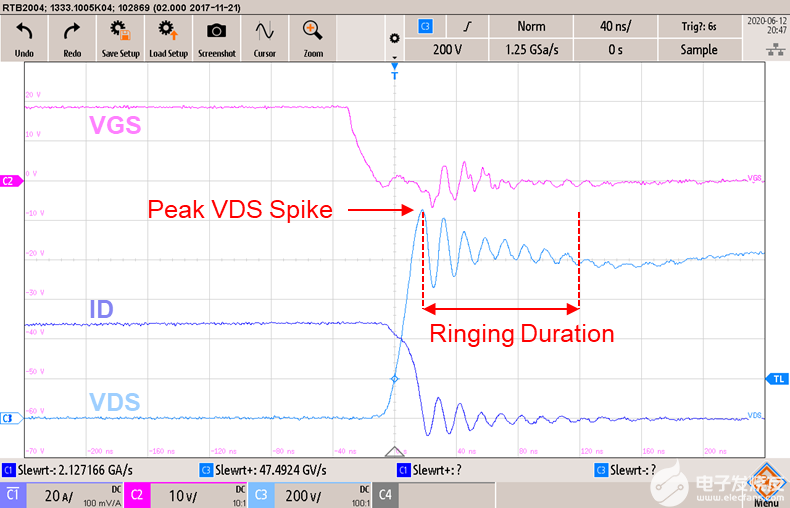

當以微秒為單位計算開關時間時,數安培的開關電流只會產生幾毫伏的瞬態電壓,從而使柵極驅動電壓幾乎保持不變。但是,寬帶隙 (WBG) 器件可在數納秒時間內產生數十安培的開關電流,這樣每 nH 連接電感就會產生大約 2-5V 瞬態電壓。如果柵極驅動中增加了這種瞬態電壓,就會阻止 MOSFET 關斷,從而產生振鈴風險,甚至會導致器件故障。

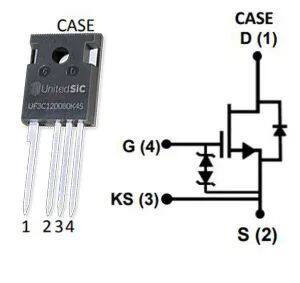

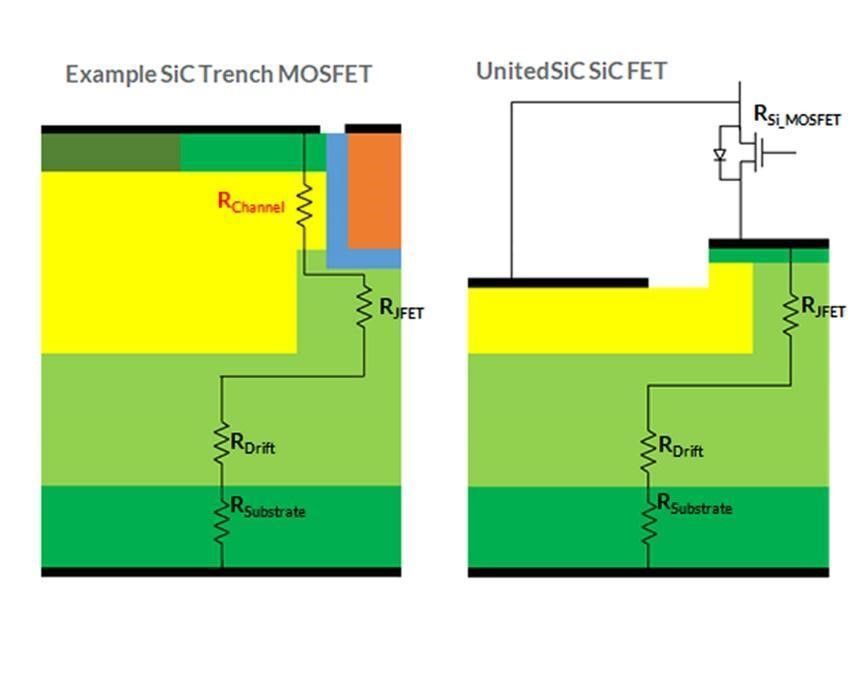

對于 Si MOSFET,可以在柵極關閉時施加加負電壓(或許為 -10V)以克服柵極電壓尖峰造成的偏壓降低。但這會導致更高的柵極驅動功耗,該功耗會隨總柵極驅動電壓波動一同變化。這一問題對于采用 SiC 或氮化鎵的 WBG 器件更為嚴重,因為此類器件只支持大約 -3V 的負驅動電壓。解決方案就是使用開爾文連接,以確保柵極驅動回路盡可能靠近 MOSFET 晶粒的源連接。盡管使用芯片級封裝比較容易實現這一點,但如果制造商想要使用 TO-247 封裝以獲得出色的散熱特性,則必須增加第 4 個引腳,以便進行開爾文連接(圖 2)。

圖 2:TO-247 封裝的第 4 個引腳可提供至源極的開爾文連接

開關速度越快,效率越高

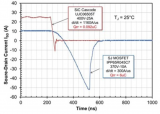

使用開爾文連接可控制引腳電感及其對柵極偏置電壓的潛在影響,讓寬帶隙器件以其真實的開關速度運行,無需使用柵極負電壓。這可以簡化驅動電路。效果非常明顯:當 UnitedSiC 的 SiC JFET 共源共柵使用三引腳封裝時,必須降低器件的速度才能保持其可靠性。而使用四引腳封裝以及開爾文連接時,電流壓擺率可超過5000 A/μs,從而實現更高效率,且不會影響柵極驅動信號。

物理現象并非盡如人意,即使是采用 TO-247 封裝,也有需要處理的器件引腳電感。常用的處理方式是跨漏極-源極放置一個小型緩沖電路,以防止功率路徑中出現電壓過沖。我們還必須小心部署柵極驅動回路,以盡可能地減少回路中的電感,同時防止出現由主換向回路導致的外部磁場拾取問題。

哪種開爾文連接?

使用開爾文連接時還會遇到其他實際問題。如果柵極驅動回路的電壓為主系統 0V 電壓,也就是與電源地線連接,則可能難以成為開爾文連接至開關的共用點。如果電路為全橋,那么至少會有兩個低側器件,如果都采用開爾文連接,則應將哪個連接至系統 0V?如果在器件源極引腳中使用電阻式電流感測,那么這個問題會變得更加復雜:如果開爾文連接的電壓為系統 0V 電壓,則電阻中的電壓將為負電壓。

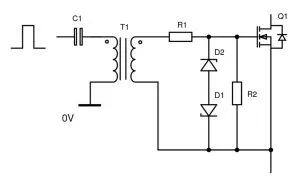

解決這個問題的一個方法就是,通過光耦合器或變壓器來隔離柵極驅動,這也是任何高側驅動都需使用的辦法。如果此類隔離用于低側,則可以靈活實現開爾文連接,與系統 0V 隔離(圖 3)。此外,使用變壓器意味著,設計人員可以根據需要生成關態柵極驅動負電壓,并且可以通過調整匝比將驅動正電壓調整至其最佳值。

圖 3:隔離的變壓器柵極驅動

優勢大于劣勢

使用開爾文接法連接帶引腳的寬帶隙器件還可使用 TO-247 封裝,從而具有出色的散熱性能。這使我們更接近于理想電氣開關,并且實際上還可在較高功率水平下使用。

-

開關

+關注

關注

19文章

3128瀏覽量

93512 -

FET

+關注

關注

3文章

630瀏覽量

62895 -

SiC

+關注

關注

29文章

2771瀏覽量

62468 -

碳化硅

+關注

關注

25文章

2702瀏覽量

48893

發布評論請先 登錄

相關推薦

采用SiC-FET的PSR反激參考設計

SiC FET性能和優勢及起源和發展介紹

SiC FET的起源和發展

SiC FET導通電阻隨溫度變化

最大限度降低SiC FET的EMI的開關損耗

使用開爾文連接提高 SiC FET 的開關效率

給SiC FET設計PCB有哪些注意事項?

使用開爾文連接提高SiC FET的開關效率

使用開爾文連接提高SiC FET的開關效率

評論