ESD,EOS,Latch-up都是芯片在制造,運輸,使用過程中的風險源,他們會對芯片造成不同程度的物理損傷。所以芯片在設計過程中不得不考慮這些因素。前幾篇文章都聚焦于ESD防護,這一期討論芯片Latch-up防護。

一.Latch-up定義

閂鎖效應是指體CMOS集成電路中所固有的寄生NPN和寄生PNP組成的電路在一定條件下被觸發而形成低阻通路,從而產生大電流,并且由于正反饋電路的存在而形成閂鎖,導致CMOS集成電路無法正常工作,甚至燒毀芯片。——《CMOS集成電路閂鎖效應》。在日常工作中,作者對閂鎖現象分為兩種,一種是IO端口電路發生閂鎖(尤其是輸出buffer),一種就是ESD器件Design Window設計不當發生的閂鎖。

而Latch-up與ESD最大的區別在于, 閂鎖主要發生在芯片正常使用過程中。 Latch-up測試時,VDD上電,VSS接GND,非測試引腳按要求接高低電位,對VDD/輸出輸入接測試電流/電壓。而ESD主要發生在制造、運輸過程中,使用過程。ESD測試時一個引腳接電流源,一個引腳接地,芯片不上電。

1.1 CMOS電路閂鎖

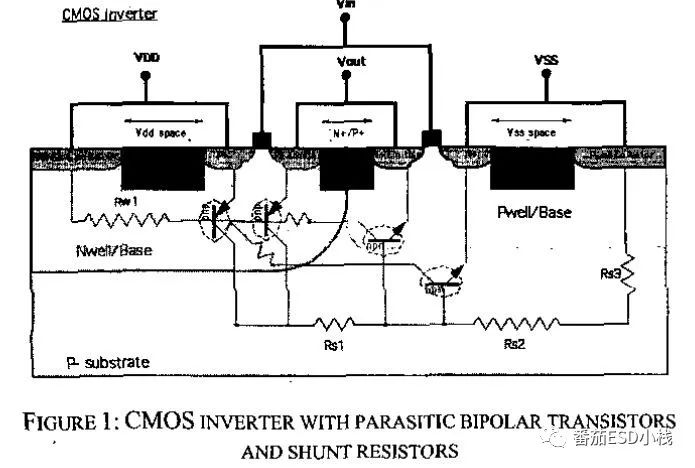

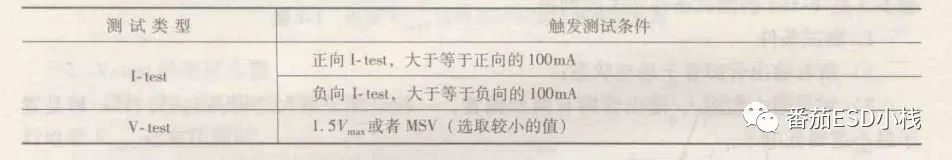

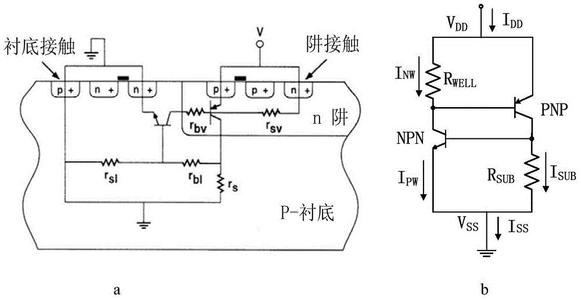

圖一.CMOS寄生SCR結構圖。

如圖所示,CMOS器件里存在多個寄生SCR器件。VDD與GND之間;VDD/輸出端口與GND;VDD/輸出端口與輸出端口;VDD與GND/輸出端口。前幾期已經介紹過SCR的工作原理,這里不再贅述。

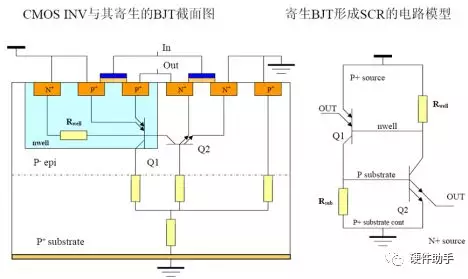

圖二.CMOS寄生SCR電路圖。

- VDD出現浪涌,N-WeLL/P-WeLL發生雪崩擊穿。 大量雪崩載流子經過阱電阻Rnw,Rpw產生壓降,寄生SCR開啟。寄生NPN與寄生PNP發生正反饋耦合,從而形成低阻通路,發生Latch-up。

2 .輸出端電壓過沖,寄生SCR中PNP三極管的射電極(輸出端)電壓高于VDD, 該PNP導通,Rpw產生壓降,造成寄生NPN開啟,NPN與PNP發生正反饋耦合,從而形成低阻通路,發生Latch-up。

- 輸出端電流倒灌,大量電流由NMOS和PMOS的Drain端流入電路中。電流流經阱電阻Rnw和Rpw, 產生壓降作用于寄生NPN和PNP的基級,造成寄生NPN和PNP的開啟,NPN與PNP發生正反饋耦合,從而形成低阻通路,發生Latch-up。

- 輸出端電壓下沖,寄生SCR中NPN三極管的射電極(輸出端)電壓低于GND ,該NPN導通,Rnw產生壓降,造成寄生PNP開啟,NPN與PNP發生正反饋耦合,從而形成低阻通路,發生Latch-up。

1.2 ESD保護器件閂鎖

ESD器件發生閂鎖的情況有兩種 一種是ESD器件內部寄生SCR的開啟,還有一種是Design Window選取不合理。

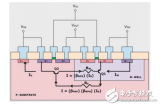

圖三.二極管ESD防護示意圖。

如圖三所示,使用GCNMOS作為Power Clamp時,端口的ESD防護會使用二極管,P-diode連接端口與VDD,N-diode連接GND與端口。N-diode與P-diode之間會存在寄生SCR器件,如圖四所示。(GCNMOS前幾期已經講過,二級管的ESD防護后期也會提及)

圖四.二極管寄生SCR示意圖。(圖源《CMOS集成電路閂鎖效應》)

與上文中的CMOS中寄生SCR類似,P-diode與N-diode間也會存在寄生SCR器件且發生Latch-up的情況:

- VDD出現浪涌,N-WeLL/P-WeLL發生雪崩擊穿。 寄生SCR開啟,發生Latch-up。

- 端口電壓過沖,寄生SCR中PNP三極管的射電極(P-diode陽極)電壓高于VDD, 該PNP導通,Rpw產生壓降,造成寄生NPN開啟,發生Latch-up。

- 端口大電流,大量電流進入N-WeLL/P-WeLL, 經過阱電阻產生壓降,發生Latch-up。

- 端口電壓下沖,寄生SCR中NPN三極管的射電極(N-diode陰極)電壓低于GND ,該NPN導通,Rnw產生壓降,造成寄生PNP開啟,發生Latch-up。

第二種情況就是ESD器件的Design Window設置不合理。 如果ESD器件的IV曲線進入電路的latch-up區,當ESD器件被誤觸發開啟后,ESD器件會一直保持開啟,直至損壞。

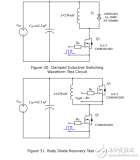

圖五.用于不同電路中的ESD器件以及設計窗口。a)電源鉗位電路與設計窗口b)CMOS輸出級與設計窗口。c)柵極輸入與設計窗口。

如圖五所示,不同的防護需求的ESD器件有對應的設計窗口要求。

a)作用于VDD與GND之間的Power Clamp,其Holding Voltage不能小于VDD。VDD的驅動能力近似是無窮大的,如果ESD器件的Holding Voltage進入latch up區,使用過程中一旦VDD的擾動開啟ESD器件,ESD器件的低阻通路會一直開啟,直到燒毀。

b)作用于輸出級的ESD防護器件,其Design Window中的Latch-up區為由PMOS的負載曲線,因為PMOS進入飽和區后存在溝道夾斷效應,其過電流能力有限,所以Latch-up區的電流上限有限。ESD器件的Holding Voltage和Holding Current一旦進入PMOS的Latch-up區,PMOS會形成對ESD器件的持續上拉,帶來失效風險。

c)作用于輸入級的ESD防護器件,其Design Window中的Latch-up區為柵級負載曲線,大部分ESD器件都能避免Latch-up風險。

如果是ESD器件是作用于端口與VDD之間,其柵極輸入的Design Window與端口對地一致,而輸出級的Design Window需要關注NMOS的負載曲線,避免進入NMOS的下拉負載區內,形成導電通路。

-

CMOS

+關注

關注

58文章

5680瀏覽量

235145 -

ESD

+關注

關注

48文章

2012瀏覽量

172733 -

SCR

+關注

關注

2文章

150瀏覽量

44143 -

GND

+關注

關注

2文章

529瀏覽量

38657 -

PNP管

+關注

關注

1文章

28瀏覽量

7418

發布評論請先 登錄

相關推薦

CMOS的閂鎖效應:Latch up的原理分析

Latch UP

寄生電路的效應:Latch-Up(鎖定)

靜電放電/過度電性應力/閂鎖試驗 (ESD/EOS/Latch-up)

LIS3DH加速度計自我測試失敗

ESD/Latch-Up Considerations wi

Latch-Up White Paper

Latch-Up白皮書

c2m0160120d碳化硅功率MOSFET技術

高壓閉鎖雙SPST開關的adg5421/adg5423數據表

淺談Latch-up(二)

淺談Latch-up(一)

淺談Latch-up(一)

評論