分享一篇不錯的PCB與EMI問題文章,來自網(wǎng)絡(luò)。

電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來都需要系統(tǒng)設(shè)計工程師擦亮眼睛,在當今電路板設(shè)計和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下,這兩大問題尤其令PCB布局和設(shè)計工程師頭痛。

EMC與電磁能的產(chǎn)生、傳播和接收密切相關(guān),PCB設(shè)計中不希望出現(xiàn)EMC。電磁能來自多個源頭,它們混合在一起,因此必須特別小心,確保不同的電路、走線、過孔和PCB材料協(xié)同工作時,各種信號兼容且不會相互干擾。

另一方面,EMI是由EMC或不想要的電磁能產(chǎn)生的一種破壞性影響。在這種電磁環(huán)境下,PCB設(shè)計人員必須確保減少電磁能的產(chǎn)生,使干擾最小。

避免在PCB設(shè)計中出現(xiàn)電磁問題的7個技巧

技巧1:將PCB接地

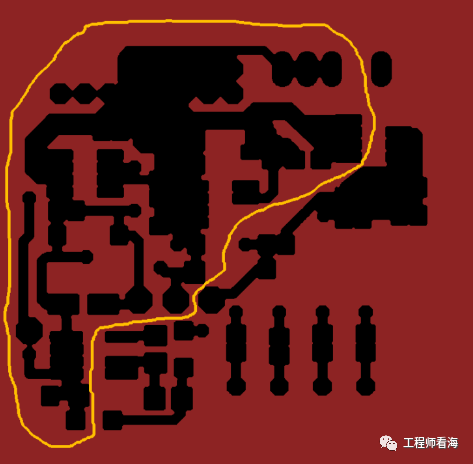

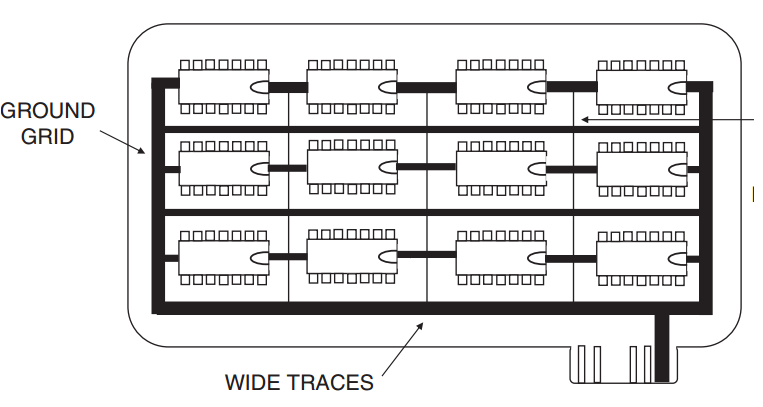

降低EMI的一個重要途徑是設(shè)計PCB接地層。第一步是使PCB電路板總面積內(nèi)的接地面積盡可能大,這樣可以減少發(fā)射、串擾和噪聲。將每個元器件連接到接地點或接地層時必須特別小心,如果不這樣做,就不能充分利用可靠的接地層的中和效果。

一個特別復(fù)雜的PCB設(shè)計有幾個穩(wěn)定的電壓。理想情況下,每個參考電壓都有自己對應(yīng)的接地層。但是,如果接地層太多會增加PCB的制造成本,使價格過高。折衷的辦法是在三到五個不同的位置分別使用接地層,每一個接地層可包含多個接地部分。這樣不僅控制了電路板的制造成本,同時也降低了EMI和EMC。

如果想使EMC最小,低阻抗接地系統(tǒng)十分重要。在多層PCB中,最好有一個可靠的接地層,而不是一個銅平衡塊(copper thieving)或散亂的接地層,因為它具有低阻抗,可提供電流通路,是最佳的反向信號源。

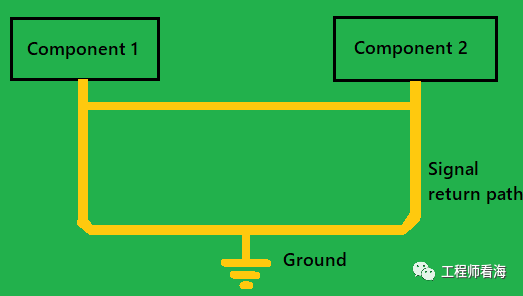

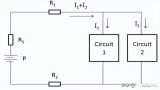

信號返回地面的時長也非常重要。信號往返于信號源的時間必須相當,否則會產(chǎn)生類似天線的現(xiàn)象,使輻射的能量成為EMI的一部分。同樣,向/從信號源傳輸電流的走線應(yīng)盡可能短,如果源路徑和返回路徑的長度不相等,則會產(chǎn)生接地反彈,這也會產(chǎn)生EMI。

如果信號進出信號源的時間不同步,則會產(chǎn)生類似天線的現(xiàn)象,從而輻射能量,引起EMI

技巧2:區(qū)分EMI

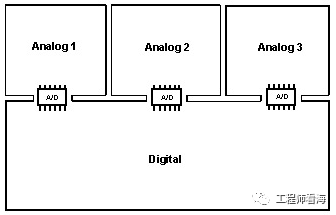

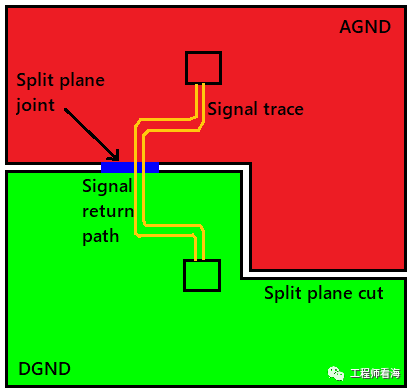

由于EMI不同,一個很好的EMC設(shè)計規(guī)則是將模擬電路和數(shù)字電路分開。模擬電路的安培數(shù)較高或者說電流較大,應(yīng)遠離高速走線或開關(guān)信號。如果可能的話,應(yīng)使用接地信號保護它們。在多層PCB上,模擬走線的布線應(yīng)在一個接地層上,而開關(guān)走線或高速走線應(yīng)在另一個接地層。因此,不同特性的信號就分開了。

有時可以用一個低通濾波器來消除與周圍走線耦合的高頻噪聲。濾波器可以抑制噪聲,返回穩(wěn)定的電流。將模擬信號和數(shù)字信號的接地層分開很重要。由于模擬電路和數(shù)字電路有各自獨特的特性,將它們分開至關(guān)重要。數(shù)字信號應(yīng)該有數(shù)字接地,模擬信號應(yīng)該終止于模擬接地。

在數(shù)字電路設(shè)計中,有經(jīng)驗的PCB布局和設(shè)計工程師會特別注意高速信號和時鐘。在高速情況下,信號和時鐘應(yīng)盡可能短并鄰近接地層,因為如前所述,接地層可使串擾、噪聲和輻射保持在可控制的范圍。

數(shù)字信號也應(yīng)遠離電源平面。如果距離很近,就會產(chǎn)生噪聲或感應(yīng),從而削弱信號。

技巧3:串擾和走線是重點

走線對確保電流的正常流動特別重要。如果電流來自振蕩器或其它類似設(shè)備,那么讓電流與接地層分開,或者不讓電流與另一條走線并行,尤其重要。兩個并行的高速信號會產(chǎn)生EMC和EMI,特別是串擾。必須使電阻路徑最短,返回電流路徑也盡可能短。返回路徑走線的長度應(yīng)與發(fā)送走線的長度相同。

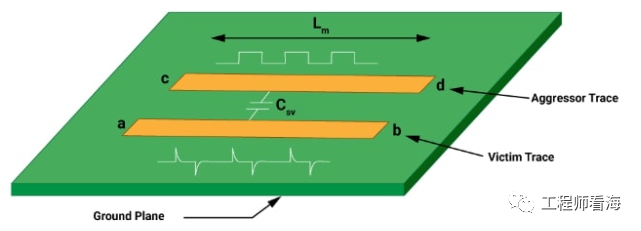

對于EMI,一條叫做“侵犯走線”,另一條則是“受害走線”。電感和電容耦合會因為電磁場的存在而影響“受害”走線,從而在“受害走線”上產(chǎn)生正向和反向電流。這樣的話,在信號的發(fā)送長度和接收長度幾乎相等的穩(wěn)定環(huán)境中就會產(chǎn)生紋波。

在一個平衡良好、走線穩(wěn)定的環(huán)境中,感應(yīng)電流應(yīng)相互抵消,從而消除串擾。但是,我們身處不完美的世界,這樣的事不會發(fā)生。因此,我們的目標是必須將所有走線的串擾保持在最小水平。如果使并行走線之間的寬度為走線寬度的兩倍,則串擾的影響可降至最低。例如,如果走線寬度為5密耳,則兩條并行走線之間的最小距離應(yīng)為10密耳或更大。

隨著新材料和新的元器件不斷出現(xiàn),PCB設(shè)計人員還必須繼續(xù)應(yīng)對電磁兼容性和干擾問題。

技巧4:去耦電容

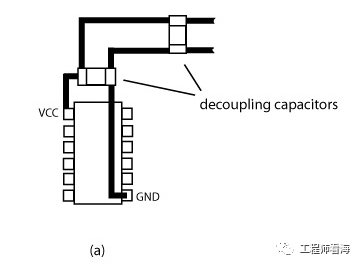

去耦電容可減少串擾的不良影響,它們應(yīng)位于設(shè)備的電源引腳和接地引腳之間,這樣可以確保交流阻抗較低,減少噪聲和串擾。為了在寬頻率范圍內(nèi)實現(xiàn)低阻抗,應(yīng)使用多個去耦電容。

放置去耦電容的一個重要原則是,電容值最小的電容器要盡可能靠近設(shè)備,以減少對走線產(chǎn)生電感影響。這一特定的電容器盡可能靠近設(shè)備的電源引腳或電源走線,并將電容器的焊盤直接連到過孔或接地層。如果走線較長,請使用多個過孔,使接地阻抗最小。

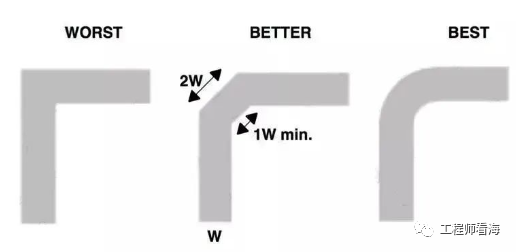

技巧5:避免90°角

為降低EMI,應(yīng)避免走線、過孔及其它元器件形成90°角,因為直角會產(chǎn)生輻射。在該角處電容會增加,特性阻抗也會發(fā)生變化,導(dǎo)致反射,繼而引起EMI。要避免90°角,走線應(yīng)至少以兩個45°角布線到拐角處。

技巧6:使用過孔需謹慎

在幾乎所有PCB布局中,都必須使用過孔在不同層之間提供導(dǎo)電連接。PCB布局工程師需特別小心,因為過孔會產(chǎn)生電感和電容。在某些情況下,它們還會產(chǎn)生反射,因為在走線中制作過孔時,特性阻抗會發(fā)生變化。

同樣要記住的是,過孔會增加走線長度,需要進行匹配。如果是差分走線,應(yīng)盡可能避免過孔。如果不能避免,則應(yīng)在兩條走線中都使用過孔,以補償信號和返回路徑中的延遲。

技巧7:電纜和物理屏蔽

承載數(shù)字電路和模擬電流的電纜會產(chǎn)生寄生電容和電感,引起很多EMC相關(guān)問題。如果使用雙絞線電纜,則會保持較低的耦合水平,消除產(chǎn)生的磁場。對于高頻信號,必須使用屏蔽電纜,其正面和背面均接地,消除EMI干擾。

物理屏蔽是用金屬封裝包住整個或部分系統(tǒng),防止EMI進入PCB電路。這種屏蔽就像是封閉的接地導(dǎo)電容器,可減小天線環(huán)路尺寸并吸收EMI。

如果看到這里,請點贊、收藏、分享三連!

限時免費掃碼進群,交流更多行業(yè)技術(shù)

推薦閱讀▼

審核編輯黃宇

-

PCB設(shè)計

+關(guān)注

關(guān)注

394文章

4648瀏覽量

84516 -

emc

+關(guān)注

關(guān)注

167文章

3795瀏覽量

182264

發(fā)布評論請先 登錄

相關(guān)推薦

PCB設(shè)計中EMC/EMI的仿真

EMC之PCB設(shè)計技巧

PCB設(shè)計考慮EMC的接地技巧

PCB設(shè)計中的EMC概念

PCB設(shè)計中EMC/EMI的仿真

關(guān)于PCB設(shè)計過程中的EMC/EMI仿真淺析

PCB設(shè)計EMC/EMI的仿真分析

EMC的PCB設(shè)計解析

PCB設(shè)計中7個EMC技巧!

PCB設(shè)計中7個EMC技巧!

評論