本文選自極術專欄《IC設計》的文章,授權轉自微信公眾號老秦談芯。本篇將介紹多核處理器的啟動過程。

在早些年前,一個中央處理器(CPU)里面只有一個處理器核(Core)。那時候CPU的性能提升主要靠的是提升處理器工作主頻。定性分析,我們假定一個軟件在編譯完成后,對應的需要執行的指令總數是固定的,那么處理器主頻越高,執行這些指令用的時間越少,也就是處理器的性能越高。定量分析,處理器的性能公式:CPU時間 = IC x CPI x時鐘周期時間,其中IC是指令的條數,CPI是每時鐘周期指令數。從上述公式可以看出提升CPU性能可以從三方面入手:時鐘頻率,CPI 和指令的條數。

隨著集成電路的發展,人們發現提高處理器主頻越來越難以實現了。那么,能不能把原來的一個任務分解成多個子任務并行執行,這樣是不是就會提升處理器的性能呢?在前面我們講過,雖然現在的處理器有了操作系統加持,看起來能夠并行執行很多個不同的程序。但是實際上在某一段時間內,一個處理器核只能執行一個程序,操作系統只是通過時間片輪轉的方式讓所有的程序分時執行,看起來像所有程序并行執行一樣。那如果有很多個處理器核,每個核執行一個程序,是不是會提升整體性能呢?這兩個問題的答案都是肯定的。有了多核處理器,就可以并行執行多個程序,也可以并行執行一個程序(前提是這個程序可拆解)。對于并行執行的性能提升,定量分析可以參考Amdahl定律。

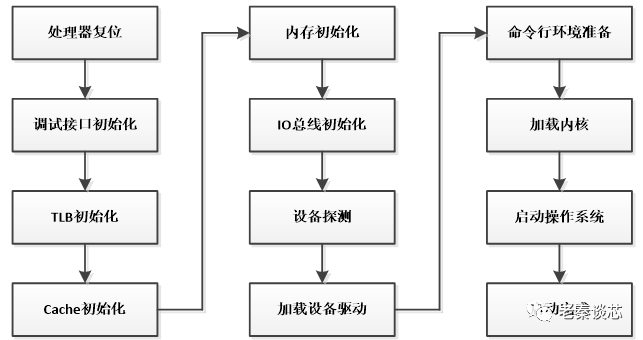

不管單核處理器還是多核處理器設計,都是一個非常宏大的話題。以上只是泛泛而談,不再展開。我們今天具體看看處理器的啟動過程。在分析多核處理器啟動之前,我們先來看看一個單核的計算機系統是如何啟動的。假設大家對內存管理,TLB,緩存(Cache),DDR,PCIe這些有一些基礎知識。

當我們按下電源開關以后,系統的時鐘生成單元會最先工作,這時候處在參考時鐘ref_clk下(通常是10-100MHz),待到PLL輸出穩定后,時鐘生成單元會把給處理器的時鐘切換到正常工作頻率,并釋放處理器的復位信號,通常我們稱這個復位為冷復位。

無論采用何種指令系統的處理器, 復位后的第一條指令都會從一個預先定義的特定地址取回。處理器的執行就從這條指令開始。處理器的啟動過程, 實際上就是一個特定程序的執行過程。這個程序我們稱為BIOS(Basic Input Output System, 基本輸入輸出系統),也有稱為Bootloader,或者統統歸為固件(Firmware)。現代計算機系統的啟動代碼很復雜了,但是本文是從硬件角度去分析,所以就不嚴格區分這幾個軟件概念了。

處理器預先定義的起始地址會在系統總線中映射到一個存儲設備上,這個設備可能是內部的ROM,也可能是外部Flash。如果把處理器從開始到結束比作一場大戲,啟動過程就是序幕,那么現在才剛剛開始準備工作。

當CPU拿到第一條指令,啟動過程就開始了。所謂啟動初始化過程,就是把計算機系統內部每個模塊的工作狀態調整到一個確定的狀態,其實就是一個熵減的過程。現在的處理器設計大都是基于Load/Store架構,所以簡單說,初始化過程就是處理器通過一大堆的load和store指令把復位后某些沒有固定態的寄存器或者模塊設置到固定態(嚴格意義上,這么說不十分準確)。

處理器啟動后的第一條指令的地址一定是實地址,或者說是直接地址翻譯模式(虛地址和實地址有直接的對應關系)下的地址,因為這時候的TLB還沒有被初始化,尚不能正常工作。這時候的指令或數據訪問是uncacheable的,也就是不經過高速緩存,原因一樣,高速緩存還沒有被初始化。

在初始化過程的前期,一般最先初始化調試接口,通常是UART串口。這樣做的好處是在早期就可以提供一個簡單的交互接口,如果后面的初始化過程跑不下去了,也能進行簡單的調試。通常情況下,I/O設備的寄存器會跟內存空間映射到一起,也就是所謂的memory mapped方式,這樣處理器可以像訪問內存空間一樣去訪問這些I/O設備(我們先不考慮某些系統中可以通過特殊指令訪問I/O設備的做法)。

調試接口的初始化完成后,就是TLB初始化。TLB作為一個地址映射的管理模塊,主要負責操作系統里地址空間的管理。系統剛上電時,TLB里的內容是殘留或者隨機的,換句話說,TLB里面的所有表項都是錯誤的。TLB的初始化主要是將全部表項初始化為無效,將TLB的每項逐一清空, 以免程序中使用的地址被未初始化的TLB表項所錯誤映射。這個過程可以由硬件完成,也可以由軟件完成(通過特殊指令),不同指令集的處理器有不同的方式。

同理,在系統復位之后,Cache同樣也處于一個未經初始化的狀態, 也就是說Cache里面可能包含殘留的或隨機的數據, 如果不經初始化, 對于Cache空間的訪問也可能會導致錯誤的命中。大多數情況下對Cache的初始化就是對Tag的初始化,只要將其中的Cache塊狀態設置為無效, 其它部分的隨機數據就不會產生影響。現在的處理器設計中,緩存系統大多數情況下會采用分層結構,對于多核處理器,一般L1緩存是獨享的,最后一級緩存是共享的。不管單核處理器系統還是多核處理器系統,都要對所有層級的緩存做初始化。

接下來就是內存的初始化了,在此步驟之前的代碼執行要么是處理器直接讀ROM/Flash里面的指令,要么是把外部存儲器的讀到芯片內部RAM,處理器從RAM讀取指令。不管哪種方式,處理器執行的速度都會比較慢。內存控制器的初始化包括兩個相對獨立的部分, 一是根據內存的行地址、列地址等對內存地址映射進行配置, 二是根據協議對內存信號調整的支持方式對內存讀寫信號相關的寄存器進行訓練(Training), 以保證傳輸時的數據完整性。 內存初始化完成后,就要對外部設備進行初始化,首先要完成的是外部設備的探測和加載。這部分主要是指PCIe的訓練,設備枚舉,并加載驅動等動作。這也是一個比較大的話題,不展開了。

至此,為了加載操作系統的基本環境已完成,可以進入操作系統內核了。單核處理器的啟動初始化過程也就結束了。

對于多核處理器系統,情況復雜一些。一般是有一個主核(有時叫core 0)先去完成上述的操作。主核的啟動工作完成后,再去喚醒其它的處理器核(可以稱為從核)。從核負責初始化私有的TLB和cache等資源,啟動之后進入空閑(Idle)狀態,直至進入操作系統再由主核進行調度。多核處理器的內核間通信一般會通過信箱(Mailbox)機制或者核間中斷機制。信箱機制可以是設計專用的信箱寄存器,主要是為了在內存還沒有初始化前就讓所有處理器核能夠有效通。如果是通過信箱機制,從核在等待喚醒的時候要去定時查詢自己的信箱寄存器,如果發現主核喚醒自己,就要從空閑狀態出來了。可以看出,信箱寄存器機制需要處理器輪詢,所以通信效率不高,在休眠/喚醒這類不頻繁的操作中還可以,如果是比較頻繁的核間通信就不適用了,要采取中斷機制。

以上是多核處理器啟動的基本原理,至于具體實現,不同的廠商有不同的設計。比如在ARM體系里面,往往會有一個小的系統控制單元(MSCP,Management & System Control Processor)輔助完成簡單外設初始化,安全認證等等工作,然后由主核和從核完成剩余的啟動工作。

責任編輯:彭菁

-

電源開關

+關注

關注

12文章

1031瀏覽量

44486 -

程序

+關注

關注

116文章

3775瀏覽量

80845 -

多核處理器

+關注

關注

0文章

109瀏覽量

19897

原文標題:多核處理器啟動過程淺析

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

嵌入式微處理器和接口詳技術詳解

嵌入式微處理器和接口詳技術詳解

多核處理器的優點

典型的支持多核處理器的RTOS功能解析

STM 32 UART串口通信基本原理是什么?

多核處理器啟動的基本原理是什么?如何實現呢

看看一個多核處理器系統是如何啟動的

多核處理器會取代FPGA嗎?

多核處理器啟動的基本原理

多核處理器啟動的基本原理

評論