一、什么是去耦以及為什么要去耦?

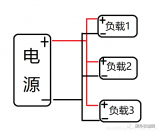

模電書上講的去耦大多是講電源的去耦,就是一個電路的各個單元共用同一電源供電,為了防止各單元之間的耦合,需加去耦電路。

造成耦合的原因有:

1. 數字電路——在電平翻轉時的瞬間會有較大的電流,且會在供電線路上產生自感電壓。

2. 功率放大電路——因電流較大,此電流流過電源的內阻和公共地和電源線路時產生電壓,使得電源電壓有波動。

3. 高頻電路——電路中有高頻部分因輻射和耦合在電源上產生干擾。

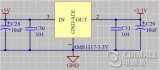

這些干擾會對同一供電電路中的對電源電壓較敏感或精度要求較高的部分. 比如微弱小信號放大器、AD轉換器等產生干擾,或者相互干擾,嚴重時使整個電路無法工作。為了阻止這種干擾,可以加電源去耦電路來解決,一般常用的電源去耦電路有RC或LC電路,要求較高的另加用穩壓電路。

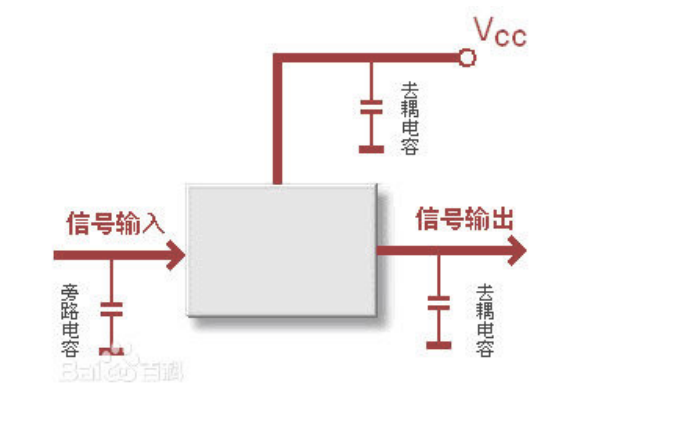

一般需要在以下位置放置去耦電容:

接插件的電源和信號引腳﹔

運放/比較器的電源引腳﹔

ADC和DAC的電源引腳;電路板上其他有可能發生電流波動的位置。

二、為什么電容可以去耦?

1)電源噪聲一般是高頻交流分量,而電容具有通交隔直的功能,所以電容以去除高頻噪聲分量,實現去耦。

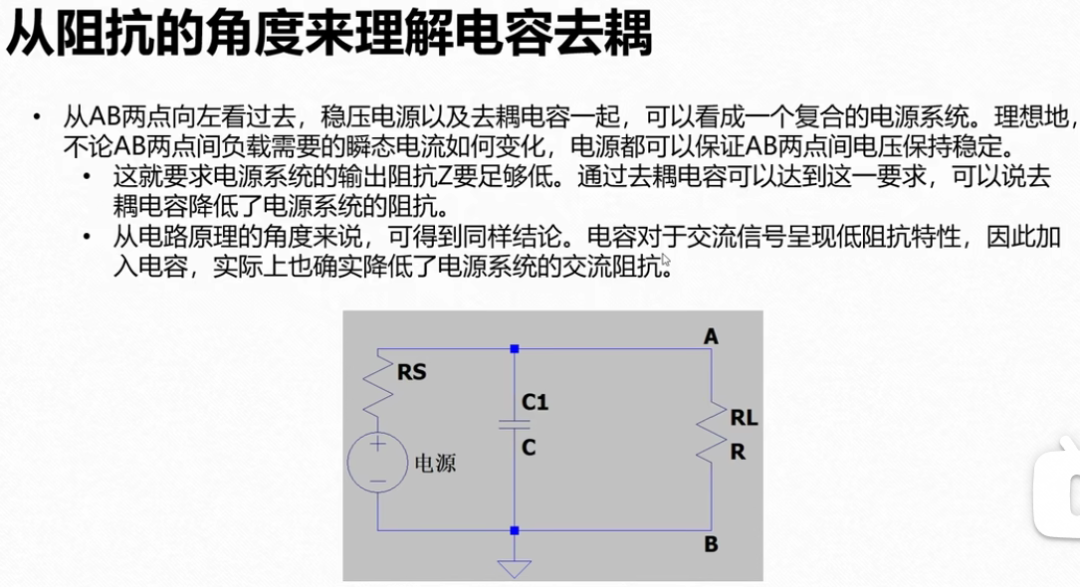

2)通過降低電源系統輸出阻抗,可以減少后級的負載變化對于電源輸出電壓的影響,而電容可以實現降低輸出阻抗的要求。(因為輸出電阻越小,可以減小負載瞬時電流突然變大導致的輸出電壓跌落(也就是電壓波動))。

(另一種降低輸出阻抗的去耦方式是縮短電源層和地層的距離)。

三、理想電容和實際電容的特性

雖然我們都知道電容具有通交隔直的功能。但是在實際使用過程中,我們還需要了解實際電容的特性,這樣才能選擇根據去耦電路的實際需求去選擇最合適的電容。

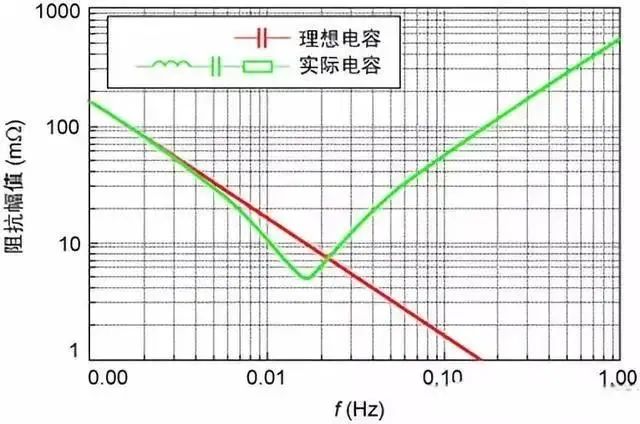

1)理想電容VS實際電容:

理想的電容:本身不會產生任何能量損耗,在任意頻率下都呈現容性。

實際電容:實際上,因為制造電容的材料有電阻,電容的絕緣介質有損耗,各種原因導致電容變得不“完美”。實際上的電容等于等效串聯電感ESL、等效串聯電阻ESR、與理想電容的串聯,因此其特性與頻率有關。

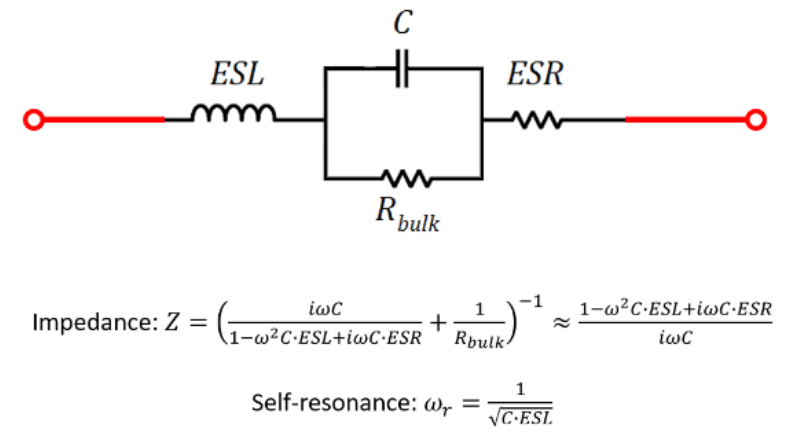

2)實際電容的模型:

實際的電容會存在一些能量損耗,在外部的表現就像一個電阻跟電容串聯在一起(等效串聯電阻ESR)。另一方面,由于引線、卷繞等物理結構因素,電容內部還存在著電感成分(等效串聯電感ESL)。電容器中存在一些泄漏或體電阻(體電阻Rbulk),它與理想電容、ESL 和 ESR 并聯存在。下圖顯示真正實際的電容模型和阻抗。

由于電容器中的介電材料具有很強的絕緣性,因此 Rbulk 的值通常非常大(~100 GOhms),因此在計算電容器的阻抗時可以忽略它。因此,我們在選擇電容時需要重點關注ESL和ESR值。

3)ESR和ESL對于電容濾波作用的影響:

ESR:——會導致電壓突變!

ESR通常是在100mΩ ~ 1000mΩ不等,假如你的芯片電源會有一個非常短暫的100mA的peak current, 而且這個電流幾乎是去耦電容來提供的, 如果你的電容ESR有1Ω,想象一下100mA的電流流過這個電阻, 到達另一端的時候, 已然有了100mV的壓降了.

ESL——會影響濾波的工作頻率和高頻濾波效果。

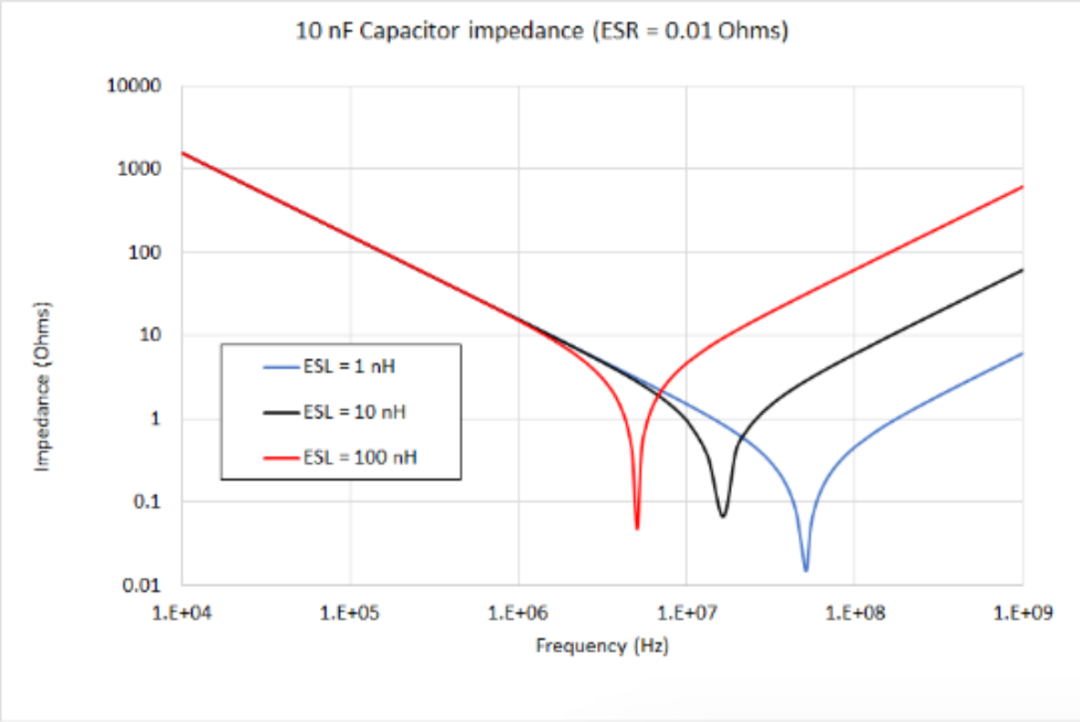

下圖顯示了 ESL 如何影響具有 0.01 歐姆 ESR 的理論 10 nF 電容器的阻抗。各種曲線顯示了不同 ESL 值(1 nH、10 nH 和 100 nH)的阻抗曲線。

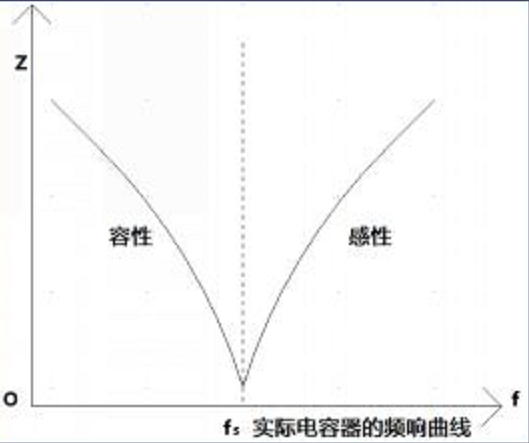

從上圖中,我們看到阻抗在自諧振頻率(也就是最低那個點)之前是容性的,(阻抗隨頻率升高而減少,呈現容性)而與 ESL 值無關;然后在高于自諧振頻率之后變為感性(因為這時候阻抗隨著頻率升高而增大,呈現感性)。

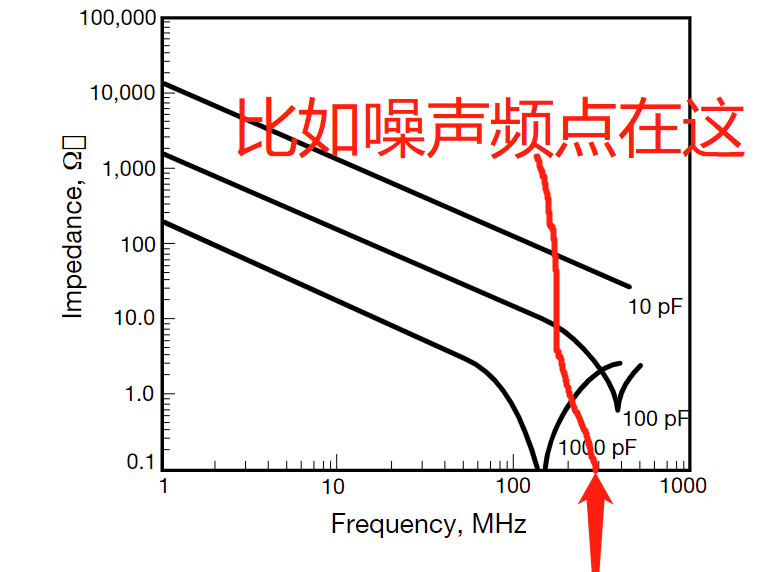

電容的最佳濾波效果就是這個自諧振頻率處,所以對于EMC的RE輻射問題,我們一般都是將輻射超標點頻率作為自諧振頻率點,然后根據這個曲線去選電容。

這樣降低ESL就有雙重意義了:

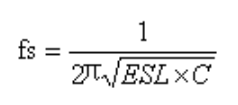

1.降低ESL,可以提高自諧振頻率,也就是上圖中最低那個點的頻率右移。這樣就可以讓電容可以前面更寬的范圍保持容性。

因為:電容的LC自諧振頻率Fs,是由下面的公式計算的:

2.降低ESL,降低高頻區域的阻抗,因為在頻率超過超過自諧振頻率fs之后,電容呈現的是感抗,跟ESL相關,這時候降低ESL,就可以降低電容的阻抗。

所以結論就是:為了提高電容的去耦濾波作用,一定要選用低ESR和低ESL的電容!

(一般電容容值越高,ESL越大,這就是為什么一般用大電容濾低頻,小電容濾高頻的原因(因為小電容ESL小,自諧振頻率高))

四、去耦電容的選型——容值及自諧振頻率

1)容值

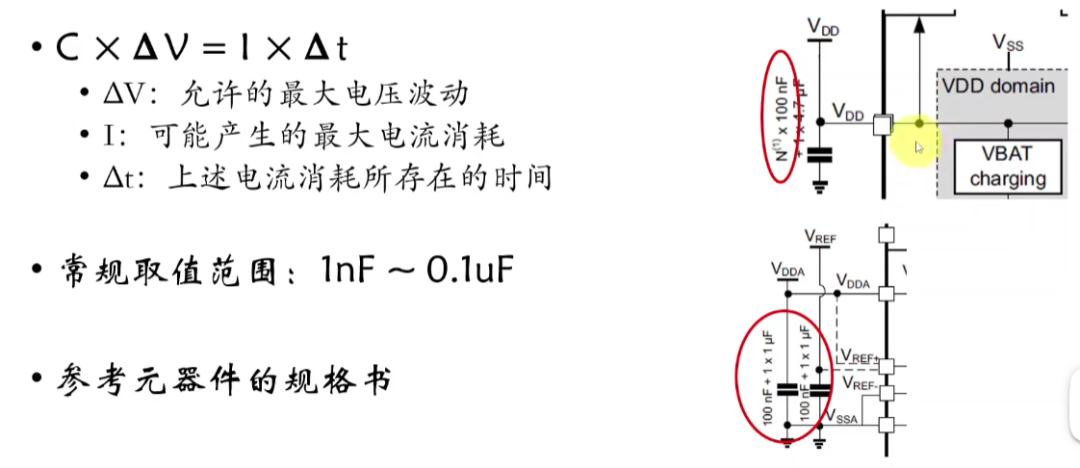

對于芯片電源引腳級別的濾波,一般可以從容值方面進行選型:

可以參照以下三種方法:

1.1)參照芯片規格書overshoot電壓手動計算

1.2)經驗值(按照100倍原則:比如10pF, 1nF,0.1uF)

2)自諧振頻率

對于EMC RE輻射超標問題,或者某些對于電源紋波特別敏感的芯片,這時候就要根據噪聲頻點,并結合電容的自諧振頻率去選電容了。

如果是想要濾除單個點噪聲,可以選擇噪聲頻點略低于自諧振頻率的電容,這時候可以達到最佳的濾波效果。

如果找不到合適封裝的怎么辦?

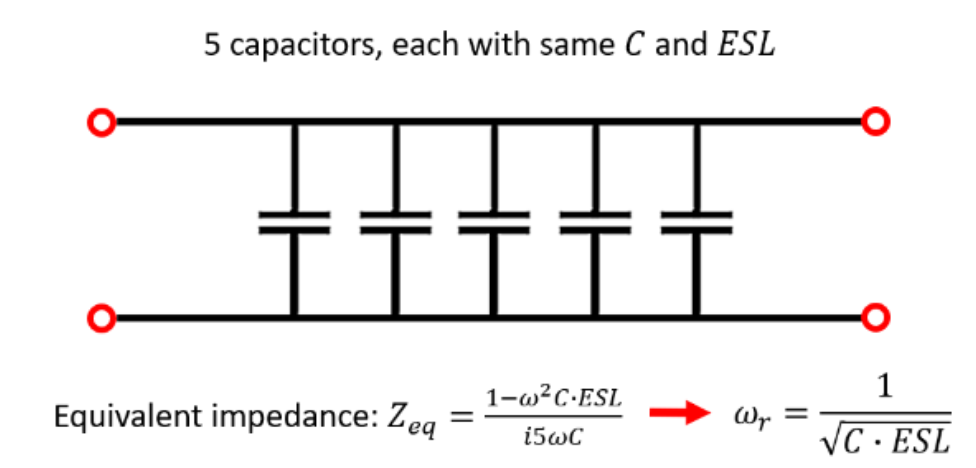

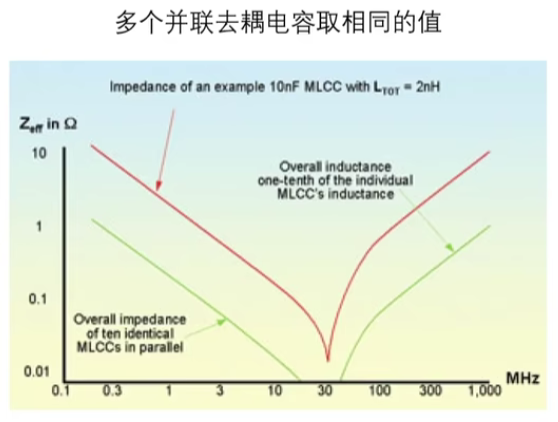

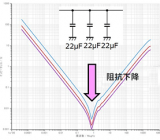

那可以選擇多個容值的電容,將他們并聯起來,并聯使用多個相同的電容會增加總等效電容并降低 PDN 阻抗,但不會改變諧振頻率。(多個電容并聯可以降低ESL)

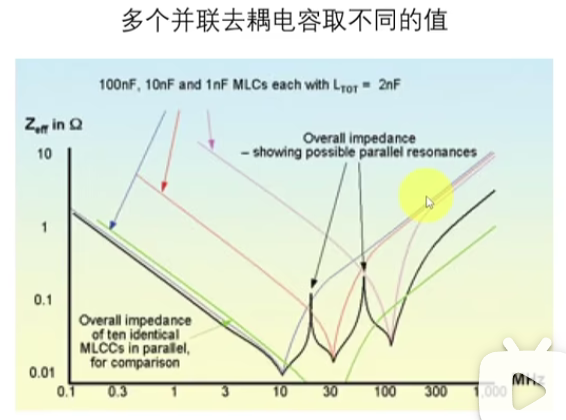

如果噪聲頻點是一個范圍,那就需要選擇多個容值的電容。

五、去耦電容的放置要求

1)就近原則:

去耦電容應盡可能的靠近芯片的電源引腳。減小去耦電容和芯片之間走線的寄生電感,去耦效果更好。

2)越小越近的原則:

小容值電容最靠近芯片,然后按照容值遞增的原則依次遠離芯片(遠離是相對的,前提是遵循就近原則)。小電容負責高頻響應,應該更靠近芯片縮短響應的時間。并且小電容可以濾除高頻噪聲,若距離芯片太遠,則電容和芯片之間的走線會重新拾取噪聲,削弱去噪效果。

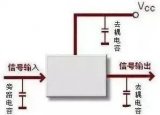

3)電源線先經過去耦電容再連接至芯片引腳

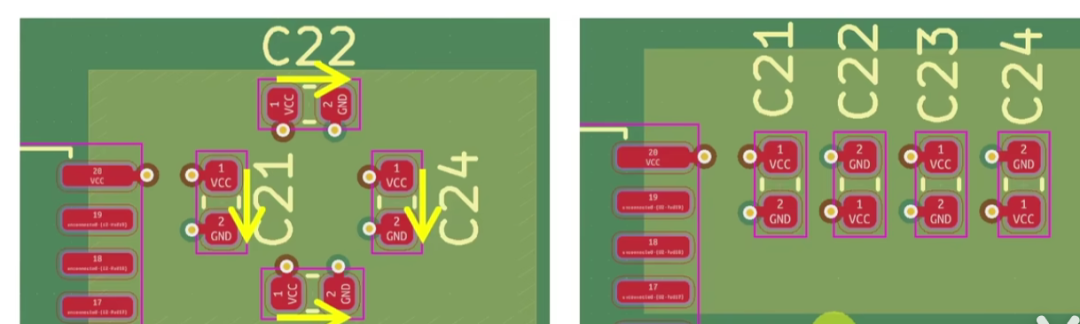

4)多個電容并聯時,最好不要平行并排放(有互感),可以改為:

審核編輯:湯梓紅

-

放大電路

+關注

關注

101文章

1757瀏覽量

106286 -

噪聲

+關注

關注

13文章

1099瀏覽量

47281 -

模電

+關注

關注

20文章

464瀏覽量

36277 -

去耦電容

+關注

關注

11文章

313瀏覽量

22258

原文標題:探索去耦電容,噪聲無所遁形

文章出處:【微信號:knifewheat,微信公眾號:小麥大叔】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

去耦電容有什么作用

去耦電容的作用和選型

去耦電容的作用和選型

評論