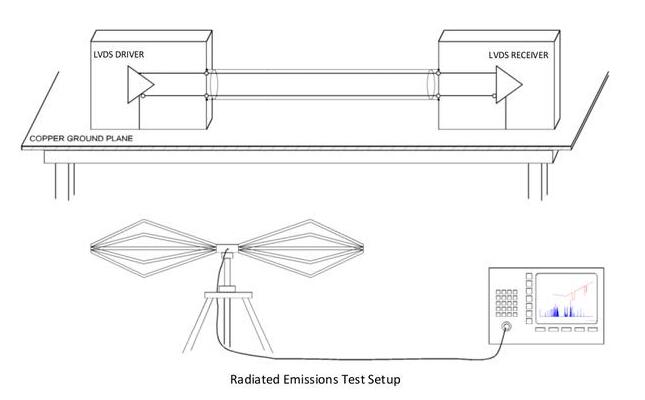

早在十幾年前信號完整性還并沒有進入硬件工程師的視野,工程師對付干擾、噪聲等問題的“三大法寶”就是接地、濾波、屏蔽,這種僅憑工程師的經驗的做法顯然非常粗放。當時的數字系統工作頻率大多都在100MHz以下,信號的上升時間也都有幾個納秒,信號完整性的問題并不嚴重;當時的數字系統的電平標準大多是TTL、CMOS電平信號線有著很大的噪聲裕量不必擔心電源噪聲的影響;當時的芯片功耗也沒有像現在一個CPU、DSP動輒就幾十瓦的功耗,不必擔心電源通流能力和電壓降的問題;當時芯片的接口電壓、核電壓并沒有現在這么低甚至到了1V以下,不必過分的擔心電源噪聲的問題。

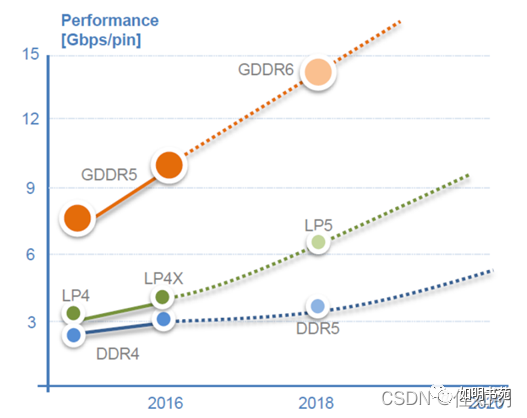

然而隨著電子通信產品性能的不斷提高、半導體工藝技術的發展,信號的最高傳輸速率已經由2004年的3.125Gbps發展到目前的28Gbps,同時供電電壓不斷降低,產品對電流的需求卻不斷地增加。這些都是高速電路設計所面臨的挑戰,使得以往僅僅通過工程師的經驗已經無法解決信號在傳輸過程中所產生的各種問題:

- 系統電流需求越來越大,使IR Drop和電源噪聲越來越難以控制;

- 供電電壓越來越低,使得芯片對電源噪聲的要求越來越高;

- 信號上升時間越來越快,使得極其細微的互連結構(比如說芯片封裝、接插件、過孔等)都會對信號質量造成影響。

- 信號幅度不斷降低,導致信號噪聲裕量不斷減小

于是人們開始認識到信號完整性和電源完整性的重要性,同時對SI和PI的研究也開始表現出了濃厚的興趣,并使得信號完整性分析成為產品開發流程中一個非常重要的工作和不可或缺的環節。

正因為如此,專業的信號完整性工程師也就誕生了,盡管目前來看專業從事SI、PI分析的工程師還比較少(雖然比前些年多多了),大部分SI、PI分析還都是由硬件工程師或者PCB工程師兼職在做。但我們也要看到信號完整性分析發展前景十分廣闊,隨著數字系統高速、高集成度、產品開發周期的不斷縮短的發展趨勢,信號完整性工程師必將在產品的開發過程中扮演越來越重要的角色。

基于信號完整性分析的設計方法

隨著電子、通信技術的發展,電子產品的功能、性能等各項指標都在不斷提高,電子產品面臨著高密度、小型化、分布式、低功耗、高可靠要求等諸多挑戰。

按照應對這些挑戰的不同應對方法,我們可以把產品的開發方式,大體上分為如下三種:

- 問題解決型

顧名思義,問題解決型是一些小公司面臨技術、資金、進度、成本等多方面壓力情況下的無奈選擇。一款產品不經過充分的評估分析,而是先做了再說。如果在調試測試過程中發現問題,再絞盡腦汁想方設法解決、補救,美其名曰“攻關克難”。這樣設計出來的產品拋開運氣成分,不可能穩定。如果問題無法解決,那就需要改版,當然啦肯定也會影響產品開發的進度,同樣也可能會付出更高的成本。

- 規則驅動型

公司發展到一定的規模,在長期的產品開發中積累了豐富經驗。將這些經驗轉化為設計規則,在產品開發過程中應用這些規則驅動、約束整個開發流程。顯而易見,這種開發方法相比“問題解決型”有了明顯的進步。但這種方法只是在經驗的積累轉化為的規則,在面臨更加復雜、性能要求更高的產品開發時,現有的規則可能并不適用。

面臨新的調整就需要新的設計方法。

- 系統設計型

“凡事預則立,不預則廢”。那么我們做硬件產品開發也需要有規范的設計流程,是“做了再說”,遇到問題再找解決的辦法,還是要先對關鍵技術、難點進行充分的評估分析,在前期找到問題的解決辦法再執行,有效的規避風險?顯然選擇后者更靠譜!

在硬件開發流程中引入SI、PI仿真分析環節就能夠有效地在設計前期解決信號、電源質量引起的問題,因此將SI、PI仿真分析引入硬件開發流程中是非常必要的。目前國內像某為、某興等大公司,都有一套自己的設計方法論、都有完整的SI、PI仿真分析流程。

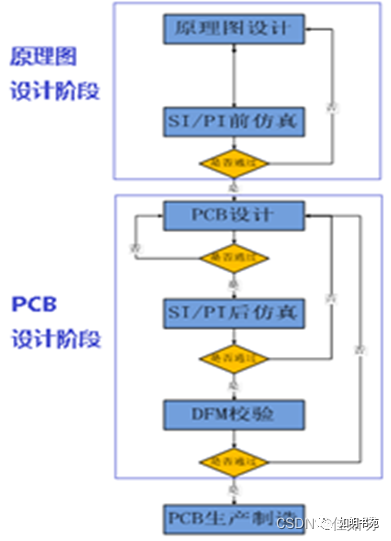

面對信號完整性方面的挑戰,以往“問題解決型”、“規則驅動型”的設計方法已經不能夠滿足需求。我們必須重新定義硬件的開發流程。為了在產品設計初期能夠及時預測、解決信號完整性方面的問題和風險,目前業界主流的硬件設計流程中都已經引入了信號完整性分析環節。

業界主流硬件設計流程圖

在設計的各個階段SI仿真分析所起到的作用如下:

- 原理圖設計階段:SI工程師參與其中,對關鍵信號和關鍵電源進行仿真分析之后給出關鍵信號的匹配方案、關鍵接口器件的buffer選型、關鍵電源的濾波方案等等;同時還給出關鍵網絡的PCB設計規則。

- PCB設計階段:SI工程師與PCB工程師溝通落實前仿真規則,待PCB設計完成后通過后仿真對信號質量和前仿真結論進行驗證。如果不能滿足要求需要與硬件工程師、PCB工程師溝通提出解決方案對PCB設計進行優化。

表面上看起來設計流程中增加了SI仿真分析環節,會導致產品設計周期的延長 ,但實際上由于能夠提前預測和解決信號完整性方面的問題,可以極大的縮短測試調試的周期,甚至一板成功的可能性也極大的提高。

-

dsp

+關注

關注

552文章

7962瀏覽量

348269 -

PCB設計

+關注

關注

394文章

4670瀏覽量

85289 -

信號完整性

+關注

關注

68文章

1397瀏覽量

95385 -

CMOS電平

+關注

關注

0文章

18瀏覽量

7174 -

DDR5

+關注

關注

1文章

419瀏覽量

24100

發布評論請先 登錄

相關推薦

信號完整性面臨的挑戰

信號完整性面臨的挑戰

評論