目前的硬件產品面臨著高密、高速的挑戰。封裝尺寸越來越小,板級布線密度越來越高;總線接口的時鐘頻率不斷提高,數據速率不斷提高,時序余量越來越小。同時信號的邊沿越來越陡,信號之間相互干擾越來越嚴重。

工藝越來越先進,信號電壓擺幅越來越小,導致信號的噪聲余量越來越小者都導致串擾造成的影響越來越嚴重。對于上個世紀90年代幾十兆赫茲的X86系統都已經是新鮮事物,IO接口的電平標準大多為5V或者3.3V的TTL電平,一個時鐘周期有幾十個ns,信號的噪聲裕量(VCC-VIH或者VIL-VSS)甚至會高達1V以上。此時,串擾對時序和噪聲的影響就顯得沒那么重要。然而,數字技術發展日新月異,現在的高速存儲器(如DDR3)速率達到1600Mbps,DDR4的速率在此基礎上翻一番達到了3200Mbps,DDR5再翻一番最高速率達到了6400Mbps。如此高的數據速率一個數據UI只有156ps,這就對系統的時序設計提出了更高的要求。同時,隨著速率的提升IO電壓也在不斷地降低,這對信號之間的噪聲干擾控制是一個新的挑戰。

廣義上來講任何兩個網絡之間都存在串擾。串擾是指有害信號從一個網絡轉移到另一個網絡,串擾是發生在一個網絡的信號路徑及返回路徑和另一個網絡的信號路徑及返回路徑之間的一種效應。

系統中信號之間串擾影響的主要表現有兩個方面:第一,串擾會使傳輸線的特征阻抗和傳播速度發生變化,影響系統的時序問題;第二,串擾會在其它傳輸線上引入感應噪聲,使信號的噪聲容限減小。這一噪聲也有可能發生在信號的邊沿導致抖動增加或者時鐘信號邊沿不再單調,等等這些都可能導致系統設計的失敗。

01

電路角度理解串擾

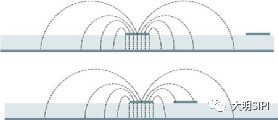

當信號沿傳輸線傳播時,信號路徑和返回路徑之間將產生電力線;圍繞在信號路徑和返回路徑周圍也有磁力線圈。這些場會延伸到周圍的空間。相鄰傳輸線之間的場的相互作用就會產生串擾。

我們可以把這種電場和磁場的耦合,簡化為電路中的容性和感性耦合。串擾就主要表現為容性串擾和感性串擾。

串擾是不同傳輸線之間的能量耦合,引起串擾的原因不同傳輸線或者信號的傳輸路徑之間存在著電磁場耦合。這一耦合只與作為信號傳輸載體的傳輸線的無源特性相關。有人會說,傳輸線間的耦合如果只和傳輸線結構的無源特性相關,那為什么隨著信號速率的提高串擾會越來越嚴重呢?

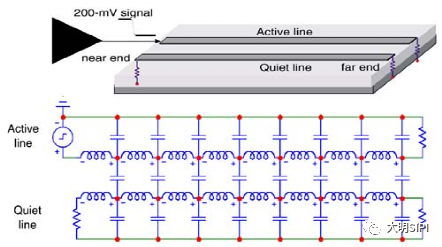

傳統的信號完整性理論都會把傳輸線間的電磁場耦合分成容性耦合和感性耦合。兩條傳輸線通過電場產生的耦合以互容Cm表示,侵害網絡通過互容在受害網絡上引起的噪聲電流

傳輸線間通過磁場產生的耦合以互感Lm表示,侵害網絡通過互感在受害網絡上引起的噪聲電壓

可見,噪聲電流Ic與互容Cm和電壓變化率dV/dt成正比,噪聲電壓VL同互感Lm和電流變化率dI/dt成正比。

其中,Cm和Lm代表了傳輸線間的耦合,即傳輸線的無源特性;

電流噪聲Ic乘以被害網絡的阻抗也可以表示為噪聲電壓;

dV/dt其實就是信號邊沿的斜率,反映的是激勵信號的特性。

在信號幅度一定的情況下噪聲電流和信號的上升時間成反比,同樣由噪聲電壓的計算公式也可以得出這一結論。

實際上信號的上升時間dt的長短對應的就是信號的頻譜帶寬,信號上升時間越短信號的有效頻譜成分越高產生的串擾噪聲越大,信號的上升時間dt越大信號的有效頻譜成分越低產生的串擾噪聲越小。分析到這一層次,我們可以清楚地知道串擾與無源的傳輸線的物理結構和激勵信號本身特性這兩個方面相關,無源的傳輸線的物理結構確定以后,串擾的值由激勵信號的特性所決定,也就是說不同頻率成分的信號通過同一無源系統所產生的串擾也是不同的。

01 - 1

容性串擾

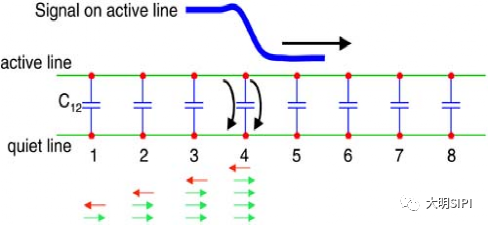

如下圖所示,把信號的上升沿看作是沿動態線移動的電流源,信號前沿區,有容性耦合電流流入靜態線。

上圖所示,紅色箭頭所示為后向電流,下面綠色箭頭所示為前向電流。它們的傳播及疊加示意如上,前向電流和后向電流方向相反,但產生的噪聲電壓都是正的。

很明顯,綠色的前向電流產生的噪聲隨著時間的推移寬度不變,但幅度在增大;而紅色所示的后向電流產生的噪聲幅度不變、寬度在增加,直到信號邊沿到達接收端前向噪聲電壓的寬度達到最大值2倍的TD(傳輸線延時)。

01 - 2

感性串擾

相鄰布線之間的互感在受害網絡產生一個感應電壓。

上圖所示,上邊紅色箭頭是后向電壓,下面綠色箭頭是前向電壓的傳播及疊加示意圖。前向噪聲電壓為負和后向噪聲電壓為正。

與容性串擾類似,綠色的前向電流產生的噪聲隨著時間的推移寬度不變,但幅度在增大;而紅色所示的后向電流產生的噪聲幅度不變、寬度在增加,直到信號邊沿到達接收端前向噪聲電壓的E寬度達到最大值2倍的TD(傳輸線延時)。

01 - 3

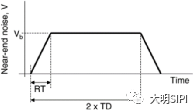

近端串擾

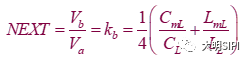

近端串擾其實就是后向的容性和感性串擾之和。上面對于容性和感性串擾的分析可知,在大于RT時間之后無論容性和感性的后向串擾的幅度都是固定的。如下所示為近端串擾的計算式,串擾僅和互容、互感與傳輸線自容、自感的比值相關。

下圖為微帶線和帶狀線在不同線間距情況下的近端串擾系數。可明顯看出:隨著線間距增大,近端串擾減小,當信號線間距在3W以上時,近端串擾在一個比較低的水平。

01 - 4

遠端串擾

遠端串擾其實就是前向的容性和感性串擾之和。上面對于容性和感性串擾的分析可知,遠端串擾會隨著信號的向前傳播而累加。如下所示為遠端串擾的計算式,遠端串擾和互容、互感與傳輸線自容、自感的比值相關,并且容性前向串擾和感性的前向串擾方向相反。

遠端串擾系數:

我們注意到:如果所有導線周圍的介質材料是同質的,而且是均勻分布的,如兩條耦合的完全嵌入式微帶線或兩條耦合帶狀線,則相對容性耦合和相對感性耦合是完全相同的,在這種結構中就不會出現遠端串擾。

而微帶線由于信號線的介質在PCB板上是PP,板外的介質是空氣,有著不同的介電常數。因此,微帶線的遠端串擾要大于帶狀線。

而實際上,我們使用的介質并不是均勻的:

(1)通常的FR4介質是由玻璃纖維和環氧樹脂編制而成,而玻璃纖維和樹脂的介電常數是不同的。

(2)玻璃纖維的編織有疏有密;不同類型的介質樹脂的含量也不盡相同。

因此,實際的設計中,帶狀線也會還是會存在遠端串擾。使用介電常數為均勻穩定的介質,并盡量使用帶狀線布線對減小串擾、提高高速鏈路性能非常重要。

02

電路角度理解串擾的局限

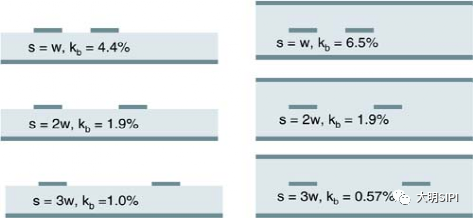

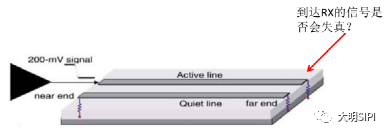

以上所講的容性、感性、近端、遠端串擾都是從電路的角度來理解串擾。不知道大家有沒有發現一些不對的地方。按照容性串擾和感性串擾前向串擾的解釋,前向串擾的值應該是一直疊加下去,信號線越長,串擾的幅值越大才對。但實際的測試情況是這樣的嗎?

真實的近端和遠端串擾的測試結果如下,我們發現遠端串擾是會飽和的,并不會無限的增大下去。

傳統的、電路角度的串擾解釋是在假設產生串擾的過程中,也就是信號在傳輸的過程中,信號本身沒有變化的基礎上得出的結論!

顯然這是不可能的。因為隨著信號的傳輸,信號的能量已經通過容性和感性耦合進入到了受害網絡了,這樣的話攻擊線上的信號本身已經有了一定的衰減。

攻擊線上的入侵信號也會失真。這個失真主要來自于兩個方面:

(1)傳輸線損耗;

(2)耦合到受害網絡上的能量。

上面所講到的容性串擾、感性串擾、近端串擾、遠端串擾的公式都是從電路角度得出的,目的是便于我們理解串擾,但并不準確。因此,那些公式沒必要死記硬背,只需要了解串擾和哪些因素相關即可。后面有機會會講一下S參數,用S參數來表示串擾更加方便也更準確。

03

串擾的控制

接下來該講一講控制串擾的方法。首先從信號路徑考慮控制串擾:

?減小走線并行長度;

?拉大布線間距;

?避免相鄰層布線;

?減小傳輸線與參考平面的間距。

?關注阻抗的影響!

驅動器的阻抗一般比較低,如果沒有匹配的話在串擾到達驅動器端將發生負反射(反射系數為負數),串擾將返回遠端影響負載的接收。

對于TTL、CMOS等電平負載端阻抗一般為高阻,遠端串擾會在負載端由于全反射而加倍。

因此,源端和負載端的阻抗匹配,不僅能夠消除有用信號的反射,而且也能消除串擾信號的反射,有利于降低串擾。

其次,減小串擾不僅需要從信號路徑入手更要關注信號的返回路徑,同時也要考慮相鄰過孔之間的垂直耦合。

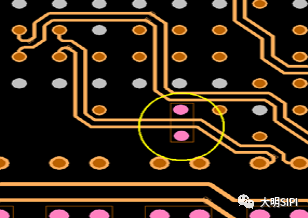

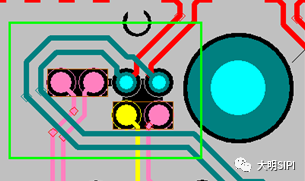

?布線與過孔之間:關鍵信號不要走進其它信號的antipad區域。其它信號也不能進入關鍵信號過孔的antipad。

?過孔與過孔之間的垂直耦合:由于信號在流經過孔時,返回路徑比較復雜,因此如果過孔之間的間距太近,串擾也會非常嚴重;

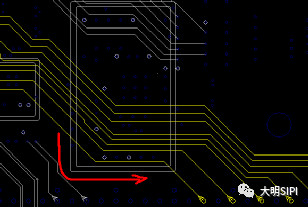

?返回路徑之間:如一組總線同時跨分割的情況,雖然信號線間距比較大,但是會存在很多信號的返回路徑重疊的情況,也會產生嚴重的串擾。

?布線與平面之間(電源);如果信號線以高電壓、大噪聲的電源為參考平面,那么電源噪聲也會耦合到信號線上。

-

CMOS

+關注

關注

58文章

5689瀏覽量

235171 -

PCB板

+關注

關注

27文章

1443瀏覽量

51523 -

TTL電路

+關注

關注

2文章

65瀏覽量

15064 -

信號完整性

+關注

關注

68文章

1398瀏覽量

95392 -

電磁場

+關注

關注

0文章

790瀏覽量

47238

發布評論請先 登錄

相關推薦

DAC信號完整性淺析 DAC信號完整性解決方案

淺析信號完整性中的串擾

淺析信號完整性中的串擾

評論