對于點到點拓撲我們只需要注意選擇合適的匹配方式,并優化好整個channel的阻抗即可,但是當一個網絡上的器件超過兩個時,信號可以選擇的拓撲結構就會變得非常豐富了。此時如何根據信號特性以及器件的布局布線等約束選擇合適的拓撲結構和匹配方式就變得尤為重要。對于PCB板的布線瓶頸處的布線拓撲選擇就可能對PCB板的所需的布線層數起到決定性作用,這直接關系到產品的成本;而對于一些關鍵的高速總線接口的拓撲結構選擇又關系到系統的性能指標。因此,在實際的產品開發中多負載拓撲結構的選擇意義重大,可能直接關系到產品的成本、性能等競爭力。

01

菊花鏈拓撲簡介

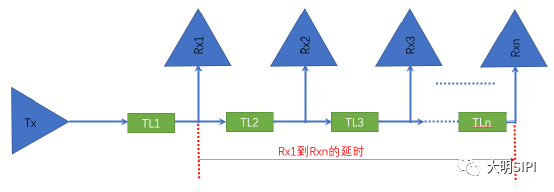

菊花鏈是比較常用的一種拓撲結構,它將各個負載端依次相連。

如上圖所示,當Rx1到Rxn的互連線不能表現出傳輸線效應時,用菊花鏈拓撲是一個非常好的選擇。也就是說當負載的位置相對比較集中,也就是最靠近驅動器的負載(Rx1)和最末端的負載(Rxn)之間的布線延時小于信號上升時間的1/6時,用菊花鏈拓撲結構會比較好。此時可以近似的認為Rx1和Rxn之間是集總的。因此,有好多低速的總線都是走的菊花鏈拓撲,如I2C、JTAG等總線,信號速率低、上升時間往往是ns級的,往往負載會很多,這個時候菊花鏈就是比較好的選擇,一般也不會出什么問題。

一些老資格的硬件或者layout工程師往往認為這種低速信號可以隨便走,不會出問題。的確,對于一個上升時間2~3ns的信號,如果布線延時不足0.5ns時不會有什么問題,但如果系統更大,布線更長的時候就可能出現問題,此時就需要SI仿真來解決問題。

更有甚者,PCB設計都沒有變,老版本運行正常,而新版本的單板由于使用了工藝升級后的器件就問題頻出,這又是什么原因呢?

其實,問題就出在芯片的工藝升級上了。同樣一個驅動器老版本的使用28nm工藝,新版本使用14nm工藝,新的工藝驅動能力更強信號的上升時間更短。使得老版本上沒有體現出傳輸線效應的互連線體現了傳輸線效應,從而導致了SI問題。

那么,還是讓我們來仔細探討一下菊花鏈拓撲吧。下圖為菊花鏈拓撲結構的示意圖,同時也對拓撲結構中各個點的信號特點進行了說明。

假設拓撲結構中驅動器的輸出阻抗和傳輸線阻抗Z0匹配,驅動器的IO電壓為VCC,此時T0點的入射電壓幅值為VCC/2在鏈路的末端(負載3)發生全反射,反射電壓的幅值也是VCC/2。在這種拓撲結構下我們可以發現各個負載所接收到的信號的特點。

(1)驅動器和傳輸線的阻抗匹配情況決定了傳輸線入射波的電壓和反射情況。假設驅動器輸出阻抗和傳輸線阻抗匹配,入射波只在末端發生一次反射;

(2)首先負載3處入射波和反射波之間沒有延時因此得到的信號邊沿單調。同時正是因為入射波和反射波完全重疊,導致如果驅動能力過強導致入射波和反射波都存在過沖的話,最末端的負載3的過沖也會是最大的,邊沿斜率是最陡的。

(3)在負載2和負載1處則會由于入射波和反射波之間存在的延時而導致接收到的信號存在臺階或者回溝。由上面的示意圖我們不難理解當驅動器和傳輸線阻抗匹配時在負載2和負載1處有可能出現臺階,欠驅動情況下可能只是使信號邊沿變緩,而在過驅動情況下信號邊沿就有可能會出現回溝了。TD2等于2倍的TL3的延時, TD1等于2倍的TL2+TD3的延時,TD0等于2倍的TL1+TL2+TD3即整個網絡的總延時。由此可知越靠近源端的負載接收到的信號在邊沿處存在的回溝或者臺階就越大。

另外在負載端是否會產生臺階或者回溝不僅和負載到拓撲最末端的延時有關,而且還和驅動器輸出信號的上升下降時間有關。當負載到拓撲末端的延時小于信號上升時間的1/3時就不會在負載處觀測到明顯的臺階或者回溝,但是負載到拓撲末端的延時超過上升時間的1/3臺階或回溝就會變得明顯起來。

使用3.3VLVCMOS的驅動器和負載進行仿真。設置TL1 = 2000mil,TL2、TL3都是長度為1500mil的50ohm傳輸線。信號線的延時按照170ps/inch進行估算,此時負載1到末端的延時TD1/2為510ps、負載2到末端的延時TD2/2為255ps。我們通過IBIS模型中的[Ramp]關鍵字得到驅動器輸出上升時間為500ps左右,下降時間1ns左右(具體計算方法參見第七章IBIS模型介紹);通過IBIS模型的pullup、pulldown曲線來估算驅動器輸出阻抗為20ohm。分別在過驅動、阻抗匹配、欠驅動三種情況下進行仿真分析

驅動器輸出未加匹配電阻時即為過驅動情況,仿真結果如下:

三個負載處的接收波形如上所示。藍色點虛線為負載1處的波形,其上升沿都存在1ns左右的回溝,下降沿隱約有些臺階但并不明顯。這是由于驅動器輸出的上升沿要比下降沿快,所以負載1到末端的延時和上升時間相當但卻只有下降時間的一半。負載1處的波形過沖幅值是最小的;紅色短劃虛線為負載2處波形,只表現出了上升下降邊沿比較緩并沒有明顯的臺階,其過沖比負載1處的稍微大一些;綠色實線為負載3處的波形,邊沿單調且斜率最大,同時過沖也達到了最大值。由于過沖和振鈴的存在使信號的噪聲余量也有了明顯地降低。下面再對阻抗匹配的情況進行仿真我們就可以知道阻抗匹配的重要性。

驅動器輸出添加30ohm匹配電阻使輸出阻抗匹配,仿真結果如下:

如上所示,此時所有負載端的過沖和振鈴都消失了,而且負載1上升沿的回溝也變成了臺階。可見阻抗匹配在菊花鏈拓撲中也具有重要的作用。欠驅動的情況這里不再分析,有興趣的讀者可以自行驗證。其實驅動器的輸出阻抗一般都會比傳輸線阻抗要小,過驅動是普遍存在的情況,如果過沖振鈴能夠滿足要求我們一般可以不考慮阻抗匹配了,當信號質量不可接受時,我們才會選擇加串阻來解決阻抗匹配問題,并不會故意設計成欠驅動的情況。

顯然菊花鏈拓撲所產生的回溝或臺階的危害性是非常大的。對于數據信號回溝或臺階會影響信號的時序裕量,對于時鐘信號如果存在回溝,很可能會被接收器件識別成雙時鐘沿,此時鐘再去采數據就會產生錯誤。因此,這種菊花鏈拓撲只能應用于低速總線中。

02

菊花鏈拓撲信號質量改善

如何來改善菊花鏈拓撲結構的信號質量,可以從下面幾個方面考慮:

1、明確驅動器的上升下降時間后,可以考慮將離驅動器最近的負載到最末端的負載的延時控制在上升下降沿的1/3以內。如果是時鐘信號只是上升沿采樣那么我們只需關注上升時間即可。但這一點往往很難做到,像PCI、local BUS、JTAG、IIC等低速總線上的負載往往很多而且布局位置可能分布在PCB板各個位置,距離會比較遠。

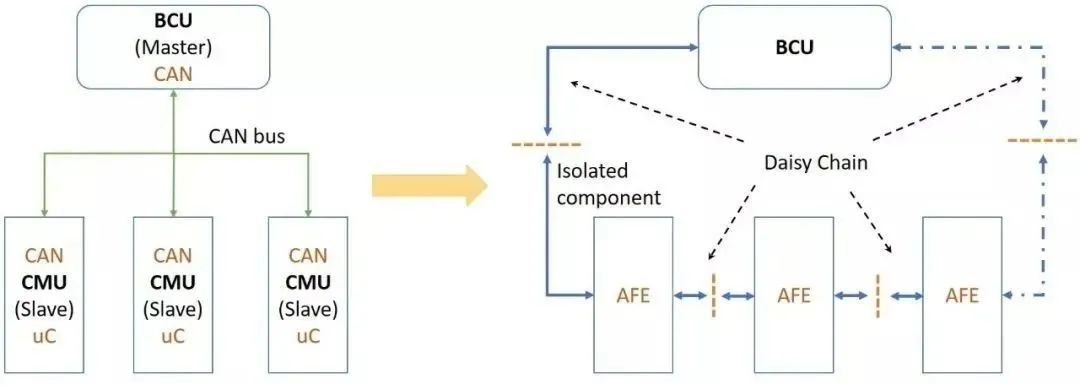

2、在菊花鏈的末端加戴維南端接消除拓撲末端的反射,進而可以消除靠近驅動端的負載的臺階或者回溝。這種拓撲結構也是DDR地址控制信號fly-by拓撲的雛形,使其有應用于高速并行總線的可能。

但是需要注意,通常在戴維南匹配中選擇R1=R2且R1||R2=Z0,源端如果匹配的情況下接收信號的低電平為1/4VCC、高電平為3/4 VCC,高低電平到VIH和VIL的余量會大大地減小。因此,如果是CMOS或者LVTTL電平,使用戴維南匹配源端不必做阻抗匹配保持過驅動就可以了。

戴維南匹配示意圖如下:

如上所示末端的戴維南匹配消除了末端反射,使得每個負載接收到的波形都和入射波形基本一致,且邊沿單調沒有臺階和回溝以及過沖。此時入射波的幅值就決定了負載端的電壓幅值以及高低電平的噪聲裕量,驅動器的驅動能力越強、輸出阻抗越小負載接收到的信號幅值就會越大。

使用戴維南端接只是消除了拓撲最末端的反射,實際的拓撲中存在著很多阻抗不連續的點,我們很難將他們一一消除,這將付出非常大的代價。比如說每個負載處都會有負載的fanout過孔和很短的分支布線,當負載比較少只有2~3個時我們可以不必在意,但是如果整個拓撲的負載有很多甚至達到7、8個甚至10個以上那么這些過孔分支布線帶來的影響就必須重視了。

我們需要研究在布線的分支處到底發生了什么。入射波在分支點處同樣會發生反射。入射波在分支點處向右看過去的阻抗相當于負載處的Stub和TL2并聯ZT=Z0||Z0=0.5*Z0,此時在分支點處發生反射系數為(0.5Z0-Z0)/(0.5Z0+Z0) = -1/3的負反射,這一反射只是在入射信號經過分支點處的瞬間發生過了分支點后的阻抗依舊是連續的。因此,這一反射會在信號的邊沿產生一個微小的臺階或者回溝。

負載少時這種影響并不顯著,當拓撲中的負載非常多時就會嚴重影響信號質量哪怕是再末端加戴維南匹配也不能完全消除反射。

3、在存在臺階或者回溝的負載端加串阻消除回溝或者臺階。

在點到點拓撲的分析中已經介紹了在末端加串阻能夠消除過沖和振鈴,同樣也能夠消除回溝和臺階,但這都是需要犧牲信號邊沿斜率。在介紹菊花鏈拓撲時我們做的仿真中負載1上升沿存在嚴重的回溝,那么我們在負載1處加一個串聯電阻Rs =100ohm,拓撲如下所示:

如上所示紅色短劃虛線所示為未加串阻Rs的波形,此時上升沿存在明顯的回溝;藍色點虛線所示為加200ohm串阻的波形上升沿的回溝已經消除只是稍有臺階;綠色實線所示將串阻Rs增大到了400ohm,此時臺階進一步減小。此外我們也可以觀測到隨著串阻的阻值增大負載1接收到的波形邊沿越來越緩。

4、驅動器端加到地的電容Cp,增大輸出信號的上升下降時間也可以改善負載端接收的波形;

對不同容值的Cp進行仿真,對比負載1的接收波形如下所示:

如上所示藍色短劃虛線所示為未加Cp時的波形,此時上升沿存在明顯的回溝;紅色點虛線所示為Cp=10pF時的波形,上升沿的回溝已經消除只是稍有臺階;綠色實線所示將Cp增大到20pF,此時臺階進一步減小。此外我們也可以觀測到隨著Cp的容值值增大負載1接收到的波形邊沿越來越緩。負載的容值可以根據回溝的大小經過仿真來確定。

以上這些解決菊花鏈拓撲信號完整性問題的方法需要在具體的設計中靈活應用,如果始終不能解決問題那就需要考慮更換信號的拓撲結構。

-

驅動器

+關注

關注

51文章

7998瀏覽量

145024 -

DDR

+關注

關注

11文章

697瀏覽量

64937 -

PCB設計

+關注

關注

394文章

4648瀏覽量

84552 -

jtag接口

+關注

關注

0文章

34瀏覽量

13619 -

菊花鏈拓撲

+關注

關注

0文章

7瀏覽量

1928

發布評論請先 登錄

相關推薦

【分享】Altium 4層核心板(菊花鏈拓撲)案例

我的板子之前是按照fly-by拓撲(菊花鏈)布線,之后板子縮小打算用T行拓撲布線,有用過的大神知道可以直接更改嗎?

請問什么是菊花鏈的概念?

ddr3菊花鏈拓撲結構是什么

探討一下菊花鏈拓撲結構

探討一下菊花鏈拓撲結構

評論