引言

納米線(NWs)已經為氣體和生物傳感提供了一個極好的平臺, 從而研究如何使納米線的表面功能化,由于納米尺度尺寸與分子尺寸兼容性,導致我們需要考慮如何使納米線的表面功能化,從而以良好的選擇性檢測特定的氣體分子。

在這種情況下,可以設計NW晶體管,其響應于氣體分子的“吸收”或“相互作用”,通過溝道的載流子傳輸受到影響并被發送信號。對于場效應晶體管來說,為了降低器件尺寸縮小帶來的短溝道效應(SCE)和功耗,橫向和縱向柵環繞(GAA)場效應晶體管已經成為取代FinFet的趨勢。因此,制造精確和可控尺寸的納米線或納米片已經成為一項重要的技術。

實驗與討論

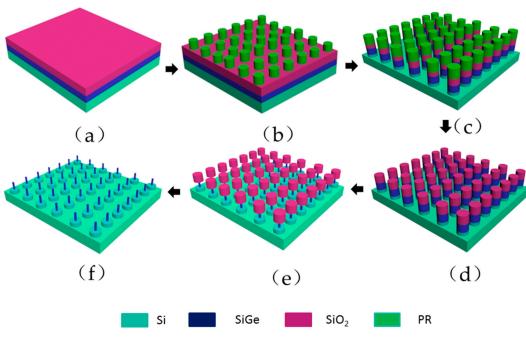

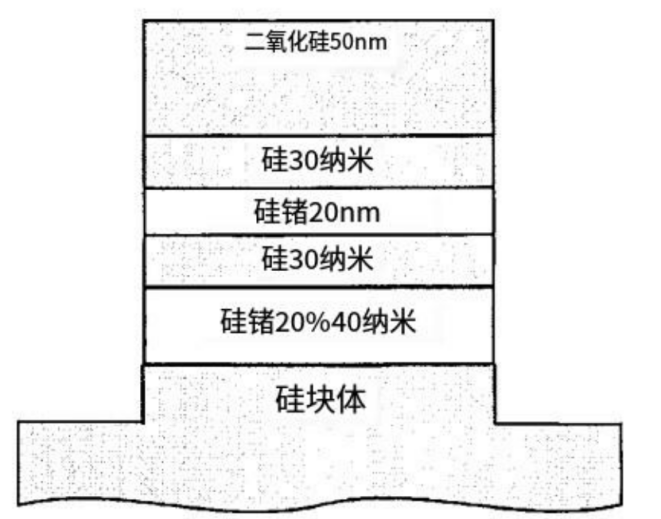

圖1:納米柱制作流程

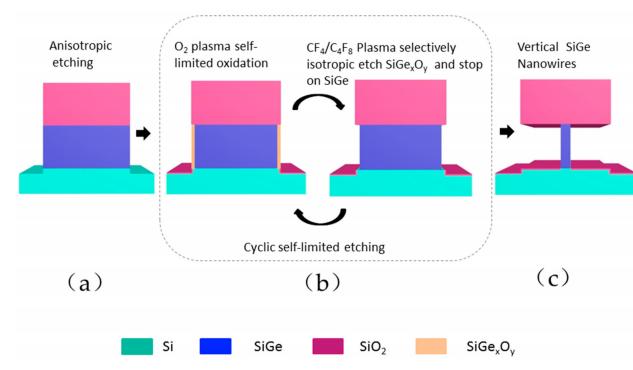

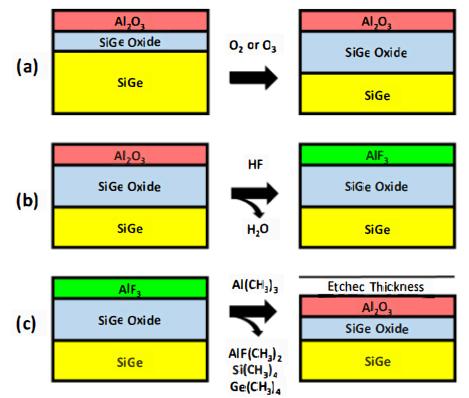

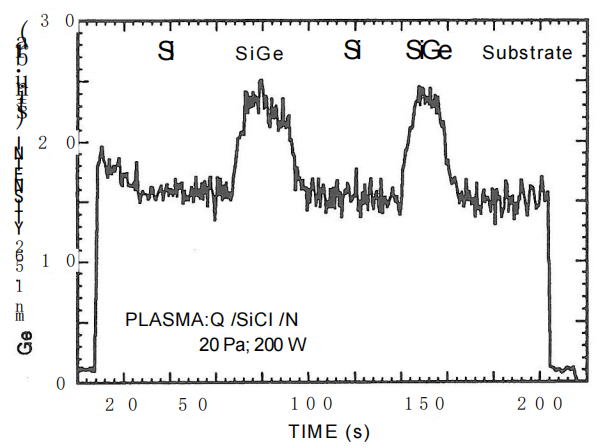

所有材料都是在8英寸(100)硅片上進行的,納米柱的制造流程如圖1,我們通過圖2所示的循環蝕刻過程進行實驗。這主要是兩個自限過程:(1)O2等離子體自限氧化:150sccm O2,500 W源RF/0W偏置功率,處理可達到氧化飽和狀態;(2)SiGexOy選擇性刻蝕:200 sccm CF4/x sccmC4F8/500W源射頻功率/0W偏置功率,用于SiGexOy的選擇性刻蝕和SiGe表面的自限停止。重復步驟(1)和(2),直到SiGe納米線的直徑達到預期值。

圖2:垂直納米線的蝕刻過程

自限制順序反應是原子層蝕刻的主要特征,SiGe的氧化在某些條件下是自限制的。因此,本研究的重點是如何實現SiGexOy的自限性去除(見圖2)并自動停止在SiGe層上。我們知道SiGe在O2等離子體下可以氧化成SiGexOy,Si可以氧化成SiO2,但是在形成這些之前,氧化物需要打開原來的共價鍵。

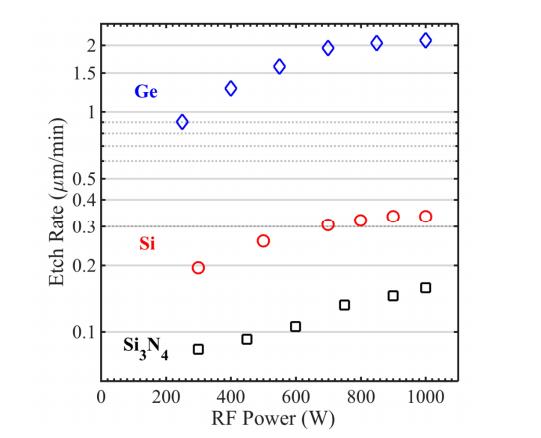

Si–Si鍵能(2.31 eV)> Si–Ge鍵能(2.12 eV),因此SiGe合金比純Si更容易發生鍵氧化,Si–O鍵能(9.0 eV)大于Ge–O鍵能(5.0 eV),Si–O–Ge鍵能的值介于兩者之間,所以使用CF基氣體刻蝕氧化物會形成揮發性的SiFx和GeFx以及CO或CO2。從圖中可以看出當CF4流速固定在200sccm并且C4F8比率超過20sccm時,SiGe蝕刻已經被完全抑制,從而實現了SiGexOy層選擇性蝕刻的自限制效應。

結論

通過ALE蝕刻,英思特獲得了一種制造納米線的創新方法。根據研究結果表明,納米線的直徑可以在60 ~ 16.5nm范圍內靈活調節,形貌精確可控,微結構完整,界面上也沒有明顯的刻蝕殘留物污染。ALE方法可以與先進的光刻(如初始線寬控制到<45nm)技術相結合,未來將有望獲得更小的高密度納米線。這種技術在傳感器方面將有非常廣泛和有前途的應用。

江蘇英思特半導體科技有限公司主要從事濕法制程設備,晶圓清潔設備,RCA清洗機,KOH腐殖清洗機等設備的設計、生產和維護。

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27010瀏覽量

216307 -

晶體管

+關注

關注

77文章

9634瀏覽量

137849 -

蝕刻技術

+關注

關注

0文章

23瀏覽量

7834

發布評論請先 登錄

相關推薦

雷尼紹測頭為什么具有各向同性

鍺化硅工藝在高速通信領域有哪些應用?

《炬豐科技-半導體工藝》CMOS 單元工藝

關于原子層蝕刻的分析和介紹

各向同性和各向異性工藝如何用于改善硅濕蝕刻

常見的各向同性濕法刻蝕的實際應用

【虹科方案】如何提高電場探頭測量精度?——各向同性的重要性(2)

【虹科EMC測試系列】如何測量各向同性場?

鍺、硅、SiNx薄膜的各向同性等離子體蝕刻

鍺化硅(SiGe)和硅(Si)之間的各向同性和選擇性蝕刻機制

一種新型的鍺化硅(SiGe)干式選擇性各向同性原子層蝕刻技術

一種新型的鍺化硅(SiGe)干式選擇性各向同性原子層蝕刻技術

評論