根據(jù)《通信原理》一書可知,m序列是最長線性反饋移位寄存器的簡稱,它產(chǎn)生的偽隨機(jī)序列的周期與其反饋移存器級數(shù)有關(guān);

m序列的屬性有很多,比如:

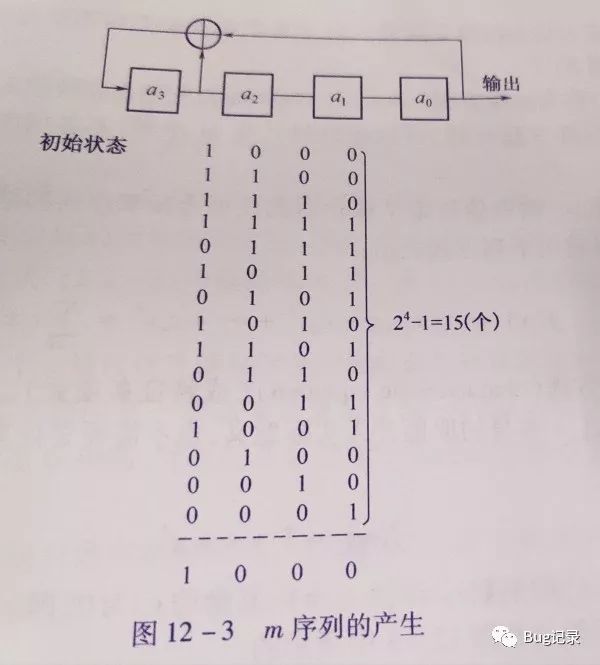

- 周期性,它的周期與它的反饋寄存器的級數(shù)有關(guān),周期為2的級數(shù)N次方-1,比如級數(shù)為4,則周期為2^4-1,即15;

- 均衡性,一個(gè)周期內(nèi)'1'的個(gè)數(shù)比'0'多一個(gè);

假設(shè)一個(gè)4級m序列的初始狀態(tài)為(a3,a2,a1,a0) = (1,0,0,0),特征多項(xiàng)式為23;

移位一次,a3與a0模2相加產(chǎn)生新的輸入a4=1^0 = 1,則新的狀態(tài)為(a3,a2,a1,a0) = (1,1,0,0),輸出為0;

依次移位15次后又回到初始狀態(tài)(1,0,0,0)。所以4級反饋移存器的周期為15。

從書上拍下的圖 圖1

從書上拍下的m序列框架圖 圖2

從圖2可以清晰的看出m序列的框架原理,只需要N位寄存器,并整體左移/右移,不斷地做異或運(yùn)算,產(chǎn)生新的值,;

以圖1為例,使用特征多項(xiàng)式23,也就是'010 011',原始狀態(tài)為'1000';參照圖2的框照圖,可以知道n = 4, c1 = c0 = c4 = 1, c2 = c3 = 0;

m序列的實(shí)現(xiàn)大致如下:

圖3 m序列產(chǎn)生always塊

可以看到,當(dāng)en為高的時(shí)候,data_count會更新相應(yīng)的值,同時(shí)data_out會產(chǎn)生新的輸出值;

en信號在這里作為一個(gè)使能信號,它的作用是為了解決高速時(shí)鐘下低速運(yùn)行的問題;

以m序列的產(chǎn)生為例,假設(shè)需要產(chǎn)生符號速率1Mbps的偽隨機(jī)序列,而FPGA的晶振為50MHz,而初學(xué)者為了在50MHz下按照1MHz的頻率運(yùn)行,通常會用兩種方法:

- 使用各種分頻的方法將50MHz分頻出1MHz;

- 使用PLL等IP核將50MHz輸入之后鎖定輸出1MHz;

而這兩種方法都會產(chǎn)生兩種時(shí)鐘域(1MHz,50MHz),兩個(gè)時(shí)鐘域之間的數(shù)據(jù)通信通常又會牽扯到跨時(shí)鐘域同步,亞穩(wěn)態(tài)等問題;

那么有沒有一種方法能夠在50MHz下按照1MHz的頻率運(yùn)行?有,使用使能信號控制頻率運(yùn)行。

使能信號的作用就相當(dāng)于一個(gè)定時(shí)器鬧鐘,定時(shí)會拉高一次,提醒電路該運(yùn)行一次了,然后電路進(jìn)入空閑狀態(tài)等待下一次使能信號拉高;

這么做的好處有以下幾點(diǎn):

- 減少了其他的時(shí)鐘,F(xiàn)PGA設(shè)計(jì)需要遵循盡可能少的時(shí)鐘域原則;異步時(shí)鐘域之間的信號同步,亞穩(wěn)態(tài)問題都可以避免;

- 降低了設(shè)計(jì)難度,不需要使用IP核,不需要考慮跨時(shí)鐘域的處理;

- 便于FPGA實(shí)現(xiàn),因?yàn)镕PGA內(nèi)部的寄存器本來就有使能en端,實(shí)現(xiàn)起來方便;

使能信號的產(chǎn)生原理也很簡單,使用計(jì)數(shù)器不斷地計(jì)數(shù),同時(shí)使能信號保持低電平;當(dāng)計(jì)數(shù)到固定值時(shí),使能信號拉高,計(jì)數(shù)器歸零;

設(shè)計(jì)內(nèi)容如下:

圖3

這里INTERVAL是一個(gè)常量,可以在實(shí)例化的時(shí)候修改這個(gè)常量值;

其實(shí)這個(gè)常量值可以設(shè)為輸入端口,這樣可以在運(yùn)行的過程中在線修改使能信號的周期,更為方便;

最后的VCS仿真圖如下:

圖4 仿真圖

得出來的數(shù)字與圖1完全對應(yīng),仿真成功!

總結(jié):

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26489 -

移位寄存器

+關(guān)注

關(guān)注

2文章

258瀏覽量

22238 -

BPSK

+關(guān)注

關(guān)注

0文章

34瀏覽量

22918 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6397 -

Verilog語言

+關(guān)注

關(guān)注

0文章

113瀏覽量

8219

發(fā)布評論請先 登錄

相關(guān)推薦

跨時(shí)鐘域控制信號傳輸設(shè)計(jì)方案

關(guān)于跨時(shí)鐘域信號的處理方法

quartus仿真雙口RAM 實(shí)現(xiàn)跨時(shí)鐘域通信

怎么實(shí)現(xiàn)m序列信號發(fā)生器的設(shè)計(jì)?

FPGA跨時(shí)鐘域處理簡介

看看Stream信號里是如何做跨時(shí)鐘域握手的

FPGA電路實(shí)現(xiàn):m序列及應(yīng)用

跨時(shí)鐘域信號的幾種同步方法研究

使用Matlab和Verilog實(shí)現(xiàn)fibonacci序列包括源代碼和testbench

基于FPGA的跨時(shí)鐘域信號處理——MCU

單位寬信號如何跨時(shí)鐘域

跨時(shí)鐘域電路設(shè)計(jì):多位寬數(shù)據(jù)通過FIFO跨時(shí)鐘域

m序列的verilog實(shí)現(xiàn)以及使能信號解決跨時(shí)終域問題

m序列的verilog實(shí)現(xiàn)以及使能信號解決跨時(shí)終域問題

評論