Q.在上一期的討論結(jié)束時,我在ADC和微控制器之間建立通信時遇到了問題。如果您還記得,無論模擬輸入上的電壓如何,微控制器似乎總是在讀取FFF(HEX)的轉(zhuǎn)換結(jié)果。可能是什么原因造成的?

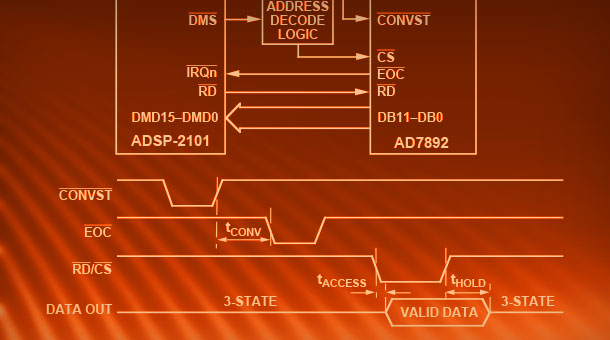

A. 有許多可能與計時相關(guān)的錯誤源。您可以通過將所有定時信號連接到邏輯分析儀或多通道示波器(至少需要三個通道才能同時查看所有信號)來開始解決此問題。您在屏幕上看到的內(nèi)容類似于下圖中的時序圖。首先確保正在生成啟動轉(zhuǎn)換命令 (CONVST)(來自微振蕩器或獨(dú)立振蕩器)。一個常見的錯誤是應(yīng)用極性錯誤的CONVST信號。轉(zhuǎn)換仍會執(zhí)行,但不會在您期望時執(zhí)行。同樣重要的是要記住,CONVST信號通常有一個最小脈沖寬度要求(通常約為50 ns)。來自快速微處理器的標(biāo)準(zhǔn)寫入或讀取脈沖可能無法滿足此要求。如果太短,可以通過插入軟件等待狀態(tài)來延長脈沖寬度。

確保微在讀取周期開始之前等待轉(zhuǎn)換完成。您的軟件應(yīng)該記錄轉(zhuǎn)換所需的時間,或者等待ADC的轉(zhuǎn)換結(jié)束(EOC)指示器在微中生成中斷。確保EOC信號的極性正確,否則ADC將在轉(zhuǎn)換過程中引起中斷。如果微處理器沒有響應(yīng)中斷,則應(yīng)檢查軟件中中斷的配置。

同樣重要的是,當(dāng)串行時鐘線(SCLK)不尋址轉(zhuǎn)換器時,考慮串行時鐘線的狀態(tài)。正如我在前面的討論中提到的,某些DAC和ADC不能在連續(xù)串行時鐘下正常工作。除此之外,某些設(shè)備還要求 SCLK 信號始終處于一種特定狀態(tài)。

問:好的我已經(jīng)發(fā)現(xiàn)并糾正了我的軟件中的一些錯誤,事情似乎正在改善。轉(zhuǎn)換器的數(shù)據(jù)隨著輸入電壓的變化而變化,但轉(zhuǎn)換結(jié)果似乎沒有可識別的格式。

A.同樣,有許多可能的錯誤源。ADC將以直接二進(jìn)制或二進(jìn)制補(bǔ)碼格式輸出其轉(zhuǎn)換結(jié)果(BCD數(shù)據(jù)轉(zhuǎn)換器不再廣泛使用)。檢查您的微處理器是否配置為接受適當(dāng)?shù)母袷健H绻荒軐⑽⑴渲脼橹苯咏邮芏M(jìn)制補(bǔ)碼,您可以通過將數(shù)字與 100 進(jìn)行獨(dú)占或 . . . .00 二進(jìn)制。

通常,串行時鐘的前沿(上升或下降)將使能數(shù)據(jù)從ADC流出并進(jìn)入數(shù)據(jù)總線。然后,后緣將數(shù)據(jù)計時到微處理器中。確保微型和ADC在同一約定下工作,并且滿足所有建立和保持時間。轉(zhuǎn)換結(jié)果恰好是人們期望的一半或兩倍,這是一個跡象,表明數(shù)據(jù)(尤其是MSB)的時鐘在錯誤的邊緣。同樣的問題在串行DAC中表現(xiàn)為輸出電壓是預(yù)期值的一半或兩倍。

驅(qū)動轉(zhuǎn)換器的數(shù)字信號應(yīng)該是干凈的。除了可能對設(shè)備造成長期損壞外,過沖或下沖還會導(dǎo)致轉(zhuǎn)換和通信錯誤。該圖顯示了一個具有大過沖尖峰的信號,該信號驅(qū)動單電源轉(zhuǎn)換器的時鐘輸入。在這種情況下,時鐘輸入驅(qū)動PNP晶體管的基極。按照通常的做法,器件的P型基板在內(nèi)部連接到可用的最負(fù)電位 - 在這種情況下,接地。SCLK線路上地下超過0.3伏的偏移足以開始打開N型基極和P型基板之間的寄生二極管。如果這種情況經(jīng)常發(fā)生,從長遠(yuǎn)來看,可能會導(dǎo)致設(shè)備損壞。

在短期內(nèi),雖然不會造成損壞,但為通常惰性的基板通電會影響器件中的其他晶體管,并可能導(dǎo)致為每個施加的脈沖檢測到多個時鐘脈沖。由此產(chǎn)生的抖動在串行轉(zhuǎn)換器中是一個嚴(yán)重的問題,但在并行轉(zhuǎn)換器中則不是一個問題,因為讀寫周期通常取決于第一個施加的脈沖;后續(xù)脈沖將被忽略。但是,如果在轉(zhuǎn)換過程中存在此類信號,串行和并行轉(zhuǎn)換器的噪聲性能都會受到影響。

該圖顯示了如何輕松減少過沖。一個小電阻串聯(lián)在導(dǎo)致問題的數(shù)字線路上。該電阻將與數(shù)字輸入的寄生電容C(par)結(jié)合,形成一個低通濾波器,該濾波器應(yīng)消除接收信號上的任何振鈴。通常建議使用 50W 電阻,但可能需要進(jìn)行一些實驗。如果數(shù)字輸入的內(nèi)部電容不足,則可能還需要從輸入端增加一個外部電容到地。同樣,實驗是必要的 - 但一個好的起點(diǎn)是大約10 pF。

Q.您提到時鐘過沖會降低轉(zhuǎn)換器的噪聲性能。從接口的角度來看,我還能做些什么來獲得良好的信噪比嗎?

A.由于您的系統(tǒng)在混合信號環(huán)境(即模擬和數(shù)字)中運(yùn)行,因此接地方案至關(guān)重要。您可能知道,因為數(shù)字電路是嘈雜的,因此模擬和數(shù)字接地應(yīng)保持獨(dú)立,僅在一個點(diǎn)連接。這種連接通常在電源上進(jìn)行。事實上,如果模擬和數(shù)字器件由公共電源供電,例如+5 V或+3.3 V單電源系統(tǒng),則別無選擇,只能將接地連接回電源。但是轉(zhuǎn)換器的數(shù)據(jù)手冊中可能有一條指令,用于連接器件上的引腳AGND和DGND!那么,如何避免在接地連接在兩個地方時產(chǎn)生接地環(huán)路呢?

下圖顯示了如何解決這一明顯的困境。關(guān)鍵是轉(zhuǎn)換器引腳上的AGND和DGND標(biāo)簽是指這些引腳所連接的轉(zhuǎn)換器部件。整個設(shè)備應(yīng)被視為模擬設(shè)備。因此,在AGND和DGND引腳連接在一起后,應(yīng)該有一個連接到系統(tǒng)的模擬地。誠然,這將導(dǎo)致轉(zhuǎn)換器的數(shù)字電流在模擬接地層中流動,但這通常比將轉(zhuǎn)換器的DGND引腳暴露在嘈雜的數(shù)字接地層中要小得多。本例還顯示了一個數(shù)字緩沖器(稱為數(shù)字地),用于將轉(zhuǎn)換器的串行數(shù)據(jù)引腳與噪聲串行總線隔離開來。如果轉(zhuǎn)換器與微處理器建立點(diǎn)對點(diǎn)連接,則可能不需要此緩沖器。

該圖還顯示了如何應(yīng)對使用單個電源為混合信號系統(tǒng)供電的日益常見的挑戰(zhàn)。與接地情況一樣,我們將單獨(dú)的電源線(最好是電源層)連接到電路的模擬和數(shù)字部分。我們將轉(zhuǎn)換器的數(shù)字電源引腳視為模擬。但與模擬電源引腳進(jìn)行一些隔離(電感形式)是合適的。請記住,轉(zhuǎn)換器的兩個電源引腳都應(yīng)具有單獨(dú)的去耦電容。數(shù)據(jù)手冊將推薦合適的電容,但一個好的經(jīng)驗法則是0.1 μF。如果空間允許,每個器件還應(yīng)包括一個 10μF 電容器。

Q.我想使用光隔離器在ADC和微控制器之間設(shè)計一個隔離的串行接口。使用這些設(shè)備時,我應(yīng)該注意什么?

A.光隔離器(也稱為光耦合器)可用于創(chuàng)建簡單且廉價的高壓隔離柵。轉(zhuǎn)換器和微型之間存在電流隔離柵也意味著不再需要連接模擬和數(shù)字系統(tǒng)接地。如圖所示,AD7714精密ADC和常用的68HC11微控制器之間的隔離串行接口只需三個光隔離器即可實現(xiàn)。

但是,設(shè)計人員應(yīng)該意識到,即使串行通信以較慢的速度運(yùn)行時,將上升和下降時間相對較慢的光隔離器與CMOS轉(zhuǎn)換器一起使用也會引起問題。

CMOS邏輯輸入設(shè)計為由確定邏輯零或邏輯零驅(qū)動。在這些狀態(tài)下,它們提供和吸收最少量的電流。但是,當(dāng)輸入電壓在邏輯零和邏輯一之間轉(zhuǎn)換(0.8 V至2.0 V)時,柵極將消耗更多的電流。如果所使用的光隔離器的上升和下降時間相對較慢,則在死區(qū)中花費(fèi)的時間過長會導(dǎo)致柵極自熱。這種自發(fā)熱傾向于將邏輯門的閾值電壓向上移動,這可能導(dǎo)致轉(zhuǎn)換器將單個時鐘邊沿解釋為多個時鐘脈沖。為了防止這種閾值抖動,來自光隔離器的線路應(yīng)使用施密特觸發(fā)電路進(jìn)行緩沖,以便為轉(zhuǎn)換器提供快速、鋒利的邊沿。

審核編輯:郭婷

-

CMOS

+關(guān)注

關(guān)注

58文章

5684瀏覽量

235148 -

振蕩器

+關(guān)注

關(guān)注

28文章

3813瀏覽量

138886 -

微處理器

+關(guān)注

關(guān)注

11文章

2247瀏覽量

82322

發(fā)布評論請先 登錄

相關(guān)推薦

數(shù)據(jù)轉(zhuǎn)換器的工程師指南

ADI高級系統(tǒng)應(yīng)用工程師Rob Reeder專訪

模數(shù)轉(zhuǎn)換器應(yīng)用中國工程師百問

串行數(shù)據(jù)轉(zhuǎn)換器接口

Intersil 資深應(yīng)用工程師講述綠色能源趨勢

應(yīng)用工程師咨詢:寬帶A/D轉(zhuǎn)換器前端設(shè)計注意事項II

應(yīng)用工程師咨詢:串行轉(zhuǎn)換器接口

咨詢應(yīng)用工程師:關(guān)于Wire

應(yīng)用工程師咨詢:串行轉(zhuǎn)換器的接口-II

應(yīng)用工程師咨詢:串行轉(zhuǎn)換器的接口-II

評論