Mary McCarthy 和 Anthony Collins

問。 ADI公司未指定其ADG系列開關和多路復用器的帶寬。有原因嗎?

A.ADG系列開關和多路復用器具有非常高的輸入帶寬,達到數百兆赫茲。但是,帶寬規格本身并沒有多大意義,因為在這樣的高頻下,關斷隔離和串擾會明顯降低。例如,在1 MHz時,開關通常具有70 dB的關斷隔離和–85 dB的串擾。關斷隔離和串擾每十倍頻程降低 20 dB。這意味著在10 MHz時,關斷隔離降低到50 dB,串擾增加到–65 dB。在100 MHz時,關斷隔離將降至30 dB,而串擾將增加到–45 dB。因此,僅僅考慮帶寬是不夠的——必須考慮關斷隔離和串擾,以確定應用是否可以承受這些規格在所需高頻下的下降。

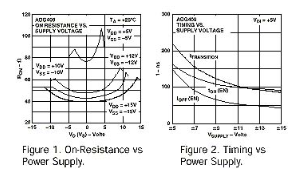

Q. 哪些開關和多路復用器可以使用低于數據手冊中規定的電源工作?

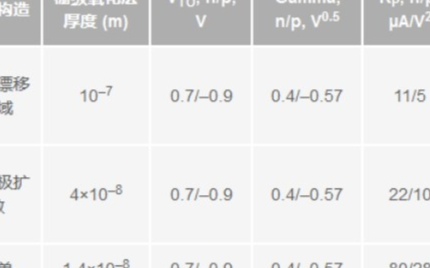

A.所有ADG系列開關和多路復用器均采用低至+5 V或±5 V的電源供電。受電源電壓影響的規格包括時序、導通電阻、電源電流和漏電流。降低電源電壓可降低電源電流和漏電流。例如,ADG411的IS(關閉)和我D(關閉)是 ±20 nA,我D(開)在 +40°C 時為 ±125 nA,采用 ±15V 電源供電。當電源電壓降至±5 V時,IS(關閉)和我D(關閉)降至 ±2.5 nA,而我D(開)在 +5°C 時降至 ±125 nA。 電源電流,IDD我黨衛軍和我L,采用 ±5V 電源時 +125°C 時最大 15 mA。使用 ±5V 電源時,電源電流降至 1 μA(最大值)。導通電阻和時序隨著電源的減少而增加。下圖顯示了ADG408的時序和導通電阻如何隨電源電壓的變化而變化。

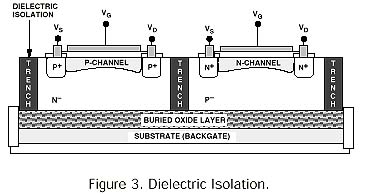

Q. 一些ADG系列開關采用DI工藝制造。這是什么?

A.DI是介電隔離的縮寫。在DI工藝中,在每個CMOS開關的NMOS和PMOS晶體管之間放置一個絕緣層(溝槽)。消除了標準開關中晶體管之間的寄生結,從而形成了完全防閂鎖的開關。在結隔離(不使用溝槽)中,PMOS和NMOS晶體管的N和P孔形成一個二極管,該二極管在正常工作時反向柯林斯偏置。然而,在過壓或斷電條件下,當模擬輸入超過電源時,二極管正向偏置,與兩個晶體管形成類似可控硅整流器(SCR)的電路,導致電流被顯著放大,最終導致閂鎖。該二極管在介質隔離開關中不存在,因此部件防閂鎖。

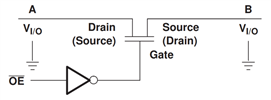

Q. 故障保護多路復用器和通道保護器如何工作?

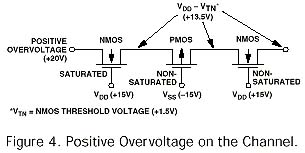

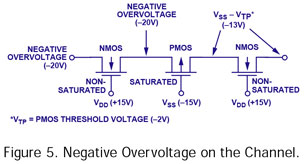

A.故障保護多路復用器或通道保護器的通道由兩個NMOS和兩個PMOS晶體管組成。其中一個PMOS晶體管不在直接信號路徑中,而是用于將第二個PMOS的源極連接到其后柵。這具有降低閾值電壓的效果,從而增加了正常工作的輸入信號范圍。出于同樣的原因,連接 NMOS 設備的源和后門。在正常工作期間,故障保護器件作為標準多路復用器運行。當通道輸入發生故障情況時,這意味著輸入已超過由電源軌電壓設置的某個閾值電壓。閾值電壓與電源軌的關系如下:對于正過壓,閾值電壓由下式給出在DD–在田納西哪里在田納西是NMOS晶體管的閾值電壓(通常為1.5 V)。對于負過壓,閾值電壓由下式給出在黨衛軍–在胡志明市哪里在胡志明市是PMOS器件的閾值電壓(通常為2 V)。當輸入電壓超過這些閾值電壓時,通道上沒有負載,通道的輸出被箝位在閾值電壓。

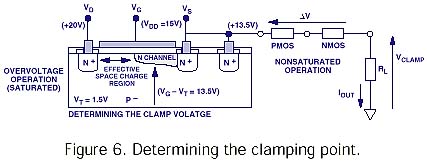

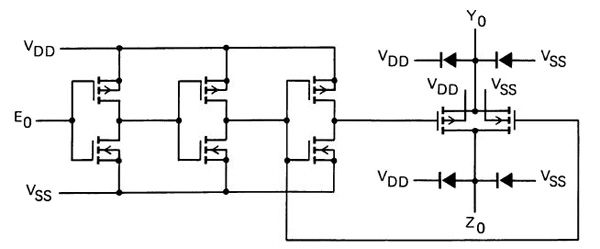

Q. 當存在過電壓時,器件如何工作?

A.接下來的兩個圖顯示了信號路徑晶體管在過壓條件下的工作條件。這一個演示了當對通道施加正過壓時,N、P和N系列晶體管如何工作。第一個NMOS晶體管進入飽和模式,因為其漏極上的電壓超過(在DD–在田納西).NMOS 設備源處的電位等于 (在DD–在田納西).其他 MOS 器件處于非飽和工作模式。

當對通道施加負過壓時,當漏極電壓超過(在黨衛軍–在胡志明市).與正過壓一樣,其他MOS器件也是非飽和的。

Q. 負載如何影響鉗位電壓?

A.當通道加載時,通道輸出將箝位在閾值之間的電壓值。例如,負載為 1 kΩ,V 時DD= 15 V,正過壓,輸出將箝位在DD–在田納西– ΔV,其中 ΔV 是由于非飽和 MOS 器件通道上的 IR 壓降造成的。在下面顯示的示例中,鉗位NMOS輸出端的電壓為13.5 V。其余兩個MOS器件的導通電阻通常為100 Ω。因此,電流為13.5 V/(1 kΩ + 100 Ω) = 12.27 mA。這會在NMOS和PMOS兩端產生1.2 V的壓降,從而產生12.3 V的鉗位電壓。故障條件下的電流由輸出上的負載決定,即在鉗/RL.

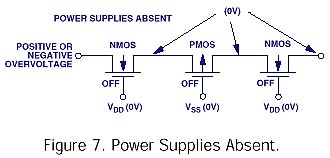

問。 故障保護多路復用器和通道保護器在電源缺電時是否正常工作。

A.是的。當電源軌關閉或暫時斷開時,這些器件仍能正常工作。當 VDD和 V黨衛軍等于0 V,所有晶體管都關閉,如圖所示,電流限制在亞納安級。

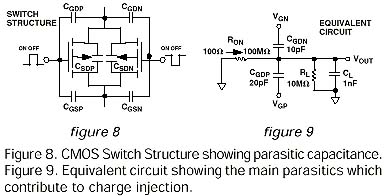

Q. 什么是“電荷注入”?

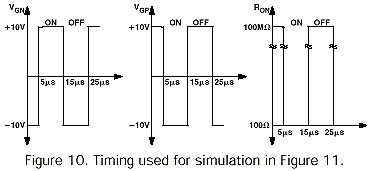

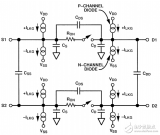

A.模擬開關和多路復用器中的電荷注入是由構成模擬開關的NMOS和PMOS晶體管相關的雜散電容引起的電平變化。下圖模擬了模擬開關的結構以及與這種實現相關的雜散電容。該結構基本上由并聯的NMOS和PMOS器件組成。這種布置為雙極性輸入信號產生熟悉的“浴缸”電阻曲線。等效電路顯示了影響電荷注入效應的主要寄生電容C粵港網(NMOS 柵極到排水管)和 C國內生產總值(PMOS柵極到排水)。與PMOS器件相關的柵極漏極電容約為NMOS器件的兩倍,因為要使兩個器件具有相同的導通電阻,PMOS器件的面積約為NMOS的兩倍。因此,相關雜散電容約為市場上典型開關的NMOS器件的兩倍。

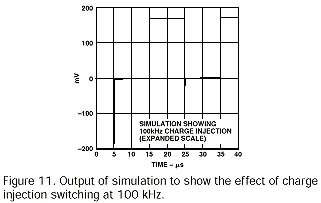

當開關打開時,正電壓施加到NMOS的柵極,負電壓施加到PMOS的柵極。由于雜散柵極-漏極電容不匹配,因此向漏極注入不等量的正電荷和負電荷。結果是從開關輸出端去除電荷,表現為負向電壓尖峰。由于模擬開關現在導通,因此負電荷通過開關的導通電阻(100 Ω)快速放電。這可以在5 μs的仿真圖中看到。然后,當開關關閉時,向NMOS的柵極施加負電壓,在PMOS的柵極施加正電壓。結果是電荷添加到開關的輸出端。由于模擬開關現在處于關閉狀態,因此注入正電荷的放電路徑為高阻抗(100 MΩ)。結果是負載電容存儲此電荷,直到開關再次打開。仿真圖清楚地表明了這一點,C上的電壓L(由于電荷注入)在170 mV保持恒定,直到開關在25 μs再次導通。此時,將等量的負電荷注入輸出端,從而降低C上的電壓L至 0 V。在35 μs時,開關再次打開,該過程以這種循環方式繼續。

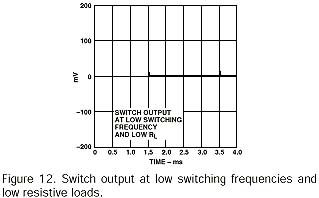

在較低的開關頻率和負載電阻下,開關輸出將包含正毛刺和負毛刺,因為注入的電荷在下一次開關轉換之前泄漏。

Q. 如何提高模擬開關的電荷注入性能?

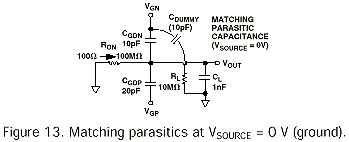

A.如上所述,電荷注入效應是由NMOS和PMOS器件的寄生柵極-漏極電容不匹配引起的。因此,如果這些寄生效應可以匹配,那么電荷注入效應將很小。這正是ADI公司CMOS開關和多路復用器所做的。通過在NMOS器件的柵極和漏極之間引入一個虛擬電容來實現匹配。

不幸的是,匹配僅在一組特定條件下完成,即當兩個器件的源上的電壓為0 V時。其原因是寄生電容C粵港網和 C國內生產總值,不是恒定的;它們隨源電壓而變化。當NMOS和PMOS的源電壓變化時,它們的溝道深度會發生變化,并且隨之而來的是C粵港網和 C國內生產總值.由于在 V 處的這種匹配源= 0 V 對于 V 的其他值,電荷注入效應將很明顯源.

注意:電荷注入通常在數據手冊中指定在這些匹配條件下,即V源= 0 V。在這些條件下,大多數開關的電荷注入通常相當好,最大值為2至3 pC。但是,對于V的其他值,電荷注入將增加源,在一定程度上取決于各個交換機。許多數據手冊將顯示電荷注入與源電壓的函數關系圖。

問:如何在應用程序中最大程度地減少這些影響?

A.電荷注入的影響是由于注入固定量的電荷而對開關輸出的電壓毛刺。毛刺幅度是開關輸出負載電容以及開關開啟和關斷時間的函數。負載電容越大,輸出端的電壓毛刺越小,即Q = C × V,或V = Q/C,Q是固定的。當然,可能并不總是能夠增加負載電容,因為它會降低通道的帶寬。然而,對于音頻應用,增加負載電容是減少那些不必要的“爆裂”和“咔嗒聲”的有效方法。

選擇導通和關斷時間較慢的開關也是降低開關輸出端毛刺幅度的有效方法。相同的固定量電荷在較長的時間段內注入,因此具有更長的泄漏時間段。結果是毛刺更寬,但幅度大大降低。這種技術在某些音頻開關產品中得到了非常有效的應用,例如SSM-2402 / SSM-2412,其中導通時間設計為10 ms量級。

值得一提的另一點是,電荷注入性能與開關的導通電阻直接相關。一般來說,R 越低上,電荷注入性能越差。其原因純粹是由于相關的幾何形狀,因為 R上通過增加 NMOS 和 PMOS 器件的面積來減少,從而增加 CGDN 和 C國內生產總值.所以權衡 R上在許多應用中,減少電荷注入也可能是一種選擇。

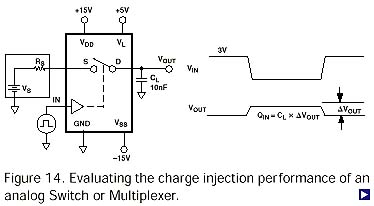

Q. 如何評估模擬開關或多路復用器的電荷注入性能?

A.評估開關電荷注入性能的最有效方法是使用類似于如下所示的設置。通過以相對較高的頻率(<10 kHz)打開和關閉開關,并觀察示波器上的開關輸出(使用高阻抗探頭),將觀察到類似于圖11所示的跡線。注入負載的電荷量由下式給出ΔV外× CL.哪里ΔV外是輸出脈沖幅度。

審核編輯:郭婷

-

晶體管

+關注

關注

77文章

9635瀏覽量

137853 -

MOS

+關注

關注

32文章

1247瀏覽量

93482 -

多路復用器

+關注

關注

9文章

869瀏覽量

65283

發布評論請先 登錄

相關推薦

PXI高密度多路復用器應用于飛機雷電防護試驗

組合邏輯基礎之多路復用器設計

模擬開關和多路復用器的基礎參數

模擬開關和多路復用器

基于模擬開關和多路復用器的應用基礎知識

基礎教程:模擬開關和多路復用器基礎知識

模擬開關和多路復用器基礎參數簡介

應用工程師咨詢:開關和多路復用器

應用工程師咨詢:開關和多路復用器

評論