ADI公司的兩款CMOS高速16位過采樣A/D轉換器,用于在需要低功耗、小尺寸和低成本單芯片解決方案的應用中處理具有寬動態范圍的寬帶信號。

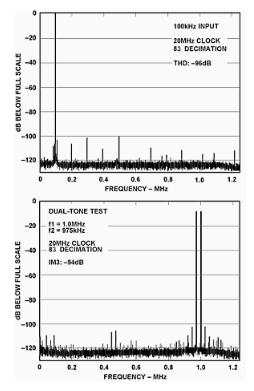

AD9260在20倍過采樣模式下使用8 MSPS時鐘(圖1),能夠以16.2 MHz字速率輸出5位信號,提供1.01 MHz信號通帶、0.004 dB紋波和100 dB SFDR(無雜散動態范圍)。AD7723具有19.2 MHz時鐘,采用16倍過采樣,能夠以16.460 MHz輸出字速率為1 kHz輸入提供2位性能。在要求較低的應用中,為了節省電池容量,AD9260的功耗要求可以從585 mW降至150 mW;AD7723的500 mW功率可以減半。AD7723還具有200 μW待機模式。該表提供了一些額外的比較點。

圖1.AD9260 SFDR:單音(100 dB)和雙音(95 dB)性能。

兩個器件都有內部基準;AD7723提供2.5 V電壓,AD9260的基準電壓源具有1.0和2.5 V模式。它們采用44引腳QFP封裝,AD9260采用MQFP封裝,AD7723采用PQFP封裝。兩款器件均采用+5 V模擬和數字電源供電,但AD9260的數字電源額定工作電壓為+3 V,以實現功耗經濟性和最小噪聲。評估板適用于每種類型。

|

特征 |

AD9260 |

AD7723 |

|

分辨率 |

16 | 16 |

|

采樣率,MSPS |

20 | 19.2 |

|

輸出數據速率,MSPS @ OSR |

2.5 @ 8× |

1.2 @ 16× |

|

過采樣率選擇 |

1×, 2×, 4×, 8× |

16×、32× |

|

濾波特性 |

LP |

LP, BP |

|

功耗,mW (最大值) |

630 | 500 |

|

功耗降低,毫瓦 |

至 150 |

50%,200 μW |

|

內部基準,V |

1,2.5 |

2.5 |

|

SFDR,dB(低頻信號) |

100 | 90 |

|

信噪比,分貝,1.2 MHz 直通量 |

88.5 類型 |

83 分 |

|

44 引腳封裝 |

MQFP |

PQFP |

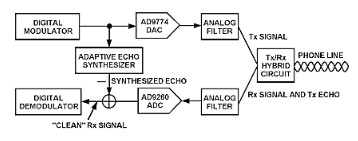

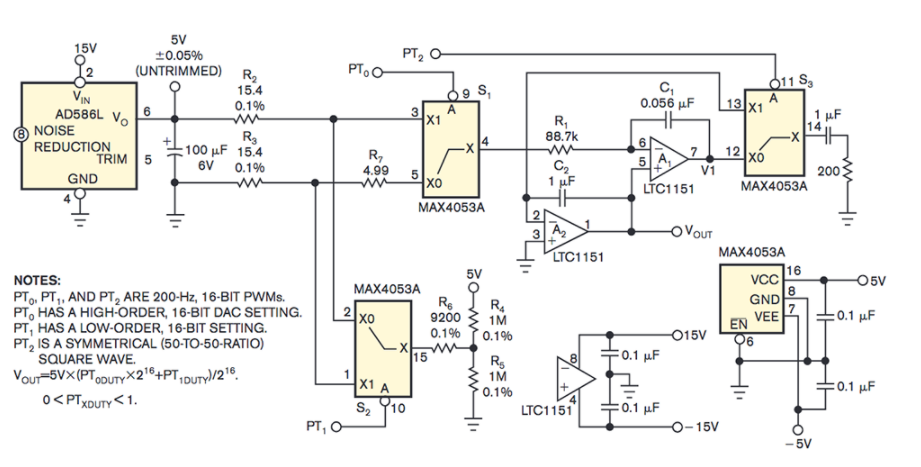

典型應用:寬帶寬和高采樣率下的16位性能在通信設備中特別有用。一個關鍵的例子是用于全雙工通信的調制解調器中的回聲消除,其中共享同一通道以同時發送和接收信號(圖 2)。在這種設備中,強發射信號(及其回波)和弱接收信號在時間或頻率上可能非常接近。為了使用DSP技術對信號進行分類,必須首先將信號轉換為數字信號,而不會損失噪聲中的小分量,也不會因失真大分量而產生雜散分量(雜散)。這就要求采用具有高SFDR、低失真(諧波和互調)和低量化噪聲的寬動態范圍器件。

圖2.全雙工數字錯誤消除調制解調器。

AD9260已成功針對有線和無線通信應用進行了評估,例如寬帶蜂窩基站、回聲消除ADSL調制解調器、單對HDSL調制解調器、導航系統和寬帶CDMA基站。這兩款器件的高速、動態范圍、低功耗、高集成度和低價格使其可用于聲納、無線電、儀器儀表、測試設備以及其他信號捕獲和分析應用。當吞吐速率合適時,AD7723的低成本和特殊特性可用于需要待機條件、需要選擇串行或并行操作和/或需要16或更高過采樣比的帶通應用。

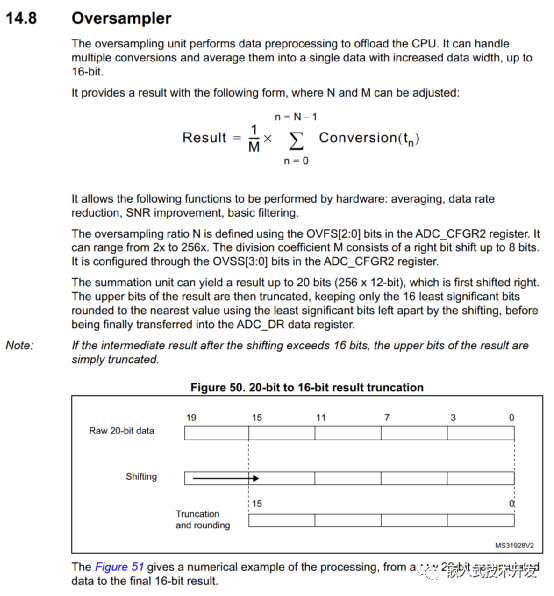

體系結構注意事項

傳統上,Σ-Δ A/D轉換器以低成本為工業、音頻和低頻通信應用提供高分辨率,但分辨率和速度之間的權衡通常將帶寬限制在200 kHz以下。二階單位比特調制器可以滿足工業市場的高分辨率要求,但代價是過采樣比(OSR)大,并且固有地不適合高輸出數據速率(ODR)應用。

單環路調制器通常通過增加環路中的積分階數來增加帶寬。例如,使用七階調制器的AD7722在7 kHz輸出數據速率下具有90 dB SNR,時鐘頻率為195.12 MHz。通過提高此類轉換器的ODR速率來提高帶寬將很困難,因為這需要更昂貴的制造工藝和能夠建立到所需精度的耗電積分放大器。因此,出于實際考慮,單環路單位比特架構的輸出數據速率為5-100 kHz。

為了擴展分辨率/帶寬邊界,需要新的架構。雖然細節超出了本次簡要討論的范圍,但值得注意的是,AD9260涉足新領域,以實現最先進的巡回賽解決方案;AD7723成功實現了先進的級聯設計方法。我們的大多數Σ-Δ型ADC中使用的單比特DAC雖然保證了出色的失真,但會產生大量量化噪聲,從而降低SNR。通過在調制器中使用多位DAC,并采用隨機混頻技術對DAC的非線性進行隨機化,AD9260實現了高分辨率和良好的失真。為了進一步降低量化噪聲的影響,在AD9260和AD7723中,首先測量DAC增加的量化噪聲,然后以數字方式減去。

特點和性能

AD9260(圖3)通過將Σ-Δ技術與高速流水線模數轉換器相結合,以適中的8×過采樣比實現了高動態范圍和極寬輸入信號帶寬。差分模擬輸入被饋入采用2位閃存量化器和5位反饋的二階Σ-Δ調制器。同時,5位流水線A/D轉換器可以更精確地量化閃存轉換器的輸入。環路架構提供相當于具有 12 位量化器和 12 位反饋的穩定二階環路,不受空閑音調和其他有時與高階單比特 Σ-Δ 調制器相關的特性的影響。

圖3.AD9260原理框圖

調制器輸出饋入三級抽取濾波器,MODE控制允許輸出旁路任何或所有級,提供時鐘速率(1×或抽取2×、4×或8×的輸出選擇。抽取濾波器的阻帶抑制1.25至18.75 MHz之間的頻率,大大放寬了模擬輸入的抗混疊要求。片內提供帶緩沖器的基準電壓源。在2.5 V模式(最佳噪聲和失真)下,可以處理4 V p-p滿量程差分輸入。在 1V 模式下,量程為 1.6 V 峰峰值。也可通過外部電阻分壓器提供任意可編程值。偏置調整使功耗與時鐘速率成比例,從而在時鐘速率從20 MSPS降至5 MSPS和585至150 mW時降低功耗(和性能)。

AD7723(圖4)使用多個級聯一階和二階Σ-Δ調制器,每個調制器由一個或多個積分器、一個比較器和一個1位DAC組成。第一個調制器執行實際的模數轉換,隨后的調制器及其校正邏輯依次消除前一個調制器貢獻的量化噪聲,同時通過向上移動自己的量化噪聲來降低自身的本底噪聲。為了滿足AD7723的性能要求,采用了5階噪聲整形,導致輸出僅包含輸入信號和調制器5的4階整形量化噪聲。

圖4.AD7723原理框圖

AD7723的時鐘頻率最高可達19.2 MHz。5級FIR抽取濾波器用于降低輸出數據速率并消除帶外量化噪聲。ADC輸出可從第4個或第5個濾波器獲取。來自第四個濾波器的數據的輸出數據速率(ODR)為1.2 MHz,SINAD為85 dB,而來自第五個濾波器的數據的ODR為5 kHz,但SINAD更高,為600 dB。第88個濾波器也可以配置為高通濾波器,使AD5可用作帶通ADC。

AD7723提供靈活的串行或并行接口、高過采樣率(OSR),以最大限度地降低抗混疊濾波器的復雜性,并接受單極性或雙極性輸入,以便與輸入驅動電路進行簡單接口。工作溫度范圍為 -40 至 +85° C。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8627瀏覽量

146871 -

濾波器

+關注

關注

160文章

7728瀏覽量

177685 -

dac

+關注

關注

43文章

2271瀏覽量

190840

發布評論請先 登錄

相關推薦

ADC的噪聲、ENOB及有效分辨率

如何在Δ∑ADC上達到20位分辨率

請問有采樣率250MHz左右、分辨率為12位,管腳兼容8位分辨率的adc嗎?

通過過采樣提高SOC單片機片內A_D分辨率

AD9260:2.5 MHz輸出字率下16位分辨率的高速過采樣CMOS ADC數據表

過采樣ADC,實現16位分辨率

過采樣ADC,實現16位分辨率

評論