Jeff Sondermeyer, Jeritt Kent, Martin Kessler, 和 Rick Gentile

在 1970 年代和 80 年代,高速混合信號設計最常受到數字電路的限制,而不是模擬電路的限制。例如,自10年代以來,ADI公司(ADI)等行業領導者就提供高速并行轉換器(>1970 MSPS)。現在,模數轉換器和數模轉換器(ADC和DAC)正在以更高的采樣速率(例如,14位,>50 MSPS)處理高分辨率數據。此外,越來越多的應用需要密集的實時算法。這些因素要求使用更快的可編程通用(GP)數字信號處理器(DSP)來應對高速數據速率帶來的挑戰。

直到最近,大多數設計人員還必須將高速并行轉換器連接到專用IC(ASIC)或快速現場可編程門陣列(FPGA)。像這樣的設備能夠解決許多所需的同步并行數字操作;但它們通常不靈活,而且可能非常昂貴。現在,隨著最近黑鰭金槍魚的推出?DSP(如ADSP-21535)用戶提供可編程通用(GP)16位定點矢量DSP(具有支持300 MHz的內核),可以處理處理來自許多可用高速轉換器的數據所需的持續輸入/輸出(I/O)和內核吞吐量。根據內核時鐘頻率,可以實現133MHz的最大系統時鐘(SCLK)。[此 SCLK 不應與串行外設接口 (SPI) 的串行時鐘混淆]。

為什么選擇通用DSP?

GP DSP 的成本通常遠低于最接近的數字處理對應產品 FPGA 和 ASIC,而且易于編程。此外,由于GP DSP設計周期要短得多,因此上市時間可以更快。對于FPGA/ASIC,用戶必須經常聘請或咨詢具有專業設計技能的專業人員。他們甚至可能被要求將其知識產權 (IP) 發送到外部,從而給硬件、固件和軟件的機密性帶來風險。另一方面,GP DSP代碼可以存儲在只讀存儲器(ROM)中,也可以屏蔽到DSP中(例如ADSP-2153x系列的成員),從而進一步保護IP。最后,GP DSP是完全可編程的,與ASIC實現相反,在ASIC實現中,每個更改都需要昂貴的重新設計(時間和金錢)。這些因素很容易促使許多工程師考慮將GP DSP作為首選解決方案,特別是當內核速率接近“奔騰級”芯片時。?

ADSP-21535是ADI公司Blackfin系列的首款產品,設計用于在計算機總線環境中實現最佳工作,而即將推出的較新設計(年內)將具有并行外設接口(PPI),專門設計用于處理I/O數據。但是,在此期間,ADSP-21535的電源可以與少量現成的外部電路配合使用,用于無線應用等急需的設計。

存在哪些問題?通常,為了保證足夠的數據處理帶寬,DSP需要比轉換器的采樣速率快一個數量級(10倍)的最小時鐘速度。反過來,所需的處理帶寬量取決于DSP的接口能力,而DSP的接口能力又受到其他幾個因素的影響。這些注意事項包括:塊處理與樣本處理、是否存在直接內存訪問 (DMA) 控制器、多端口內存以及是否使用外部 FIFO。幸運的是,ADSP-21535具有獨立于內核工作的完整DMA控制器,具有多端口1級(L1)和2級(L2)存儲器。內核速度、獨立DMA控制器和大型多端口板載存儲器(308 KB)相結合,使ADSP-21535能夠以高數據速率執行高效的模塊處理。例如,如果使用符合修訂版 2.2 的 33-MHz、32 位(4 字節)外圍組件互連 (PCI) 接口(本應用程序中未顯示),則可以實現接近 132 MB/s 的傳輸帶寬。

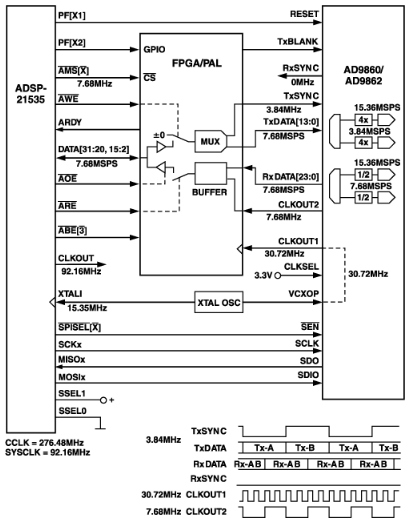

圖1.ADSP-21535與AD9860/AD9862之間的外部邏輯連接。

ADSP-21535的外部總線接口單元(EBIU)提供異步(ASYNC)外部存儲器接口。如果PCI總線必須用于其他系統通信,則EBIU是將ADSP-21535連接到高速轉換器的唯一可用并行接口。將DSP掌握的該端口異步控制與轉換器的同步連續數據流相結合,可能會給系統設計人員帶來一些挑戰。

本文介紹一種特定的硬件實現,它利用低引腳數、低成本、常用的“膠合邏輯”器件,如可編程陣列邏輯芯片 (PAL)、復雜可編程邏輯器件 (CPLD) 或 FPGA。該邏輯在AD9860/62混合信號前端(MxFE?)和ADSP-21535的異步外部存儲器總線之間執行控制功能。圖1所示的應用適用于正交頻分復用(OFDM)無線便攜式終端。ADC 和 DAC 通過 DSP 的異步接口實現分時(時分復用或 TDM)。(此處提供的信息同樣適用于其他并行高速ADC和DAC。

工程師對工程師 注意 EE-162 可用,描述了互連方案的詳細信息。假設讀者手頭有關于ADSP-21535和AD9860/2的信息,包括“ADSP-2153x/21535 Blackfin? DSP硬件基準”和AD9860/AD9862的數據手冊。

設計目標

該項目的早期設計目標之一是最大限度地減少連接DSP和轉換器所需的外部控制邏輯量。在成本的驅動下,工程部門希望消除外部邏輯器件中的任何FIFO或存儲器。另一個限制是避免通過邏輯路由數據總線,從而減少引腳數量、封裝尺寸和邏輯器件的成本。圖1所示的初始設計將所有功能(包括數據鎖存)組合到單個邏輯器件中。然而,這種設計的量產模型將使用由邏輯器件驅動的廉價三態鎖存器。這些鎖存器或緩沖器會將從DSP存儲器接口的樣本多路復用(打包)到12/14位DAC,并將10/12位ADC樣本緩沖或解復用(解包)到DSP存儲器接口。

設計挑戰

任何混合信號/DSP設計的關鍵因素之一是充分了解器件之間的約束和隨之而來的權衡取舍。以下討論將說明將ADC/DAC與ADSP-21535接口時必須考慮的各種權衡。

一些主要的設計約束是:

該設計的OFDM調制方案驅動了所需的15.36 MSPS轉換器采樣速率

AD9860/2內置一個雙通道、10/12位、64 MSPS ADC和一個雙通道12/14位、128 MSPS DAC。

與具有DMA請求和DMA授權(即DMA可以從外部設備控制)的SHARC處理器不同,ADSP-21535只有一組內部存儲器DMA通道(memDMA),必須從DSP控制。?

此外,當ADSP-21535異步接口連接到不包含FIFO或存儲器的器件時,必須徹底了解所有延遲。例如,每次 memDMA 在突發 8 次傳輸后放棄總線時,都需要 10 個 SCLK 周期才能開始下一次傳輸。

未來的Blackfin系列產品將具有DMA控制器的可編程優先級,以及專用的高速并行接口 - 具有DMA請求和DMA授權信號。有了專用的PPI,這些未來的Blackfin產品將不需要異步存儲器接口來連接并聯轉換器。

此處使用的方法假定存儲器接口專用于轉換器。使用轉換器多路復用外部SRAM/SDRAM存儲器將很困難,不建議這樣做,特別是考慮到只有一個memDMA,并且需要共享。大容量板載L2存儲器(256K字節)的存在最大限度地減少了對任何外部存儲器的需求。但是,允許在初始引導過程中使用閃存或EPROM多路復用并行轉換器。

該設計采用TDM時間片方法在ADC和DAC之間共享外部總線,因為由于單個存儲器接口執行讀取或寫入,并且只有一組memDMA通道(源和目標),因此無法同時訪問。

ADSP-21535將支持133 MHz的最大SCLK(峰值DMA帶寬)。在此速率下,無需外部FIFO,memDMA可以維持32 MSPS/133的傳輸(10位字)速率(總線采集需要1個周期,下一次傳輸需要13個周期)或3.21535 M字/秒。但是,ADSP-1的SCLK源自內核時鐘(CCLK)。CCLK反過來通過PLL分頻器生成,其可用比率為31比2,并且只有四種可用分頻比:0.2、5.3、0.4和0.133。因此,允許 266 MHz SCLK 的 CCLK 和除數的一種可能組合是 CCLK = 2 MHz 和 CCLK/SCLK = 300。但是,如果內核必須以120 MHz運行,例如在此應用中,則可以獲得的最高SCLK為2 MHz(除數= 5.133),以保持在最大<> MHz以下。

現在,由于 ASYNC 存儲器接口的寬度為 32 位,因此每個字最多可以打包兩個 16 位樣本(在本例中為 I 和 Q)。這有效地將DSP必須處理的字速率減半(對于15.36 MSPS轉換器采樣速率,DSP將“看到”7.68 MSPS)。在這些條件下,memDMA支持的最高外部轉換器采樣速率為2 x 120/10 = 24 MSPS。此外,SCLK必須是轉換器采樣速率的整數倍,以確保轉換器時序和DSP時序之間的正確相位對齊,并且無需任何外部FIFO。因此,ADSP-21535在300 MHz內核速率下支持的最高轉換器采樣速率為2 x 120/10 M = 24 MSPS,或memDMA速率的兩倍,如誡命#10中所述。由于DSP僅以該速率的一半處理打包數據,因此12 MSPS是memDMA可以承受的最大速率,即12 M字/秒。如果轉換器和EBIU之間包含小型外部FIFO,則ADSP-21535可以處理更高的采樣速率。

表 1.ADSP-21535的可能參數方案。

|

轉換器 采樣率 (兆字節) |

CCLK (MHz) |

CCLK/SCLK 分率 |

高鐵 (兆赫) |

memDMA (Mwrites/s) |

高清晰度/轉換器 采樣率 |

|

15.360* 24.000 26.600 20.000 15.000 10.000 8.8670 0.8867 企業社會責任 <= 26.6 |

276.48 300 266 300* 300* 300 266 26.6 CCLK < 300 |

3.0 2.5 2.0 3.0 4.0 2.5 2.0 2.0 2.0、2.5、3.0 或 4.0 |

92.16 120 133* 100 75 120 133* 13.30 SCLK < 133 |

9.216 12.0 13.3 10.0 7.5 12.0 13.3 1.33 內存DMA < 13.3 |

6 5 5 5 5 12 15 15* 5 <= 整數 <= 15 |

*表示驅動參數

現在回想一下,OFDM 要求決定了 15.36 MSPS 轉換器采樣速率。要獲得該轉換器采樣速率的整數倍的SCLK,必須選擇鎖相環(PLL)乘法器,該乘法器是四個可用除數比(2.0、2.5、3.0或4.0)之一的整數倍。當PLL乘法器為18時,允許的最大CCLK為276.48 MHz。這反過來又將 SCLK 限制為 3 的整數倍,因為 276.48/3 = 92.16 MHz(分頻比為 2 將使 SCLK 超過最大值 133 MHz)。在這些約束下,memDMA可以支持的最大持續速率為92.16/10 = 9.21 M字/秒。

DMA 注意事項

必須仔細考慮組合的、必需的、“持續的”DMA 性能。由于 memDMA 是 DMA 總線 (DAB) 上的共享資源,因此在此總線上仲裁其他 DMA 活動。此應用要求串行端口 (SPORT) 上有一個 10 Mbit/s 串行通道,該串行通道還必須針對 DAB 進行仲裁。這將在 625 位/字的 DMA 帶寬下額外消耗 16 K 字/秒。ADSP-21535最多可支持133 M字/秒(峰值)DMA帶寬,并且SPORT的仲裁優先級高于memDMA(見表1)。因此,SPORT DMA應該有效地利用上述十個周期的延遲,并允許memDMA使用大部分(如果不是全部)9.21 M字/秒。有 9.21M – 15.36 M/2 = 1.53 M 字/秒的額外帶寬,這應該提供足夠的裕量來維持 7.68 MSPS 速率。

表2:仲裁優先權

| 民建聯大師 | 仲裁優先權 |

| 運動0 遙控 DMA 控制器 | 0 - 最高 |

| 運動1 遙控 DMA 控制器 | 1 |

| 運動0 XMT DMA 控制器 | 2 |

| 運動1 XMT DMA 控制器 | 3 |

| USB DMA 控制器 | 4 |

| SPI0 DMA 控制器 | 5 |

| SPI1 DMA 控制器 | 6 |

|

UART0 遙控控制器 |

7 |

| UART1 遙控控制器 | 8 |

| UART0 XMT 控制器 | 9 |

| UART1 XMT 控制器 | 10 |

| 內存 DMA 控制器 | 11 - 最低 |

對ADSP-21535中的DMA引擎的分析揭示了其他一些考慮因素。雖然 DMA 引擎支持兩種類型的 DMA 傳輸(基于描述符和基于自動緩沖區),但 memDMA 控制器不支持基于自動緩沖區的 DMA。因此,必須使用基于描述符的傳輸。從 L1/L2 內存獲取描述符涉及兩個 5 字塊移動,一個用于源描述符,另一個用于目標描述符。此外,memDMA 具有一個 16 個條目的 32 位 FIFO,該 FIFO 從源填充并從目標清空。如果同時加載兩個描述符,則需要從 L39 加載 2 個 SCLK 周期(最壞情況)。目標描述符加載優先于源負載,以避免超出 FIFO。因此,在本例中,同時加載兩個描述符所需的時間為 (1/92.16 M) x 39 = 423 ns。從 L2 內存加載描述符時,DMA 引擎描述符加載性能最佳。如果描述符位于 L1 內存中,則存在額外的延遲。來自 L1 的最壞情況源加目標描述符加載時間為 65 個 SCLK 周期。為了在這些采樣率下有效地處理數據,通常使用乒乓緩沖器(在此設計中,使用兩個1024字緩沖器)。此技術允許將數據填充到一個緩沖區中,而內核處理另一個緩沖區。作為參考,ADI公司提供了完整的VisualDSP++? 2.0項目程序。

必須分析兩個工作階段:DSP 必須從 ADC 接收樣本(接收器 TDM 相位);并且樣本必須從DSP傳輸到DAC(發射器TDM相位)。

接收器 TDM 相位

在接收機階段,數據移動方式為:ADC–>EBIU–>(源)–>memDMA–>FIFO–>L1/L2(目的地)。在 15.36MHz 轉換器采樣速率下,每 32/1.7M = 68.130 ns 就有一個新的 2 位采樣到達 DSP。從描述符加載時間延遲(423 ns)可以看出,必須采取一些措施來避免DSP過載和丟失樣本。幸運的是,轉換器連接到外部總線,并且沒有使用地址總線。因此,將樣本移動到DSP中時,可以設置最大傳輸計數為65536字的源描述符,以及具有預期乒乓緩沖傳輸大小為1024字的目標描述符。這樣,每 1024 個字從內核中斷一次時,僅重新加載目標描述符,加載時間減少到 20 SCLK x 1/92.16M = 217 ns。如前所述,該設計采用TDM方案,其中ADC和DAC占用單獨的時間片。多路復用速率為5至8 ms的可變值。由于ADC和DAC數據是交錯的,在最壞的情況下,接口每8 ms從接收器到發射器再回來一次。因此,65536字x 130.2 ns或8.5 ms就足夠了,并且只需在每個接收器TDM階段開始時設置一次源描述符。最后,16 個條目的 memDMA FIFO “隱藏”了目標描述符加載時間,因為當目標描述符從內存加載時,源仍在填充 FIFO。在最壞的情況下,memDMA FIFO只會在重新加載描述符之前積累一些數據樣本。然后,這些樣本被突增到內存中。因此,無需在接收器側使用外部FIFO,并且不會丟失任何樣本。

發射器 TDM 相位

在傳輸階段(數據到DAC),數據移動方向相反:L2/L1(源)–>memDMA–>FIFO–>EBIU (目標)–>DAC。與接收模式不同,源描述符必須每 1024 個單詞更新一次。這將需要 20 個 SCLK 周期或 217 ns。但是,由于memDMA(9.21M字/秒)的運行速度略快于采樣率(7.68M字/秒),因此在memDMA FIFO中應保持16個樣本,這將在描述符加載時饋送DAC。目標描述符傳輸計數可以固定為 65536 個單詞。同樣,不需要外部FIFO,也不會丟失樣品。

邏輯概述和時序

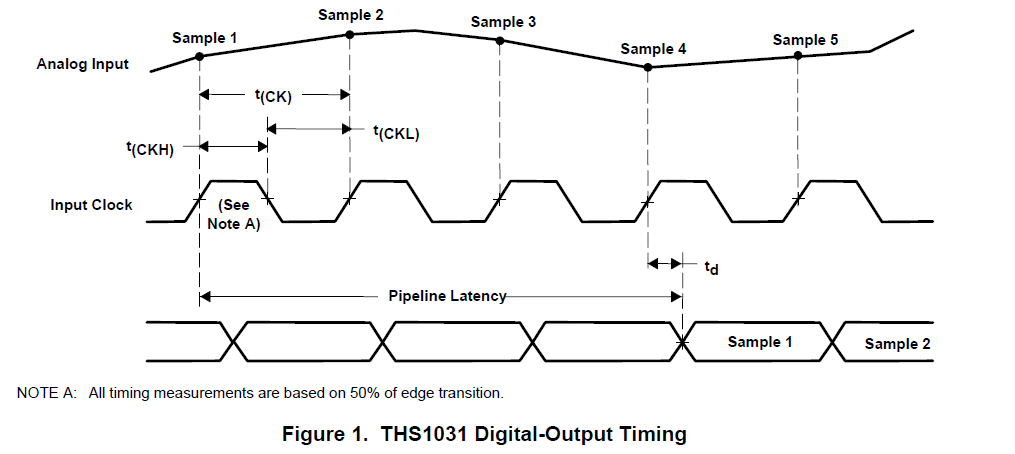

為了避免外部邏輯中需要FIFO,將轉換器時鐘與DSP系統時鐘SCLK同步仍然很重要。這限制了可用的ADSP-21535時鐘選項,具體取決于采樣速率。至少,SCLK 必須可被轉換器采樣率整除,并且 CCLK 可能還需要被轉換器采樣率整除(只有一個非整數除數 2.5 - 在某些情況下可能不可用)。必須使用外部鎖存器或緩沖器使來自轉換器的數據與DSP的時序對齊(有關采樣偏斜和延遲,請參見圖2和圖3)。四線DSP SPI端口直接連接到AD9860/AD9862 SPI端口。為確保正確的電源排序和初始化,DSP應復位轉換器。為了進一步減少外部邏輯的引腳數,AD9860/AD9862的另一個選項(此處未顯示)允許將兩個10/12位ADC值時間復用到一條10/12位RXDATA總線上。雖然這將消除兩條10/12位總線之一,但它需要外部邏輯在將數據傳輸到DSP之前對數據進行解復用。

所有數據移動都由DSP中的memDMA控制或控制。讀取ADC數據時(見圖2),必須由外部邏輯驅動數據和ARDY信號。外部邏輯必須對/AOE引腳進行采樣,以檢查何時可以將數據驅動到ADSP-21535。/AOE 信號向外部邏輯指示 DMA 控制器已準備好獲取數據。接收器三態機如圖底部所示。

圖2.接收計時和狀態機。

當數據發送到DAC時(見圖3),外部邏輯必須對/AWE信號進行采樣,然后驅動ARDY。/AWE 向外部邏輯指示 DMA 控制器何時準備好使用新數據。變送器四態機如圖底部所示。

圖3.傳輸定時和狀態機。

結論

盡管ADSP-21535并非專門設計用于連接高速并行轉換器,但它具有許多其他優點,可用于需要快速上市的設計。具有專用并行外設接口(PPI)的ADSP-BF532等新一代器件將很快推出,以更低的成本為此類應用提供更明確的解決方案。為了滿足緊急需求,我們建議使用一種低成本的“無先進先出”解決方案,直到下一代零件批量生產為止。這將使目前的300 MHz ADSP-21535能夠與采樣速率高達24 MSPS的ADC和DAC接口。如果ADSP-21535內核的時鐘頻率可以專門定時為266 MHz,則最高轉換器采樣速率僅受ADSP-21535可以支持的最大SCLK(133 MHz)和突發間10周期memDMA延遲的限制:2 x 133 M/10 = 26.6 MHz。

審核編輯:郭婷

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601889 -

轉換器

+關注

關注

27文章

8628瀏覽量

146873 -

asic

+關注

關注

34文章

1194瀏覽量

120331

發布評論請先 登錄

相關推薦

高速DSP與串行A/D轉換器TLC2558接口的設計

如何用TIFIFOS和TMS320DSP實現高速數據轉換器接口的英文資料概述

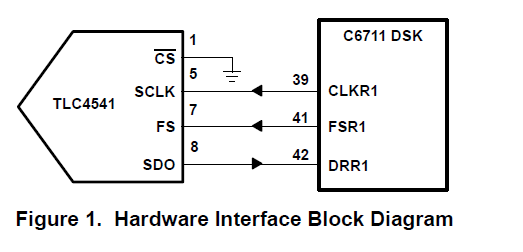

如何將TLC4541模數轉換器連接到TMS320C6711 DSP的方法詳細概述

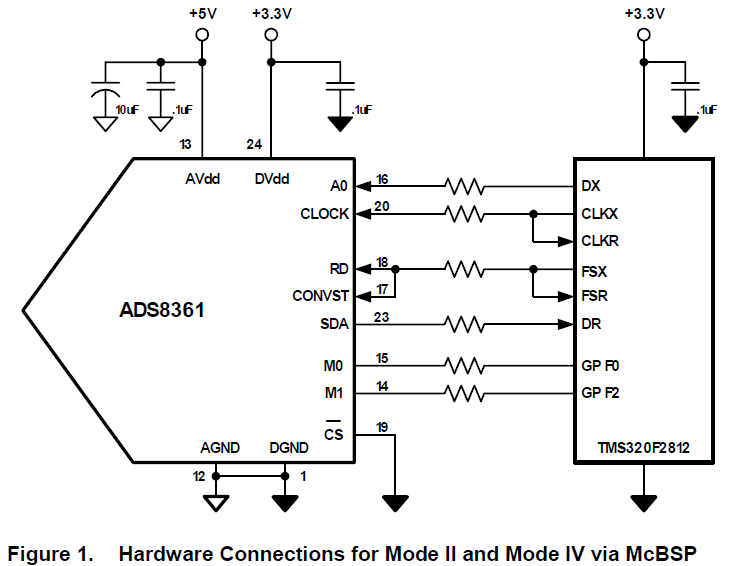

幾種將ADS8361數字轉換器連接到TMS320F2812 DSP的方法的詳細概述

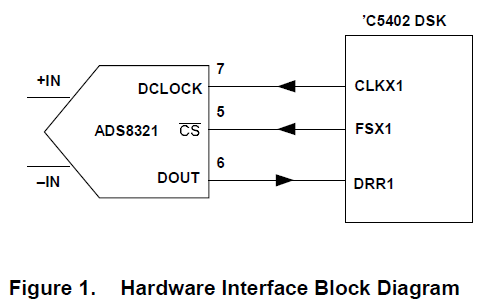

如何將ADS8320模數轉換器連接到TMS320C5402 DSP的方法詳細概述

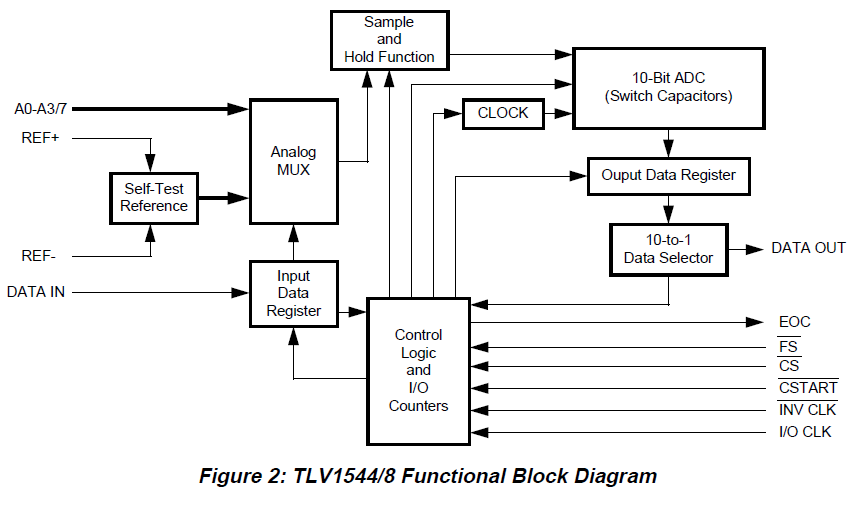

將AD轉換器連接到DSP和MCU的軟硬件要求詳細概述

EE-258:將Micron MT9V022圖像傳感器連接到Blackfin?處理器

EE-300:將Blackfin?EZ-KIT Lite?板連接到CMOS圖像傳感器

EE-302:將ADSP-BF53x Blackfin?處理器連接到NAND閃存

EE-234:通過串行端口將T1/E1收發器/成幀器連接到Blackfin?處理器

EE-184:將EPSON S1D13806內存顯示控制器連接到Blackfin?處理器

EE-203:通過異步端口將ADSP-BF535/ADSP-BF533 Blackfin?處理器連接到NTSC/PAL視頻解碼器。

EE-162:通過外部存儲器總線將ADSP-BF535 Blackfin處理器連接到高速轉換器(如AD9860/2上的轉換器)

將Blackfin DSP連接到無線應用的高速轉換器

將Blackfin DSP連接到無線應用的高速轉換器

評論