本文整理自2023年6月12日~6月18日,本公眾號(hào)【FPGA算法技術(shù)交流群】的相關(guān)問(wèn)答。相關(guān)問(wèn)題的解答和交流來(lái)自群成員,僅作參考。

問(wèn)

FPGA做IC的原型驗(yàn)證,速度大概跑多少?很多ASIC運(yùn)行主頻遠(yuǎn)遠(yuǎn)高于FPGA,仿真能cover住嗎?

答

FPGA主要用來(lái)做功能驗(yàn)證,一些接口確實(shí)需要那么高那就上,其他的不需要。Emulator可用并行計(jì)算時(shí)序的方式來(lái)仿真,更加接近仿真,但比仿真快得多。Emulator大概幾M的速度,Prototype大概10到100M。流片之前盡可能去模擬他的功能和性能,最接近的就是FPGA原型驗(yàn)證。

問(wèn)

PHY怎么驗(yàn)證到位?正確性由誰(shuí)來(lái)保證呢?

答

原型驗(yàn)證的PHY也不一定和ASIC的一致,保證通路即可。另外有些PHY可以用FPGA自帶的PHY IP來(lái)模擬。任何驗(yàn)證手段都是互相補(bǔ)充,最終達(dá)到完備性。

模擬的器件會(huì)有模擬端來(lái)驗(yàn)證,數(shù)字的基本功能都會(huì)先在Simulation保證,純數(shù)字就代表可綜合。模擬的就會(huì)抽可綜合的模型來(lái)替換。模擬的設(shè)計(jì)在模擬端保證,和數(shù)字集成到一起的時(shí)候就會(huì)模擬數(shù)字化。

PHY有單獨(dú)的IP,接口協(xié)議都是統(tǒng)一的。例如PCIe、DDR4、Ethernet等。Simulation和Emulator都有相應(yīng)的PHY model,F(xiàn)PGA階段也可以用原廠(chǎng)的PHY板,但有時(shí)沒(méi)必要,因?yàn)楦咚俳涌诙际菢?biāo)準(zhǔn)的,所以可能會(huì)用別的ip去代替,然后和真實(shí)device連接,保證通路,軟件測(cè)試通過(guò)就可以。

如果是數(shù)模混合芯片,設(shè)計(jì)過(guò)程中數(shù)字可以把RTL或后端輸出的網(wǎng)表,導(dǎo)入給模擬工程師做模擬域的仿真。反過(guò)來(lái)模擬也可以出verilog模型給數(shù)字工程師在數(shù)字域仿真。

問(wèn)

2MHz ,2V Vpp,放大到10vpp,應(yīng)該選用多大的運(yùn)放?如何計(jì)算帶寬?

答

如果是電壓反饋運(yùn)放,建議選擇20M以上,理論計(jì)算10M以上即可。而且應(yīng)該是全功率帶寬,不能只看小信號(hào)帶寬。如果是電流反饋型,選個(gè)5M估計(jì)足夠,另外就是電流驅(qū)動(dòng)能力。帶寬的話(huà),運(yùn)放指標(biāo)主要是增益帶寬積,開(kāi)環(huán)增益和開(kāi)環(huán)帶寬的乘積。

問(wèn)

有個(gè)問(wèn)題請(qǐng)教一下,F(xiàn)PGA芯片怎么能把10k的時(shí)鐘擴(kuò)到100M?

答

MMCM和PLL的輸入下限分別是10M和19M,設(shè)計(jì)思路可能需要和團(tuán)隊(duì)一起商討一下。

問(wèn)

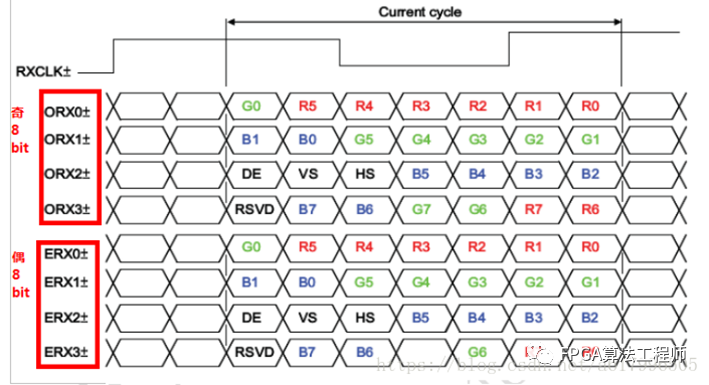

請(qǐng)教一個(gè)LVDS接收問(wèn)題。需要考慮如何將數(shù)據(jù)和時(shí)鐘對(duì)齊。但是LVDS視頻流沒(méi)有同步碼,大家是怎么處理同步?

答

有兩種方法,要么數(shù)據(jù)里邊有特殊字符,要么有其它信道傳輸同步信息。對(duì)于視頻圖像,一般都會(huì)有接口協(xié)議,行、場(chǎng)同步信號(hào)。

de就是同步信號(hào),hs是行同步,vs是場(chǎng)同步。把視頻流用顯示器顯示出來(lái),然后通過(guò)修改skew然后找到圖像由壞變好和由好變壞的臨界點(diǎn),然后中間位置就是最穩(wěn)定的,一般調(diào)整90°就行。還有一些芯片自備prn碼調(diào)試這個(gè)skew。其實(shí)對(duì)于這種VESA格式的視頻流,還有更簡(jiǎn)單的方式,直接調(diào)用Xilinx的selectio ip核。采用DDR模式就能采下來(lái)。

如果用不了DDR模式,可參考Xilinx的Xapp585,就是這種時(shí)序的例程。里面收發(fā)都有,還有g(shù)earbox例程,教你怎么樣將8bit或者4bit轉(zhuǎn)為7bit。

此外,對(duì)于接收數(shù)據(jù),Xapp524講這個(gè),需要做個(gè)狀態(tài)機(jī),找到delay調(diào)整值,每次上電之前等這個(gè)狀態(tài)機(jī)穩(wěn)定了再開(kāi)始拿數(shù)據(jù)。但是這個(gè)設(shè)計(jì)是不考慮系統(tǒng)溫升對(duì)IO的影響的,如果可靠性要求高,需要隔一段時(shí)間校準(zhǔn)一下IO的delay。

問(wèn)

有沒(méi)有邏輯優(yōu)化的一些資料?

答

推薦高亞軍老師的《AMD FPGA設(shè)計(jì)優(yōu)化寶典》,VHDL版已上市,verilog版據(jù)說(shuō)即將出版。

此外,《高級(jí)FPGA設(shè)計(jì):結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化》也可以看看。

問(wèn)

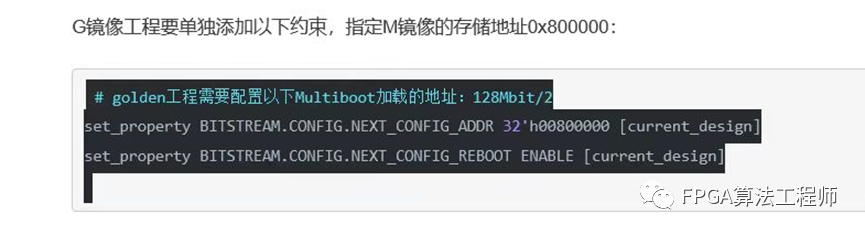

這個(gè)鏡像地址是根據(jù)flash確定的嗎?

答

golden起始地址必須是0,upgrade是800-000,16M flash空間的一半。

問(wèn)

輸入輸出雙向的端口(inout),我直接定義為輸出端口(output)使用,大家有這樣用過(guò)嘛?會(huì)有問(wèn)題嘛?

答

FPGA的user IO,電路結(jié)構(gòu)是雙向的。然后我們根據(jù)需要,聲明位input/output或者inout。外部I2C器件,把scl定義為output,可以正常訪(fǎng)問(wèn)。如果是zynq的PS I2C,要聲明為雙向,sda要設(shè)置為雙向。如果PS的I2C拉到EMIO,那么SCK也要設(shè)為雙向。盡管就PS一個(gè)主設(shè)備。

問(wèn)

求問(wèn),Vivado里FFT和LTE FFT的IP核有啥區(qū)別呢?

答

LTE FFT要收費(fèi),但是支持1536點(diǎn)。LTE FFT說(shuō)白了就是額外支持3*2^k點(diǎn)數(shù)的變換。Vivado里DFT點(diǎn)數(shù)支持1536,可以使用統(tǒng)一的2048點(diǎn)FFT實(shí)現(xiàn)所有帶寬模式的處理。

問(wèn)

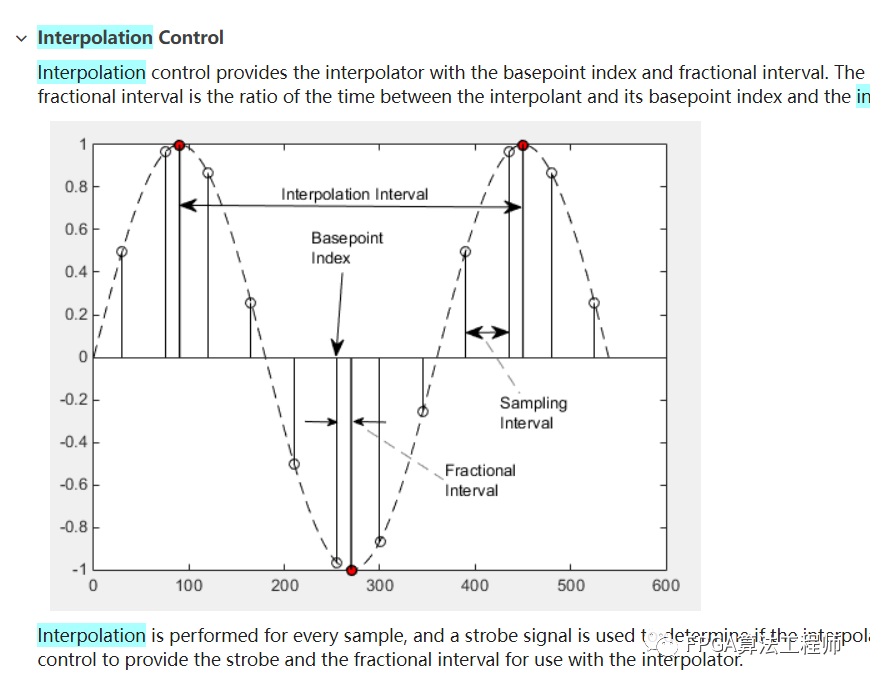

8184點(diǎn)數(shù)據(jù),怎么均勻下采樣到2048個(gè)數(shù)據(jù)啊?采樣時(shí)鐘的8.184M,1ms相干積分。

答

設(shè)計(jì)算法時(shí)候需要考慮硬件實(shí)現(xiàn),AD采了樣,DFE中濾波,可以再來(lái)個(gè)法羅插值找最佳采樣點(diǎn)。符號(hào)定時(shí)同步,可以參考一下Michael Rice的《Digital Communications:A Discrete-Time Approach》中的第8章:Symbol Timing Synchronization。此外,也可參考一下Umberto Mengli的《Synchronization Techniques for Digital Receivers》。

問(wèn)

AXI4,AXI4-Lite,AXI-Stream這三個(gè)在應(yīng)用上怎么考慮選擇?

答

AXI4包含3種類(lèi)型的接口: (1)AXI4:主要面向高性能地址映射通信的需求; (2)AXI4-Lite:是一個(gè)輕量級(jí)的,適用于吞吐量較小的地址映射通信總線(xiàn); (3)AXI4-Stream:面向高速流數(shù)據(jù)傳輸。

第一個(gè)有突發(fā),第二個(gè)無(wú)突發(fā),第三個(gè)無(wú)地址。在仿真時(shí),Vivado 模板 AXI-Lite Master和AXI-Lite Slave連上仿真,AXI4可以和MIG連著仿真。Xilinx 有個(gè)AXI Verification IP ,就四步驟:1.引入兩個(gè)package,2.聲明agent,3.用new還是start 函數(shù),即創(chuàng)建和掛載,4.寫(xiě)一些task。可以參考官方的例程。

此外,可以看一下本公眾號(hào)之前的一篇文章,點(diǎn)擊鏈接《AMBA協(xié)議規(guī)范(一)》可跳轉(zhuǎn)原文閱讀。

問(wèn)

FFT后實(shí)部,虛部的bit位寬是如何確定的?

答

Xilinx的IP,一般在處理IQ信號(hào)時(shí),都是虛部在高位,實(shí)部在低位。IP配置時(shí),在左側(cè)欄,能顯示FFT的輸入和輸出位寬,和定點(diǎn)格式。FFT的輸出位寬和輸入也有關(guān)系,配置的時(shí)候注意。此外,DFE和ADC的IQ數(shù)據(jù)位寬和實(shí)部、虛部,將決定FFT的輸入。

問(wèn)

flash讀寫(xiě),一般是大端還是小端?如果是QSPI,讀寫(xiě)一個(gè)字節(jié)比如3E,是先3還是先E啊?

答

看QSPI的協(xié)議規(guī)定,注意位序。

問(wèn)

mcs文件固化,讀寫(xiě)flash是跟bin文件還是mcs文件對(duì)得上?

答

理論上,mcs和bin 都可以,習(xí)慣用bin。

問(wèn)

FPGA需要這樣的一個(gè)場(chǎng)景,MUX選擇是從6個(gè)時(shí)鐘中選擇1個(gè),并且時(shí)鐘頻率都不低(有沒(méi)有合理使用BUFGMUX的方案,我目前能想到的是利用多級(jí)BUFGMUX來(lái)實(shí)現(xiàn))?

答

不建議切時(shí)鐘,而是邏輯設(shè)計(jì)中做跨時(shí)鐘處理,切時(shí)鐘可靠性不好做。如果硬要這么設(shè)計(jì),試一下Vivado的MMCM動(dòng)態(tài)配置功能。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1626文章

21666瀏覽量

601833 -

原型驗(yàn)證

+關(guān)注

關(guān)注

0文章

22瀏覽量

10727 -

lvds

+關(guān)注

關(guān)注

2文章

1036瀏覽量

65703 -

PHY

+關(guān)注

關(guān)注

2文章

301瀏覽量

51694 -

時(shí)序

+關(guān)注

關(guān)注

5文章

385瀏覽量

37276

原文標(biāo)題:FPGA算法技術(shù)交流問(wèn)答集錦(6.12~6.18)

文章出處:【微信號(hào):FPGA算法工程師,微信公眾號(hào):FPGA算法工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

PCB Layout and SI設(shè)計(jì)問(wèn)答集錦

fpga精選問(wèn)答集錦

運(yùn)放經(jīng)典問(wèn)答集萃及其最新工業(yè)和科技趨勢(shì)

高速PCB設(shè)計(jì)入門(mén)概念問(wèn)答集

高速PCB設(shè)計(jì)入門(mén)知識(shí)問(wèn)答集

PCB電鍍知識(shí)問(wèn)答集錦

CAXA經(jīng)驗(yàn)談問(wèn)答集

購(gòu)買(mǎi)iphone問(wèn)答集匯

電阻器的種類(lèi)及其特性問(wèn)答集匯

PROTEL應(yīng)用常見(jiàn)問(wèn)題及問(wèn)答集

特瑞仕 | 線(xiàn)性穩(wěn)壓IC網(wǎng)絡(luò)研討會(huì)問(wèn)答集錦,請(qǐng)查收~

有關(guān)FPGA的問(wèn)答集錦

有關(guān)FPGA的問(wèn)答集錦

評(píng)論