廣義而言,半導體基板即為晶圓。我們可以直接在晶圓表面堆疊晶體管,即半導體電路的基本元件,也可以構建新的一層,將其作為基板并在上面形成器件。特別是用于通信、軍事和光學元件等特殊用途的晶體管,或是高性能和高質量的晶體管,它們都需要用到外延晶片。在本文中,我們將介紹這種在晶圓之上由超純硅構成的超高純層(也被稱為“外延層)的形成過程、用途和特征。

1.外延層,超純晶圓上的“超高純”層

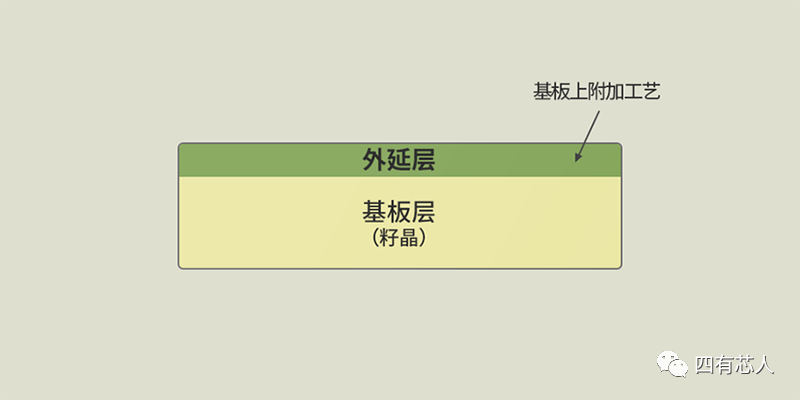

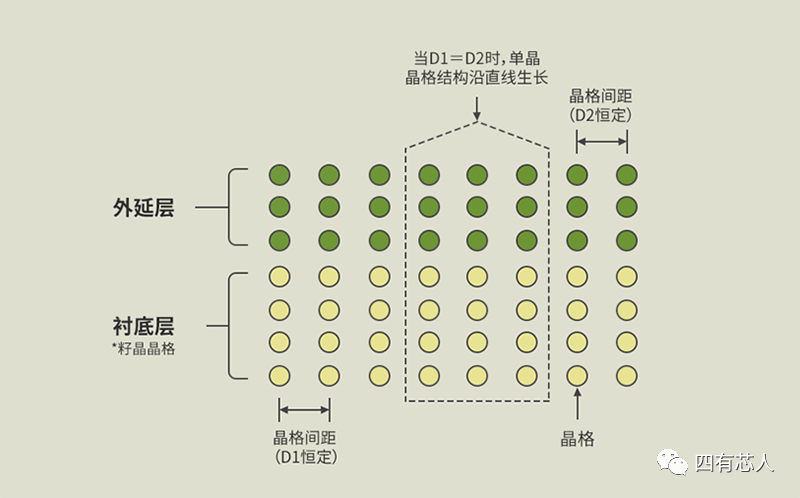

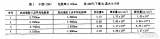

圖1.初始籽晶和附加工藝流程所在的外延層

晶圓制造過程獨立于半導體制造過程。它將熔融硅轉化為純度近100%的高純度晶圓,并將其切割成板狀。晶圓制造涉及各種材料,包括從集成電路最常用的硅和鍺,到用于高速模擬的砷化鎵。

總體而言,晶圓制造工藝流程大多相似,僅在工藝條件和方法上略有不同。硅片可分為三類超純硅片、(P型/N型)摻雜硅片以及經過附加工藝處理的外延片。其中,P型硅片最為常用。這是因為只要在P型基板上完成N-Well(半導體制造工藝),就可以簡單地制造互補金屬氧化物半導體場效應晶體管(CMOSFET)。外延片是對超純晶圓施加附加工藝(即所謂的外延工藝)后的產物,此時的超純晶圓稱為籽晶(中間產物)。

2.形成外延層的前提條件:晶體結構

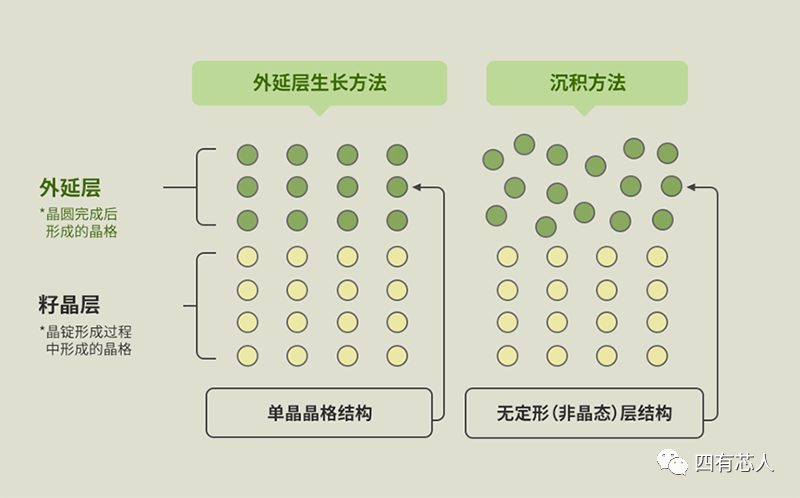

圖2.外延層與非晶層

在英語中,外延(epitaxial)一詞的前綴“epi-”表示“在上面”,而外延層則是指向上形成的層。外延一詞代表外延生長,這意味著新層不斷堆疊生長形成單晶。單晶為固態,其中同一類型的所有晶體沿著特定的晶軸有規律地形成,同時籽晶位于下方且晶格方向保持不變。

在晶體管結構中,充當漏極電流流動路徑的基板應具有晶體結構;然而,由于在半導體制造工藝前期所使用的大多數沉積方法都會有非晶(無定型)層,因此需要依靠特殊條件和方法生成外延層,以避免出現非晶態。

要用作籽晶層,晶格應具備晶體結構,同時依照下層晶格結構向上生長。因此,重要的是形成晶格排列規則且晶格常數一致或相似的層。由此,通過特殊方法在籽晶層上形成的新層或基板便是外延層,而外延層所覆蓋的晶圓被稱為外延片。

3.晶格內電子流動條件

圖3-1.不同層平均電子流動速率對比-單晶層:快

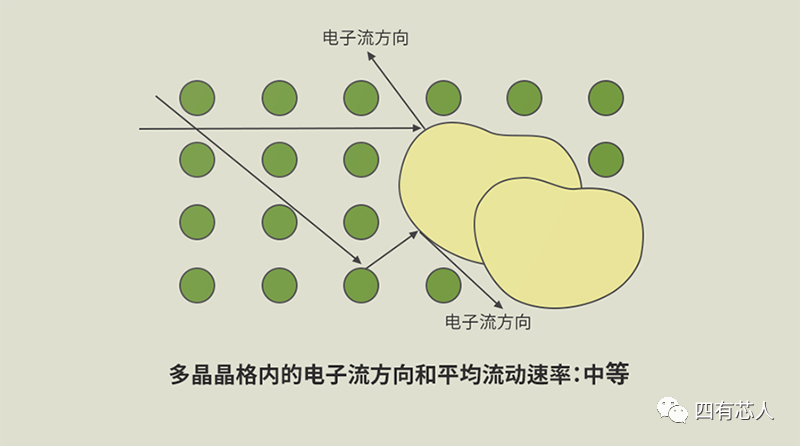

圖3-2.不同層平均電子流動速率對比-多晶層:中等

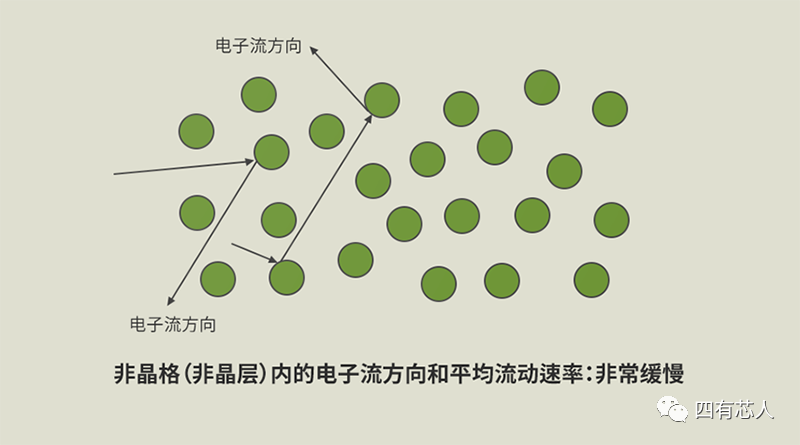

圖3-3.不同層平均電子流動速率對比-無定形(非晶)層:慢

(單晶層>多晶層>無定形(非晶)層)

半導體器件的功能包括促使電子流動,檢測和判斷流動情況,并將判斷結果以開/關形式呈現。在籽晶上進行附加工藝(超高純)處理是為了制造一個無任何缺陷的層,以此促進電子在零缺陷場中的流動。

要想增加電子在某個方向上的流動速度,晶格必須呈規則排列。當原子之間的距離恒定時則更為有利。換句話說,多晶或非晶(無定型)晶格的排列會削弱電子流動速率并形成電子陷阱,從而增加了柵極電壓和漏極電流預測和管理難度。

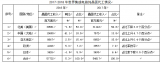

4.晶格常數

圖4.外延層和單晶結構的晶格常數

晶格常數是指硅原子之間的鍵(共價鍵)間距。當任何一種其它元素進入硅原子間時,原子的電荷量發生變化,導致原子間距(晶格常數)發生變化。盡可能避免晶格常數的改變是非常重要的。這是因為晶格常數不一致會影響上下層的熱膨脹系數,很可能導致晶圓翹曲。此外,當堆疊二氧化硅或二氧化鉿作為柵極氧化層時,若是通過外延生長制造出晶格常數一致的超高純層,而非在含雜質的硅基板上進行堆疊,可以將接觸面之間的電子陷阱和接觸面之間的失配情況(粘結程度減弱等)降至最低。

盡管外延層品質優良,但由于制作工藝復雜、成本較高,且外延工藝需要依靠單晶生長,處理速度緩慢,因此外延層僅在特殊情況下使用。

5.晶格匹配和失配情況

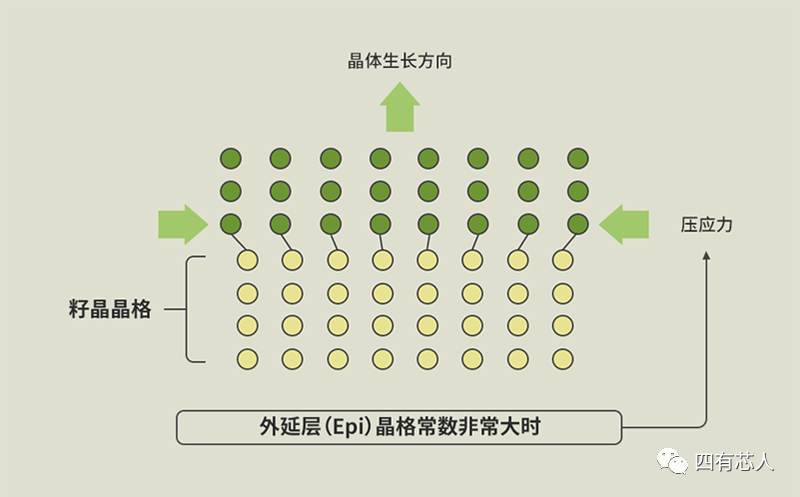

圖5-1.兩種異質外延情況-外延層晶格常數非常大時

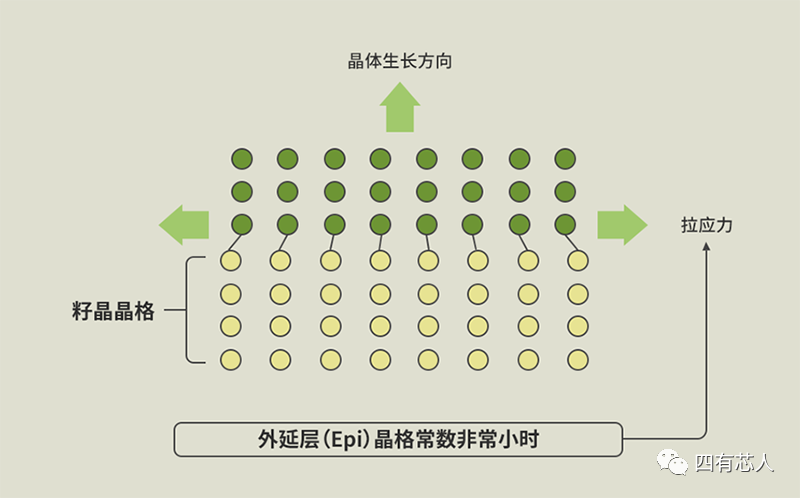

圖5-2.兩種異質外延情況-外延層晶格常數非常小時

當晶體結構中的籽晶層和外延層具有相同間距時,我們稱之為同質外延,反之,我們稱之為異質外延。在異質外延的情況下,當外延層的晶格間距較大時,需要施加壓應力使其與籽晶層間距相匹配。相反,當外延層晶格間距小于下層籽晶層晶格間距時,需要施加拉應力來增加間距。

原子的結合形成晶體結構,或稱晶格。如果晶體結構中原子間距不匹配,則會出現包括空洞、突起在內的缺陷,進而引發質量問題。通過在基板上生成新的外延基板可以克服這些問題。重要的是,如果在外延層形成的同時進行摻雜操作,則可按需形成雜質層,并將其作為基板,制作半導體部件。

審核編輯:劉清

-

半導體

+關注

關注

334文章

27010瀏覽量

216306 -

晶體管

+關注

關注

77文章

9634瀏覽量

137849 -

柵極電壓

+關注

關注

0文章

69瀏覽量

12777

原文標題:在超純晶圓上堆疊超高純層的外延技術

文章出處:【微信號:半導體封裝工程師之家,微信公眾號:半導體封裝工程師之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

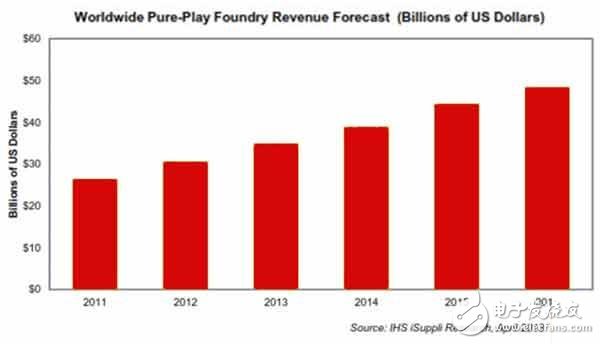

2019年純晶圓代工市場中國增長最快 預計2020年晶圓代工IC總產能將增長4%

2013年全球純晶圓代工產業營收預計達350億美元

如何在超純晶圓上堆疊超高純層的外延技術呢?

如何在超純晶圓上堆疊超高純層的外延技術呢?

評論