1 軟件和硬件

1.1 軟件和硬件的定義

指令是軟件和硬件的媒介,指令的復(fù)雜度決定了系統(tǒng)的軟硬件解耦程度。

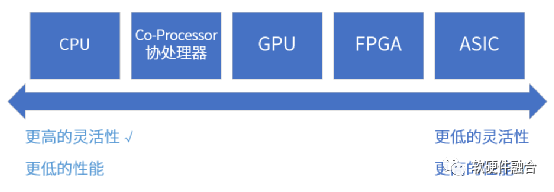

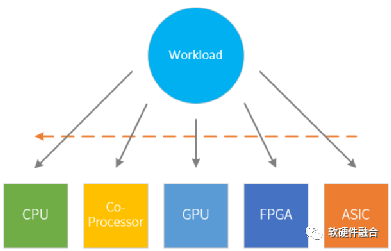

按照單位計算(指令)的復(fù)雜度,處理器平臺大致分為CPU、協(xié)處理器、GPU、FPGA和ASIC。從左往右,單位計算越來越復(fù)雜,靈活性越來越低。

任務(wù)在CPU運行,則定義為軟件運行;任務(wù)在協(xié)處理器、GPU、FPGA或ASIC運行,則定義為硬件加速運行。

1.2 “硬件定義軟件”和“軟件定義硬件”的定義

軟件定義是當前非常熱門的話題,比如軟件定義網(wǎng)絡(luò)、軟件定義數(shù)據(jù)中心、軟件定義汽車等等。軟件定義的范疇非常大,不僅僅涉及到底層的軟硬件技術(shù),也涉及到系統(tǒng)的運行管理、監(jiān)控、更新等,甚至還涉及到商業(yè)上的一些考量。

系統(tǒng)是由軟件和硬件組成。當我們說軟件定義XX的時候,其實說的是軟件定義XX系統(tǒng)。本文篇幅有限,從最底層的軟件和硬件相關(guān)的技術(shù)以及兩者之間的相互關(guān)系和影響來闡述系統(tǒng)中軟件定義和硬件定義。

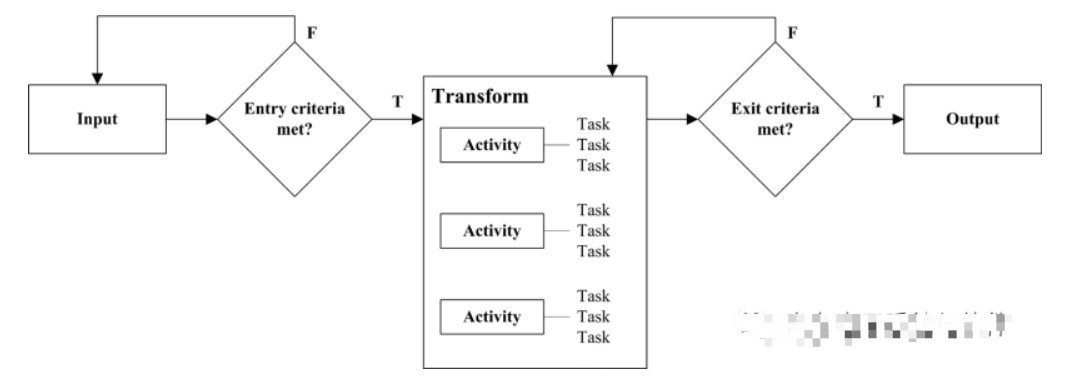

“硬件定義軟件”定義為:

當一個系統(tǒng)的主要業(yè)務(wù)邏輯是在硬件中實現(xiàn),協(xié)同的軟件是為輔助。

相關(guān)的軟件是依賴于硬件提供的接口構(gòu)建。

對應(yīng)的,“軟件定義硬件”定義為:

當一個系統(tǒng)的主要業(yè)務(wù)邏輯是在軟件中實現(xiàn);系統(tǒng)中沒有硬件引擎,或者硬件引擎是軟件可編程的;硬件引擎按照軟件編程的邏輯執(zhí)行操作。

相關(guān)的硬件依賴于軟件提供的接口構(gòu)建。

1.3 CPU,軟件和硬件解耦

CPU是最靈活的,原因在于運行于CPU指令都是最基本粒度的加減乘除外加一些訪存及控制類指令,就像積木塊一樣,我們可以隨意組合出我們想要的各種形態(tài)的功能。

很多人會認為,CPU可以自動的執(zhí)行非常復(fù)雜的計算機程序,這是CPU最大的價值所在。其實不然,CPU最大的價值在于提供并規(guī)范了標準化的指令集,使得軟件和硬件從此解耦:

硬件工程師不需要關(guān)心場景,只關(guān)注于通過各種“無所不用其極”的方式,快速的提升CPU的性能。

而軟件工程師,則完全不用考慮硬件的細節(jié),只關(guān)注于程序本身。然后有了高級編程語言/編譯器、操作系統(tǒng)以及各種系統(tǒng)框架/庫的支持,構(gòu)建起一個龐大的軟件生態(tài)超級帝國。

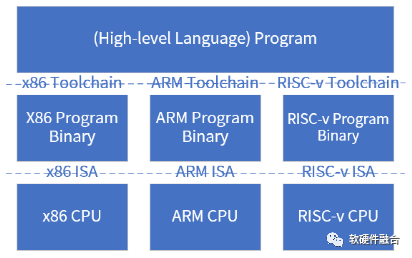

在桌面和服務(wù)器領(lǐng)域,X86是最流行的處理器架構(gòu)。而在手機等移動端,ARM則占據(jù)絕對的統(tǒng)治地位。開源RISC-v符合未來技術(shù)和商業(yè)發(fā)展的趨勢,其在MCU領(lǐng)域已經(jīng)占據(jù)重要地位,并且在向桌面和服務(wù)器領(lǐng)域發(fā)起沖鋒。

軟件的龐大生態(tài),是構(gòu)建在特定的CPU架構(gòu)之上的。但是,我們一般來說,CPU作為指令足夠細粒度,計算足夠通用的計算平臺,其是軟件和硬件解耦的:

一方面,特定架構(gòu)下,每種CPU架構(gòu)“基本”保證了向前兼容,這樣可以認為,在特定架構(gòu),軟件硬件完全解耦各自發(fā)展。

另一方面,(理想狀態(tài)下,)OS、編譯器等越來越成熟之后,能夠保證,同樣的高級語言程序,在不同的CPU架構(gòu)平臺,其運行行為是一致吧。這樣就可以脫離具體的CPU架構(gòu)憑條,構(gòu)建完全無差別的軟件生態(tài)。

從長期發(fā)展的角度,RISC-v應(yīng)該會是未來更好的選擇:

開放性。RISC-v最大的特點是其指令集開源,這樣任何廠家就可以根據(jù)自己情況設(shè)計自己的RISC-v CPU,然后大家共建一套開放的生態(tài),共生共榮。

標準化。標準化是最關(guān)鍵的價值。所有的架構(gòu)(x86/ARM/RISC-v)都可以認為是標準的,但因為RISC-v的開放性,其標準化未來的價值就會非常大。上面說過,“理想”情況下,我們可以把程序無縫的從一個平臺遷移到其他平臺,但實際上,許多商業(yè)的軟件,我們并不能拿到源碼。而且,許多時候,一些細節(jié)問題,都可能導(dǎo)致平臺遷移失敗。這種遷移對用戶來說是非常大的挑戰(zhàn)和風(fēng)險。當標準的RISC-v足夠流行之后,基于RISC-v構(gòu)建的整個生態(tài)會迸發(fā)強大的生命力。

其他。如RISC-v沒有歷史包袱,指令集更高效;更靈活的擴展能力(確保不碎片化);等等。

1.4 CPU的軟硬件定義

CPU和軟件程序的交互接口是指令集,是最細粒度的加減乘除等指令,像積木塊一樣,隨意組合出任意想要的各種程序。

CPU到底是軟件定義還是硬件定義,從不同的角度有不同的看法:

軟件和硬件并行發(fā)展。CPU,通過ISA,“完美”實現(xiàn)了軟件和硬件的標準化解耦。因此,可以認為,在這個時候,不存在硬件定義軟件或軟件定義硬件,軟件和硬件各自并行不悖的快速發(fā)展。

硬件定義軟件。基于CPU構(gòu)建的龐大軟件生態(tài),這可以算作是“硬件定義軟件”:先有CPU硬件,再有編譯器,再有OS、應(yīng)用等。

軟件定義系統(tǒng)。但是,站在軟件的角度,所有的系統(tǒng)實現(xiàn)均可以通過編程實現(xiàn),根本不需要考慮運行的CPU平臺的“差一些”,因此又可以看做基于CPU運行的系統(tǒng)是“軟件定義”的。

2 硬件定義軟件

2.1 系統(tǒng)從軟件逐步到硬件

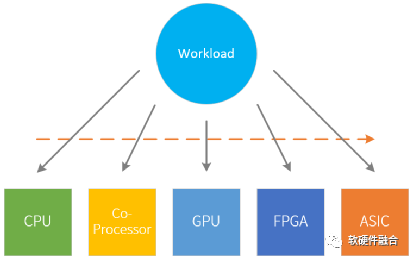

一個系統(tǒng),必然經(jīng)過前期快速迭代,后期逐漸穩(wěn)定的過程。因此,系統(tǒng)運行的處理器平臺選擇也必然有如下的一些規(guī)律:

CPU通用軟件平臺:當一個新的應(yīng)用出現(xiàn)的時候,最早出現(xiàn)的一般是軟件實現(xiàn)。一來實現(xiàn)所需要的代價較少,可以快速實現(xiàn)想法;二來CPU所提供的靈活性,不考慮性能的情況下,使之幾乎可以處理任何場景的任務(wù)。

協(xié)處理器擴展指令加速平臺:隨著技術(shù)的演進,對性能提出了一些要求。這個時候,可以針對一些比較消耗CPU資源的程序進行一定的編程和編譯優(yōu)化。

GPU向量及并行加速平臺:更進一步的,技術(shù)廣泛應(yīng)用,并且我們能從算法中尋找到更多的并行性。這個時候,我們就可以找一些專用的處理器,如GPU、DSP、NPU等,來處理。通過特定的并行優(yōu)化以及支持向量(SIMD)、多指令并行(MIMD/VLIW)等復(fù)雜指令編譯優(yōu)化的方式,深度的優(yōu)化性能。

FPGA硬件可編程加速平臺:隨著技術(shù)越來越成熟,應(yīng)用的規(guī)模越來越大。也越來越消耗資源。這個時候,我們值得花費更多的精力,提煉出復(fù)雜度非常高的算法(或者可以當作一個非常復(fù)雜的“指令”)然后通過硬件邏輯實現(xiàn)。再通過FPGA硬件可編程的方式快速落地。

ASIC定制加速平臺:再進一步的,技術(shù)更加成熟穩(wěn)定,應(yīng)用規(guī)模足夠龐大,這個時候就非常有必要為此場景定制開發(fā)ASIC,來達到最優(yōu)的性能、最低的成本、最小的功耗。

當需要面向一個新領(lǐng)域開發(fā)的時候,要快速實現(xiàn),或者應(yīng)用的場景不夠確定,需要硬件平臺有足夠多的適應(yīng)性,這些情況使用CPU比較合適。當需要極致的效率,并且成本敏感、功耗敏感,而且規(guī)模足夠龐大,那么選擇定制開發(fā)ASIC會更合適一些。如果折中的,需要有一定的靈活性,又要保證一定的性能加速,并且應(yīng)用有足夠的并行度,這個時候GPU則更合適一些。

從軟件到硬件的一個經(jīng)典的例子就是比特幣,其激烈而快速的完成了從CPU到ASIC的過渡。比特幣使用的技術(shù)區(qū)塊鏈核心算法是SHA-256,它在各個平臺上的性能對比如下:

CPU:最開始的時候,大家使用CPU挖礦,一臺高端個人電腦,處理速度大概20MH/s(H/s, Hash per second);

GPU:后來有人用GPU加速挖礦,SHA-256可以繼續(xù)拆分成普通的算術(shù)邏輯運算,而GPU具有超級多的算術(shù)邏輯運算單元,一個高端顯卡的處理速度可以達到200MH/s;

FPGA:再后來出現(xiàn)了定制SHA-256算法硬件邏輯的FPGA加速卡來挖礦,精心設(shè)計的定制電路的FPGA,可以使運算速度達到1GH/s;

ASIC:而比特大陸公司2015年發(fā)布的ASIC礦機芯片BM1385,其性能達到單顆芯片算力可達32.5GH/s。

上述CPU、GPU、FPGA性能數(shù)據(jù)來自于《區(qū)塊鏈:技術(shù)驅(qū)動金融》,數(shù)據(jù)為2013年前后的性能數(shù)據(jù)。

2.2 硬件架構(gòu)決定了軟件設(shè)計

2.2.1 ASIC的硬件定義

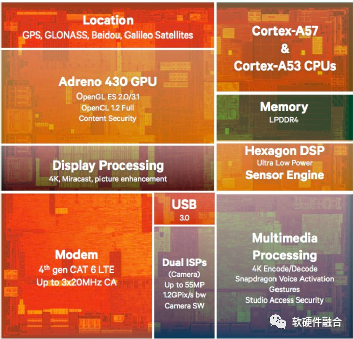

SOC是CPU、GPU、各種加速處理引擎(ASIC)以及接口模塊(ASIC)的集成。

智能手機使用電池供電,同時又要提供足夠強大的性能。如此苛刻的應(yīng)用條件,使得智能手機處理器通常都選用集成度非常高的SOC。上圖是高通手機SOC處理器驍龍810芯片,可以看到此芯片主要包括:

通用CPU:ARM Cortex-A57和Cortex-A53,CPU主要用于運行Android等智能手機操作系統(tǒng)以及APP程序;

特定場景處理器:Adreno 430 GPU、Hexagon DSP、ISP、多媒體處理器等,GPU主要用于3D游戲等場景,DSP主要用于傳感器算法處理;

特定功能子系統(tǒng):支持4G LTE的通信基帶處理、GPS/北斗等的定位模塊等;

安全處理模塊;

其他一些外圍模塊。

于是,手機系統(tǒng)就形成了如下表格的分層:

| 應(yīng)用層 | 應(yīng)用程序 |

| 系統(tǒng)層 | 操作系統(tǒng)Android/iOS等 |

| 驅(qū)動層 | Driver和HAL |

| 硬件層 | 通用CPU;GPU、DSP、ISP等處理引擎;4G、GPS等子系統(tǒng);WiFi、USB、藍牙等連接模塊;安全模塊;其他。 |

2.2.2 GPU的硬件定義

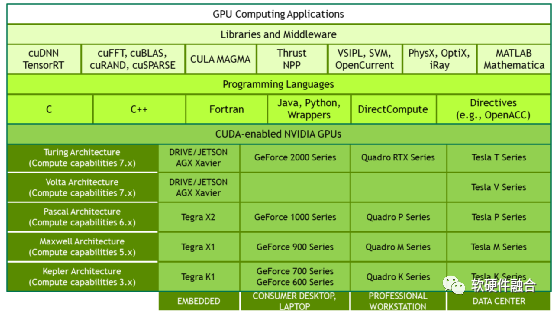

GPU由數(shù)以千計的CUDA核組成,要想對數(shù)以千計的CPU內(nèi)核進行編程,把這么多核的計算性能發(fā)揮出來,是非常大的挑戰(zhàn)。

GPU編程有一個最重要的約束是在同一個并行線程組里運行的是相同的程序,也稱之為“齊頭并進”。即使如此,GPU的編程難度依然相當?shù)拇蟆?/p>

于是,為了提升GPU編程易用性和快捷性的CUDA編程框架應(yīng)運而生了。

2006年NVIDIA推出了CUDA,這是一個通用的并行計算平臺和編程模型,利用NVIDIA GPU中的并行計算引擎,以一種比CPU更高效的方式解決許多復(fù)雜的計算問題。CUDA提供了開發(fā)者使用C++作為高級編程語言的軟件環(huán)境。也支持其他語言、應(yīng)用程序編程接口或基于指令的方法,如FORTRAN、DirectCompute、OpenACC。

CUDA是NVIDIA成功的關(guān)鍵,它極大的降低了用戶基于GPU并行編程的門檻,在此基礎(chǔ)上,還針對不同場景構(gòu)建了功能強大的開發(fā)庫和中間件,逐步建立了GPU+CUDA的強大生態(tài)。

2.3 總結(jié)

2.3.1 系統(tǒng)業(yè)務(wù)邏輯的實現(xiàn)形式,決定了軟硬件定義

三類典型的平臺:

CPU,因為是完全細粒度的指令,可以非常靈活的組織出來想要的程序。

ASIC,ASIC是把系統(tǒng)的業(yè)務(wù)邏輯固化到硬件中。優(yōu)勢在于,完全定制ASIC實現(xiàn)了最精簡的晶體管資源占用,實現(xiàn)最極致的性能。當一個系統(tǒng)功能非常固定,并且未來也不會有非常頻繁的更新的情況下,ASIC是幾乎最優(yōu)的選擇。

GPU,則介于CPU和ASIC之間,具有一定性能的同時,具有一定的靈活性。

根據(jù)系統(tǒng)業(yè)務(wù)邏輯的具體實現(xiàn):

CPU是一個完全靈活無約束的可編程平臺,系統(tǒng)運行于CPU,則說系統(tǒng)是完全軟件定義的。也既是說,可以通過軟件編程的方式,完全自由的定義自己需要的系統(tǒng)業(yè)務(wù)邏輯。

系統(tǒng)運行于ASIC,則說系統(tǒng)是完全硬件定義的。也即是說,ASIC的整個系統(tǒng)邏輯都是硬件寫死的,軟件只是一些簡單的初始化配置和運行控制。

GPU,則是介于軟件定義和硬件定義之間。

2.3.2 軟件依賴于硬件平臺而存在

ASIC實現(xiàn)的是整個SOC大系統(tǒng)中的一個子系統(tǒng),整個子系統(tǒng)的業(yè)務(wù)邏輯基本上是在ASIC模塊硬件中完成(有時候需要控制面軟件來控制ASIC模塊的運行),因此,其性能相對CPU和GPU較高。

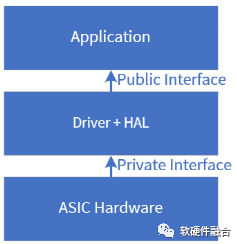

當我們設(shè)計一個ASIC硬件模塊或加速器的時候,需要提供相應(yīng)的驅(qū)動,如果是要接入OS等標準接口,還需要有一層HAL層負責把不同接口映射到OS的標準接口。應(yīng)用程序根據(jù)ASIC硬件提供的功能接口使用硬件。

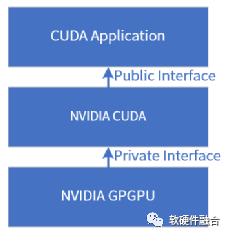

GPU平臺,硬件的GPGPU提供接口給CUDA,CUDA再提供接口給應(yīng)用。每一代具體的GPU,給上層提供的是不同的訪問接口, CUDA框架有特定的驅(qū)動和HAL屏蔽不同GPU的實現(xiàn)細節(jié);并且CUDA為了向前兼容和維護生態(tài),最終映射到標準的庫。這些標準的庫,提供了標準的接口給上層的CUDA應(yīng)用程序。

即使CUDA映射成標準的庫API接口,CUDA程序依然是要依賴于CUDA提供的接口來設(shè)計應(yīng)用軟件。

總結(jié)一下,軟件依賴于硬件平臺存在,體現(xiàn)在兩個方面:

軟件只能根據(jù)硬件提供的功能來完成系統(tǒng)實現(xiàn),系統(tǒng)的業(yè)務(wù)邏輯是在硬件實現(xiàn);

軟件依賴硬件提供的接口訪問硬件,硬件提供什么樣的接口,軟件就使用什么樣的接口,主動權(quán)在硬件。

3 軟件定義硬件

3.1 系統(tǒng)又開始從硬件逐步到軟件

上一節(jié)我們講到,系統(tǒng)從起始發(fā)展,到逐步穩(wěn)定,系統(tǒng)的運行平臺逐步從CPU演進到ASIC。那么,ASIC是不是所有系統(tǒng)最終的運行平臺?

答案是否定的。原因主要如下:

軟件更新?lián)Q代很快。新的熱點技術(shù)層出不窮,已有的技術(shù)領(lǐng)域的更新迭代速度仍在快速增加。硬件的迭代周期過長,無法跟上軟件迭代的節(jié)奏。

定制的ASIC設(shè)計,把所有功能都在硬件實現(xiàn)。在復(fù)雜的云計算、自動駕駛等場景,芯片公司對用戶的場景理解可能不夠深入,會導(dǎo)致設(shè)計偏差。另一方面,也會限制用戶自身的主觀能動性,讓用戶有想法也很難在ASIC平臺去實現(xiàn)自己想要的功能。

ASIC因為功能固定,為了適配更多場景,確保芯片的大量出貨,勢必需要實現(xiàn)功能超集。例如,某ASIC芯片支持10個功能,但實際用戶場景,都是只需要2-3種功能。這樣,ASIC實現(xiàn)實際上也是低效的。并且,這些功能因為緊耦合的緣故,系統(tǒng)復(fù)雜度反而更高。

這樣,在許多場景,我們根據(jù)實際的場景需求,除ASIC,也開始選擇DSA、FPGA、GPU甚至CPU等處理引擎。

3.2 軟件定義網(wǎng)絡(luò)

最典型的一個案例就是SDN(Software Defined Network)的發(fā)展。經(jīng)過幾十年的發(fā)展,網(wǎng)絡(luò)芯片已經(jīng)演進到了完全ASIC的實現(xiàn),這意味著基于ASIC芯片的網(wǎng)絡(luò)設(shè)備其功能是確定的,用戶只能根據(jù)廠家實現(xiàn)的確定功能來使用網(wǎng)絡(luò)設(shè)備。

然而,隨著云計算、4G/5G移動通信等的發(fā)展,新的網(wǎng)絡(luò)協(xié)議和網(wǎng)絡(luò)功能層出不窮,純ASIC實現(xiàn)的網(wǎng)絡(luò)系統(tǒng)遇到了挑戰(zhàn)。

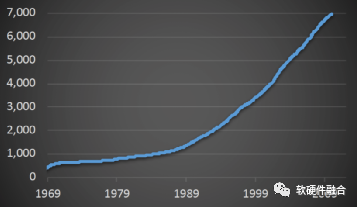

如上圖所示,IETF(Internet Engineering Task Force,互聯(lián)網(wǎng)工程任務(wù)組)的RFC(Request for Comments,請求意見稿,即網(wǎng)絡(luò)協(xié)議)數(shù)量一直在爆炸式的增長,應(yīng)用于各種新型網(wǎng)絡(luò)場景的新協(xié)議層出不窮。但是,傳統(tǒng)的網(wǎng)絡(luò)處理芯片都是封閉的、特定的設(shè)計,用于特定協(xié)議處理。想要增加新的協(xié)議非常困難,并且對新協(xié)議的支持受到不同供應(yīng)商的約束。定制的網(wǎng)絡(luò)處理芯片,對新協(xié)議的支持不足以及缺乏有效的靈活性,這使得要想在網(wǎng)絡(luò)系統(tǒng)增加新的功能非常困難,限制了客戶的網(wǎng)絡(luò)創(chuàng)新能力。

客戶希望能夠快速便捷的對網(wǎng)絡(luò)進行配置和管理;客戶希望能夠快速的進行網(wǎng)絡(luò)協(xié)議創(chuàng)新。這樣,ASIC的功能固定越來越成為網(wǎng)絡(luò)創(chuàng)新的約束。于是,SDN開始了兩個方面的創(chuàng)新:

第一步,網(wǎng)絡(luò)控制面和數(shù)據(jù)面分離,控制面可編程。把網(wǎng)絡(luò)控制面從數(shù)據(jù)面分離處理,形成了控制面可編程的Openflow協(xié)議。

第二步,進一步的,網(wǎng)絡(luò)數(shù)據(jù)面也可以編程,用戶可以定義自己的協(xié)議。形成了數(shù)據(jù)面可編程的P4語言和P4交換機相繼出現(xiàn)。

3.2.1 運行于CPU的軟件虛擬交換機

OVS(Open Virtual Switch)是Apache 2許可下的開源的軟件交換機。OVS的目標是實現(xiàn)一個生產(chǎn)環(huán)境的交換機平臺,支持標準管理界面,并為程序擴展和控制開放轉(zhuǎn)發(fā)功能。OVS非常適合在VM環(huán)境中用作虛擬交換機,除了向虛擬網(wǎng)絡(luò)層公開標準控制和可見性接口之外,它還旨在支持跨多個物理服務(wù)器的分發(fā)。OVS支持多種基于Linux的虛擬化平臺,包括Xen、KVM等。

最新的OVS版本支持以下功能:

NIC綁定在上行交換機上,可以支持LACP也可以不支持;

通過NetFlow,sFlow(R)和鏡像來增強可視性;

QoS(服務(wù)質(zhì)量)配置以及策略;

Geneve, GRE, VxLAN, STT和LISP隧道;

802.1ag連接故障管理;

OpenFlow 1.0以及眾多擴展;

支持C和Python的事務(wù)配置數(shù)據(jù)庫;

基于Linux內(nèi)核的高性能轉(zhuǎn)發(fā)模塊。

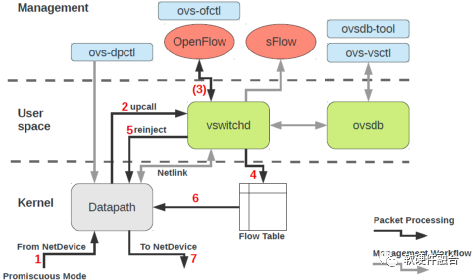

如圖,OVS答題可以分為三層:

管理層,即:ovs-dpctl、ovs-vsctl、ovs-ofctl、ovsdb-tool。

業(yè)務(wù)邏輯層,即:vswitchd、ovsdb。

數(shù)據(jù)處理層,即:datapath。

3.2.2 數(shù)據(jù)面可編程的網(wǎng)絡(luò)交換機DSA

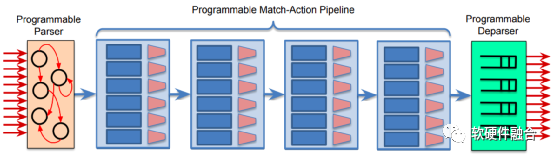

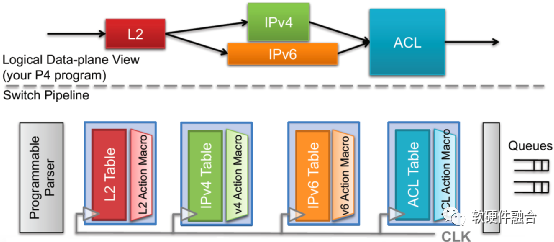

上圖為PISA(Protocol Independent Switch Architecture,協(xié)議無關(guān)的交換架構(gòu))架構(gòu)交換機的流水線,PISA是一種支持P4數(shù)據(jù)面可編程包處理的流水線引擎架構(gòu),通過可編程的解析器、多階段的可編程的匹配動作以及可編程的逆解析器組成的流水線,來實現(xiàn)數(shù)據(jù)面的編程。這樣可以通過編寫P4程序,下載到處理器流水線,可以非常方便的支持新協(xié)議的處理。

當實現(xiàn)了完全可編程的流水線之后,在P4工具鏈的支持下,就可以通過P4編程的方式來實現(xiàn)自定義的流水線,來達到對自定義協(xié)議的支持。

如圖所示,P4定義的Parser程序會被映射到可編程的解析器,數(shù)據(jù)、包頭定義、表以及控制流會被映射到多個匹配動作階段。圖 6.25中把L2處理、IPv4處理、IPv6處理以及訪問控制處理分別映射到不同的匹配動作處理單元進行串行或并行的處理,來實現(xiàn)完整的支持各種協(xié)議的網(wǎng)絡(luò)包處理。

3.3 軟件定義接口:Virtio

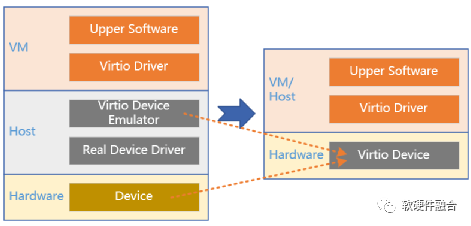

Virtio旨在提供一套高效的、良好維護的通用的Linux驅(qū)動,實現(xiàn)虛擬機應(yīng)用和不同Hypervisor實現(xiàn)的模擬設(shè)備之間標準化的接口。Virtio作為類虛擬化的I/O設(shè)備接口,廣泛應(yīng)用于云計算虛擬化場景,某種程度上,Virtio已經(jīng)成為事實上的I/O設(shè)備的接口標準。

因為軟件定義了標準化的Virtio接口,因此,如上圖所示,在SmartNIC和DPU中,offload虛擬化和Workload的最關(guān)鍵部分就是要把Virtio硬件化。

如上圖所示,站在虛擬化角度,把Virtio卸載,可以看做是從軟件到硬件。但是,如果從硬件接口的角度,從一個完全硬件定義的接口(例如NV自定義的SR-IOV接口)過渡到軟件定義的接口(Virtio接口),則可以算是從硬件到軟件。

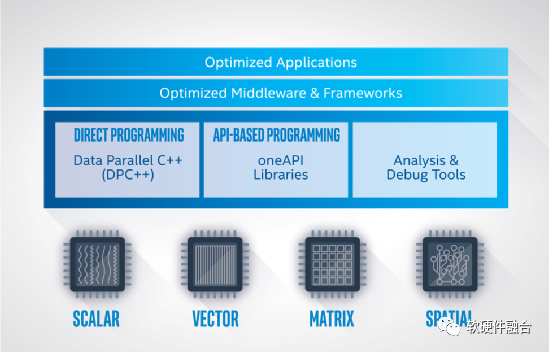

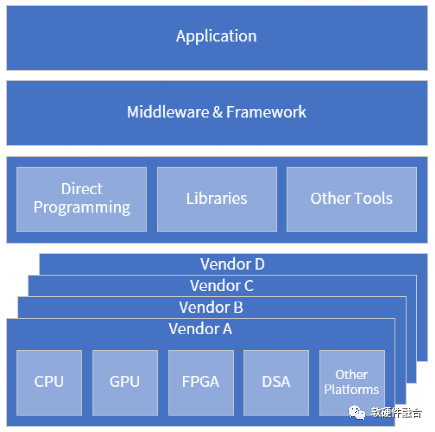

3.4 可跨平臺的軟件定義:Intel oneAPI

英特爾oneAPI是一個開放、可訪問且基于標準的編程系統(tǒng),支持開發(fā)人員跨多種硬件架構(gòu)參與和創(chuàng)新,包括 CPU、GPU、FPGA、AI 加速器等。這些處理引擎具有非常不同的屬性,因此用于各種不同的處理——oneAPI試圖通過將它們統(tǒng)一在同一個模型下來簡化這些操作。

即使在今天,開發(fā)人員面臨的一個持續(xù)問題是我們?nèi)找鏀?shù)字化的世界提供的編程環(huán)境的數(shù)量。不同的編程環(huán)境使代碼重用等節(jié)省時間的策略失效,并成為軟件開發(fā)人員的真正障礙。作為其軟件優(yōu)先戰(zhàn)略的一部分,英特爾在 2019 年的超級計算活動中推出了oneAPI。該模型標志著英特爾的雄心是擁有統(tǒng)一的編程框架作為限制專有編程平臺的解決方案。oneAPI 使開發(fā)人員能夠在不厭倦使用不同語言、工具、庫和不同硬件的情況下工作。

Intel oneAPI可以實現(xiàn):設(shè)計一套應(yīng)用,根據(jù)需要,非常方便的把程序映射到CPU、GPU、FPGA或者AI-DSA/其他DSA等不同的處理器平臺。

3.5 擴展:軟件定義“一切”

軟件定義是一個非常宏大并且非常熱點的話題,除了軟件定義網(wǎng)絡(luò)之外,還有很多軟件定義的熱點領(lǐng)域:

軟件定義存儲,是一種能將存儲軟件與硬件分隔開的存儲架構(gòu)。不同于傳統(tǒng)的網(wǎng)絡(luò)附加存儲(NAS)或存儲區(qū)域網(wǎng)絡(luò)(SAN)系統(tǒng),SDS一般都在行業(yè)標準系統(tǒng)上執(zhí)行,從而消除了軟件對于專有硬件的依賴性。

軟件定義數(shù)據(jù)中心,把數(shù)據(jù)中心基礎(chǔ)設(shè)施通過抽象化、資源池化以及自動化來實現(xiàn)基礎(chǔ)設(shè)施即服務(wù)(IAAS)。軟件定義的基礎(chǔ)設(shè)施可讓IT管理員使用軟件定義的模板和API輕松配置和管理物理基礎(chǔ)設(shè)施,以定義基礎(chǔ)設(shè)施配置和生命周期運維,并實現(xiàn)自動化。

軟件定義無線電,是一種無線電廣播通信技術(shù),它基于軟件定義的無線通信協(xié)議而非通過硬連線實現(xiàn)。頻帶、空中接口協(xié)議和功能可通過軟件下載和更新來升級,而不用完全更換硬件。

軟件定義汽車,通過軟件實現(xiàn)新的車載體驗和功能,并通過無線 (OTA) 提供更新和服務(wù)。從而使得汽車從高度機電一體化的機械終端,逐步轉(zhuǎn)變?yōu)橐粋€智能化、可拓展、可持續(xù)迭代升級的移動電子終端。

軟件定義存儲和軟件定義無線電還主要是技術(shù)的范疇,而軟件定義數(shù)據(jù)中心和軟件定義汽車,則是把軟件定義的思路和理念更加深化和拓展,應(yīng)用于更廣闊的領(lǐng)域。

4 軟硬件相互定義

4.1 軟件定義也存在一些挑戰(zhàn)

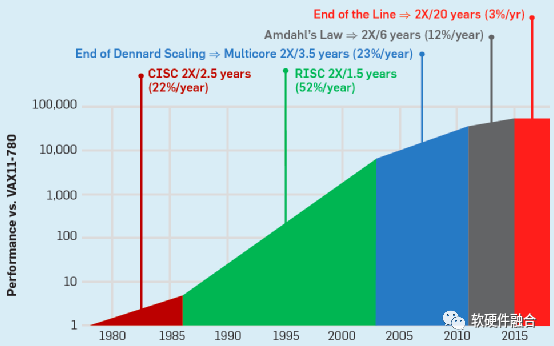

4.1.1基于CPU的摩爾定律失效

軟件定義XX,最本質(zhì)的做法還是把整個系統(tǒng)重新從硬件實現(xiàn)變成偏軟件的實現(xiàn)。隨著這勢必對CPU的性能提出了更高的要求。

然而,如上圖所示,隨著CPU的性能提升逐漸停滯,已經(jīng)無法滿足數(shù)字經(jīng)濟時代對算力持續(xù)提升的要求。

因此,還是要再輪回,“硬件”加速。

4.1.2 DSA只解決了部分問題

支持P4的網(wǎng)絡(luò)數(shù)據(jù)面可編程引擎,屬于DSA的范疇,專門用于網(wǎng)絡(luò)包處理的加速,性能跟ASIC相當,但其具有非常好的軟件可編程能力。

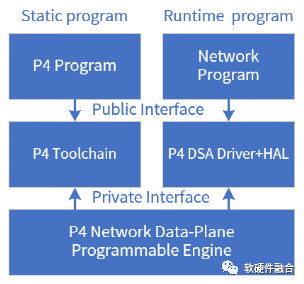

標準的P4程序,有P4前端編譯器把P4程序編譯成一個中間態(tài)的程序(類似Java編譯器)。然后特定硬件實現(xiàn)的后端編譯器負責把中間態(tài)的程序映射到具體的硬件實現(xiàn)(有點像Java虛擬機,但P4是靜態(tài))。

P4 DSA引擎預(yù)先配置好P4程序之后,P4-DSA就成了執(zhí)行特定協(xié)議處理的網(wǎng)絡(luò)包處理引擎。然后需要和已有的網(wǎng)絡(luò)程序進行適配,實現(xiàn)網(wǎng)絡(luò)任務(wù)的數(shù)據(jù)面offload。

P4的整個系統(tǒng)棧跟之前CPU、GPU、ASIC最大的不同在于先定義了標準的P4,然后各廠家根據(jù)標準的P4去實現(xiàn)各自不同的P4處理引擎。

CPU雖然現(xiàn)在有三大架構(gòu)(x86、ARM和RISC-v),但就具體的架構(gòu)而言,其定義的ISA是非常明確的。特別是在RISC-v生態(tài)下,大家遵循一致的ISA,已有的程序可以非常方便的在不同Vendor的RISC-v CPU上運行。

但是在DSA領(lǐng)域,目前還看不到這一點。

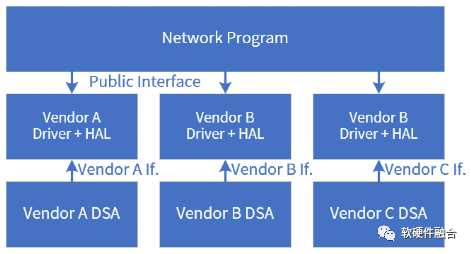

可以說,當前所有的DSA,包括P4 DSA,都還沒有實現(xiàn)接口的軟件定義,接口依然是硬件定義的,可以說是不完全的軟件定義XX。

4.2 更理想的跨平臺框架

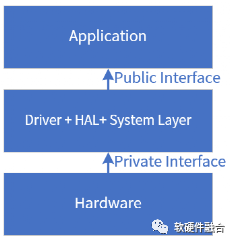

我們把oneAPI模型框架再增強一下,如上圖所示。這樣,跨平臺,不僅僅是在CPU、GPU、FPGA和DSA的跨平臺,更在于是不同Vendor的不同處理器的跨平臺。

4.3 接口的軟硬件互相定義

不管是軟件定義硬件還是硬件定義軟件,接口(這里接口是泛指,ISA是接口,IO設(shè)備的數(shù)據(jù)訪問接口也是接口,GPU等加速器呈現(xiàn)的訪問接口也是接口)都是非常關(guān)鍵的角色,因為是通過接口給對方呈現(xiàn)自己的功能和如何訪問。

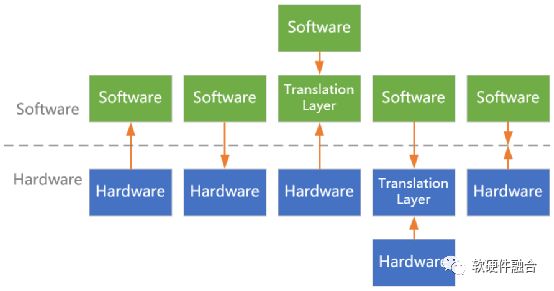

我們來總結(jié)一下軟硬件之間的接口類型:

第一類,定義好硬件,軟件依賴于硬件而定義。通常都是這樣,CPU、GPU、ASIC等等,都是這種接口定義。

第二類,軟件定義的情況下,現(xiàn)有軟件,硬件設(shè)計要進行適配。比如,Virtio的硬化,比如要兼容OVS的TC-Flower/RTE-flow接口等。

第三類,軟件定義和硬件定義各自的接口,然后中間通過轉(zhuǎn)換層適配。比如,通過HAL層把硬件驅(qū)動適配到OS;例如高級語言程序通過編譯器生產(chǎn)特定處理器架構(gòu)的Binary程序。

第四類,軟件定義,并且跨越軟硬件的接口也是軟件定義的,但是在硬件里有一層轉(zhuǎn)換層。比如,前面提到的Virtio接口,在很多解決方案里的具體實現(xiàn)是在硬件側(cè)的嵌入式軟件里,這樣,軟件模擬的Virtio成為性能的瓶頸。

第五類,軟件定義,并且跨越軟硬件的接口也是軟件定義的,硬件直接實現(xiàn)的軟件定義接口。原生支持軟件定義接口。硬件不僅僅要實現(xiàn)自己的編程范式,還需要把編程范式映射到標準接口的能力。

4.4 總結(jié)

“硬件定義軟件”是傳統(tǒng)的思路。新的技術(shù)發(fā)展很快,已有的技術(shù)仍在快速迭代;而硬件系統(tǒng)越來越復(fù)雜,更新迭代也越來越慢。系統(tǒng)如果是硬件為主,軟件依賴于硬件。則勢必限制技術(shù)的快速發(fā)展。

“軟件定義硬件”代表了一種趨勢:要從系統(tǒng)層次,主動的來定義個體的硬件。但“軟件定義硬件”的描述更多的強調(diào)系統(tǒng),容易忽略個體的特點。站在系統(tǒng)層面,可以“站得高,看得遠”,代表了宏觀的、整體的思考,能夠更好的資源統(tǒng)籌,更好的定義系統(tǒng)功能。而站在個體的層面,個體是本源,代表了事物本質(zhì)的特征。事物受客觀規(guī)律的約束,具有特定的發(fā)展規(guī)律。并且,個體具有差異化,如何更好的體現(xiàn)這些差異化優(yōu)勢,是系統(tǒng)持續(xù)不斷創(chuàng)新的本源驅(qū)動。

“軟件和硬件相互定義”,可以更好的協(xié)同系統(tǒng)和個體的關(guān)系,既能夠?qū)崿F(xiàn)軟件定義的宏觀統(tǒng)籌,又能夠兼顧硬件個體的特點和優(yōu)勢,把兩者有機的結(jié)合起來,實現(xiàn)軟硬件更加協(xié)同的更優(yōu)的系統(tǒng)。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1626文章

21666瀏覽量

601836 -

協(xié)處理器

+關(guān)注

關(guān)注

0文章

75瀏覽量

18155 -

SIMD

+關(guān)注

關(guān)注

0文章

33瀏覽量

10274 -

解耦控制

+關(guān)注

關(guān)注

0文章

29瀏覽量

10196 -

RISC-V

+關(guān)注

關(guān)注

44文章

2229瀏覽量

46026

原文標題:硬件定義軟件?還是,軟件定義硬件?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

基于Zedboard的開源軟件定義無線電設(shè)備——Panoradio

企業(yè)云下的軟件定義存儲

軟件定義技術(shù)如何為網(wǎng)絡(luò)服務(wù)

關(guān)于云際存儲軟件的定義方法,簡析其原理

杉巖:軟件定義存儲(SDS),存儲新時代

軟件定義存儲的實施是對的嗎

謹防軟件定義汽車中的軟件淺坑:BUG

自適應(yīng)計算加速軟件定義硬件時代到來

軟件定義車輛的技術(shù)概覽

軍事系統(tǒng)的未來是軟件定義和虛擬化的

SuperCAT:軟件定義EtherCAT運動控制器

硬件定義軟件?軟件定義硬件?

硬件定義軟件?軟件定義硬件?

評論