去年10月,第 54 屆國際微電子研討會在圣地亞哥舉行。這是由國際微電子組裝和封裝協會(International Microelectronics Assembly and Packaging Society)主辦的會議,簡稱為 iMAPS。

大會上,Cadence副總經理KT Moore先生親自到場發表了一場題為《判斷電子設計的下一步:后摩爾時代亦或超越摩爾時代(More Moore or More than Moore: an EDA Perspective)》的主題演講。由于 KT 先生的姓氏是 Moore,和摩爾定律(Moore's Law)中是同一個單詞,這場演講可以說足夠“摩爾”。

圖為Cadence副總經理KT Moore先生在iMAPS大會發表主題演講。

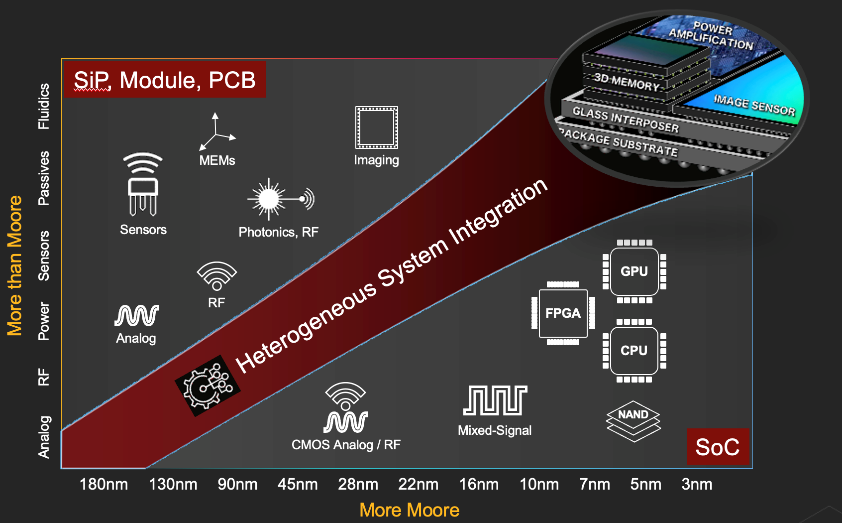

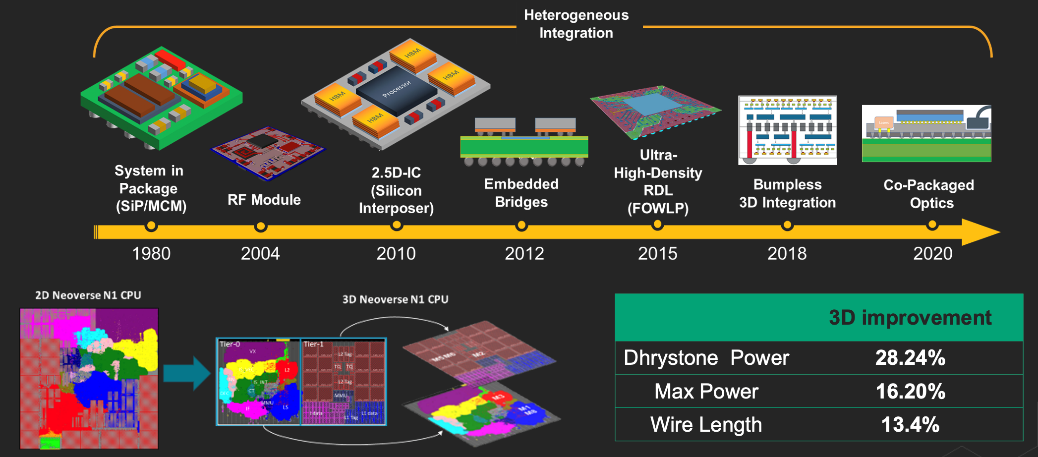

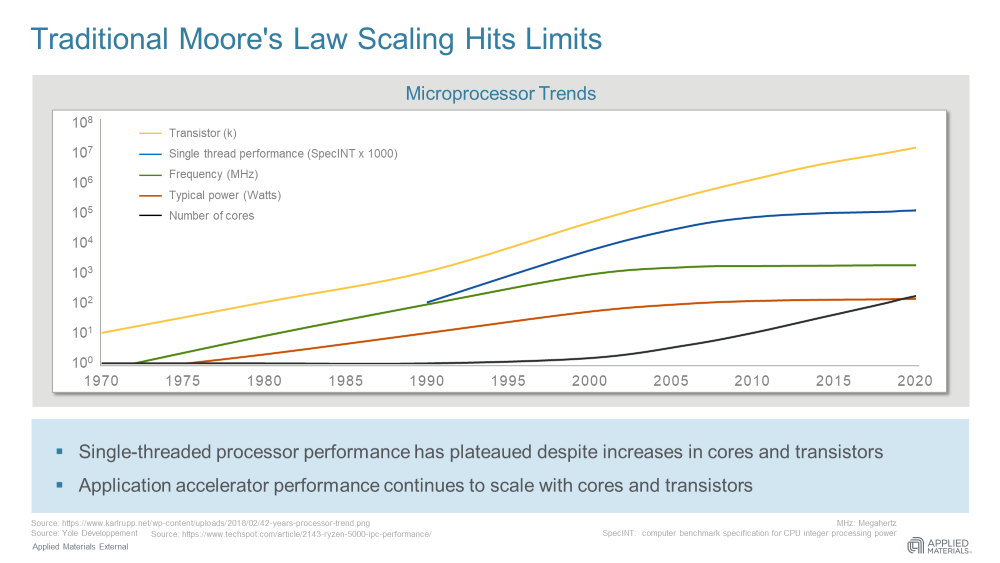

當然,“超越摩爾定律”(more than Moore) 令人朗朗上口,用來描述系統在芯片上擴展的方式,而不是單純地指擴大硅的尺寸,摩爾定律之前重要的內容就是縮小元器件并擴大硅尺寸;而“超越摩爾定律”指的就是高級封裝。

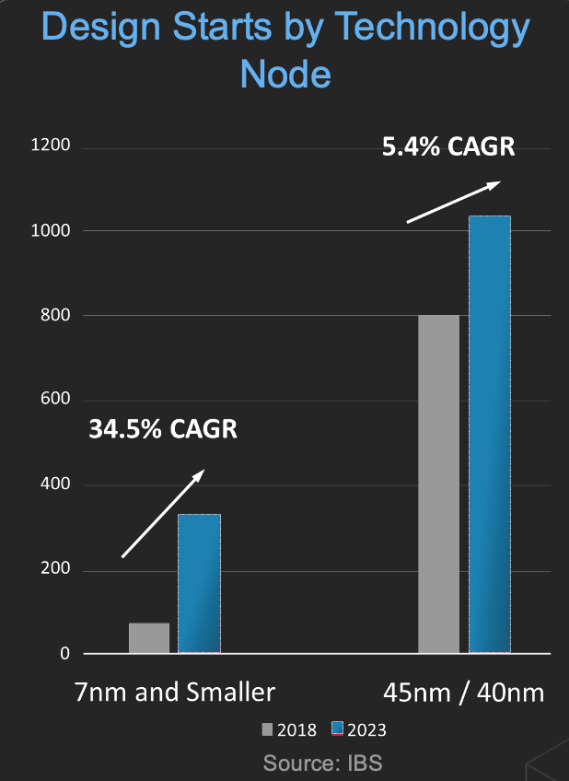

當數年前 KT 先生聽說 7nm 工藝時,他預測可能只有十家公司能夠負擔在這種節點進行設計的能力(我也懷疑數量不會很多,當時幾乎所有作出預測的人也都是這樣認為的)。但是我們都錯了;目前有幾百家公司正在進行 7nm 及更先進的設計,其中包括成熟的半導體公司、遍布全球各地的初創公司,以及開始自主設計芯片的系統公司。

正如上圖所示,先進節點的成長比例比成熟節點強勁得多(當然,先進節點的起步基礎較小)。但兩者都在增長,半導體行業呈現一片欣欣向榮的景象。

復雜的系統設計方法出現了分叉,有點像“雙城記”。圖中的右下角是傳統的 SoC,即把所有東西都塞進一個裸片中;左上方是帶有光學元件、射頻...等其他功能的系統。目前,它們開始融合到中間的線上,形成異質系統的集成:

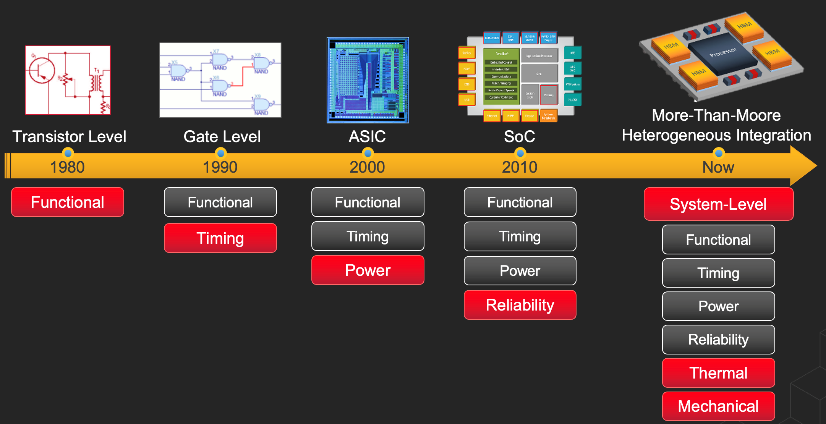

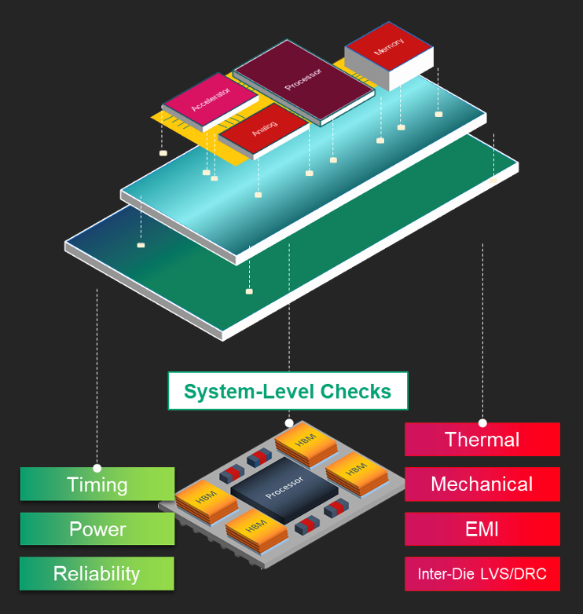

1985 年,KT 先生畢業后到Texas Instruments國防部門工作,參與了當時Texas Instruments規模最大的設計,有 9000 個晶體管。現在,有這么多器件的芯片上只要放置一個 I/O 就可以。但在當時,人們唯一關心的只是“功能是否正確”。漸漸地,我們需要檢查設計的其他方面。現在,在“超越摩爾定律”的時代,我們擔心的是如何一起完成所有復雜的系統級功能檢查。

在電子設計 (EDA, Electronic Design Automation) 中,我們不再僅止于關注 IO-ring內的情況,而是需要同時關注 IO-ring外的各種性能問題。

在系統方面,設計的許多方面一直是彼此獨立設計的。但由于缺乏集成的信息,往往導致單個裸片和封裝出現過度設計而使得成本昂貴。

3D-IC 設計整合和管理

裸片放置和管腳bump 規劃

沒有單一的數據庫來收集多種技術規范

跨越小芯片(chiplets)和封裝的熱分析

3D STA 和用于簽核的時序工藝角數量猛增

系統級裸片間連接性驗證

上下游跨域設計溝通

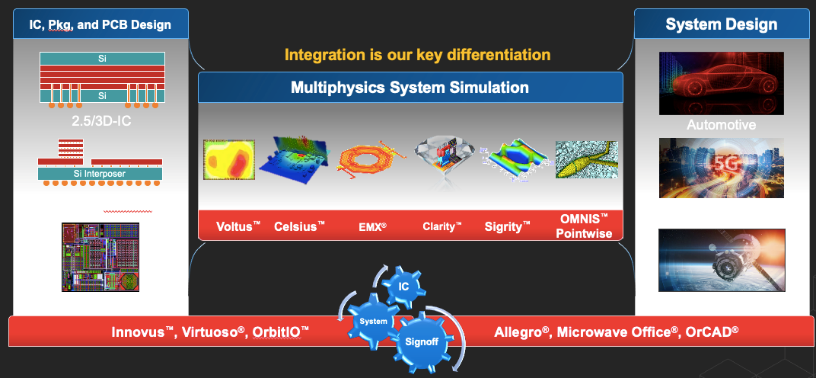

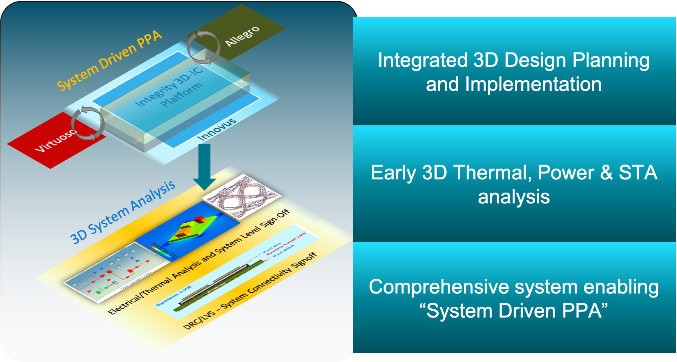

要解決現今工具缺乏集成的問題,顯然就是開發更多的集成能力。下圖顯示了 Cadence針對“航空、火車和汽車”的主要工具集成,這些領域都含有電子元件及許多其他部件。這不僅僅是關于“IO 環內”的芯片,還包括外部的從電氣和熱分析到計算流體力學的一切。

“

以前可能只分析單獨一塊電路板,現在我們可以分析整個系統,并進行合理的計算。因為Cadence工具可以高效進行架構設計,因此用戶不必擁有巨大的內存,而是可以使用在云上可用的無限計算能力——無論是在公有云還是在私有云上。

——KT Moore

”

設計工具的研發與并購

今天,我們用“超越摩爾定律”來討論異構集成;但事實上,自 90 年代初業界開始探討“多芯片模塊 (multi-chip modules ,MCM)”以來,Cadence 就一直在深耕這個領域。當然,這遠在摩爾定律開始失去動力之前。

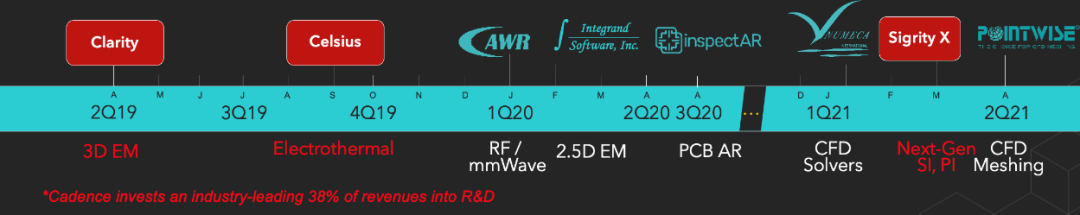

每家公司都面臨一個共同的挑戰:是在企業內部自行開發一款產品(有時稱為“有機成長“),還是收購一家專攻某個領域的公司。在過去的兩年里,Cadence 在系統領域構建了一個完整的產品組合,混合采用了這兩種方法:

Clarity 家族,用于系統級電氣分析的工具(內部開發)

Celsius家族,用于熱分析的產品 (內部開發)

AWR家族,用于射頻設計的產品 (收購)

Integrand 工具,用于 2.5D 芯片上的電磁分析(收購)

inspectAR工具,PCB 增強現實(AR)技術(收購)

Numeca技術,用于計算流體力學的求解器 (收購)

Sigrity X工具,用于下一代信號和電源完整性的產品(內部開發)

Pointwise家族,用于 CFD 網格劃分的產品(收購)

其中,有一件事令業內人士都感到驚訝,那就是 Cadence 將 38% 的收入投資到研發之中,這一比例在行業內處于領先水平。在半導體設計和集成方面,總是會不斷涌現新的要求。

設計完整性

KT 最后談到了 Integrity 3D-IC平臺,這是一款專門針對堆疊裸片 3D 芯片設計的新產品。該工具可以進行 3D 規劃(如傳統在同一個層面上,稱為布局規劃)和設計實現。并且,它可以進行早期的 3D 熱、功耗和時序分析。這些能力結合在一起,不僅在單個裸片的層面上,也在系統的層面上優化了 PPA。

“

PPA 是指功耗(Power)、性能(Performance)和面積(Area),這也是半導體領域的術語。我們談論的是在實現最佳性能的同時,使芯片尺寸盡可能小、功耗盡可能低。設計師面對的問題是“這對于高級封裝來說有什么不同?”其實沒有什么不同,但是必須采取不同的方法。

……

歸根結底,關鍵在于全面的集成。設計師需要知道,自己能夠信心十足地完成設計。當開始組合這些異構設計時,有很多地方會出現問題。因此,Integrity 3D-IC平臺融合了Cadence的布局和布線技術,以及仿真分析技術。我相信Cadence是目前唯一一家可以宣稱將這些技術相互集成的公司,所以Cadence提供了真正的集成解決方案。這就是 EDA 的發展方向,我們正在與一些客戶和合作伙伴攜手合作,共同引領這一潮流。

——KT Moore

”

最后的問題

在主題演講的最后,KT提出了最后一個問題:

我們應該讓摩爾定律繼續發展?還是追求超越摩爾定律?

答案您可能早已知曉,KT 的答案是我們需要兩者兼顧。

-

半導體

+關注

關注

334文章

27064瀏覽量

216504 -

摩爾定律

+關注

關注

4文章

632瀏覽量

78939

發布評論請先 登錄

相關推薦

飛騰成功舉辦散熱技術應用發展研討會

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

“自我實現的預言”摩爾定律,如何繼續引領創新

啟揚智能受邀參加2024恩智浦技術巡回研討會

2024 ETAP 電氣系統數字孿生平臺技術研討會(深圳站)

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

是德科技智能算力‘芯’技術研討會回顧

后摩爾定律時代,Chiplet落地進展和重點企業布局

【大大速遞】與技術專家在線交流,12月熱門研討會正在報名中

行業資訊 I iMAPS 研討會:摩爾定律,延續或超越?

行業資訊 I iMAPS 研討會:摩爾定律,延續或超越?

評論