XC7Z015-2CLG485I 供應商 XC7Z015-2CLG485I怎么訂貨 XC7Z015-2CLG485I價格

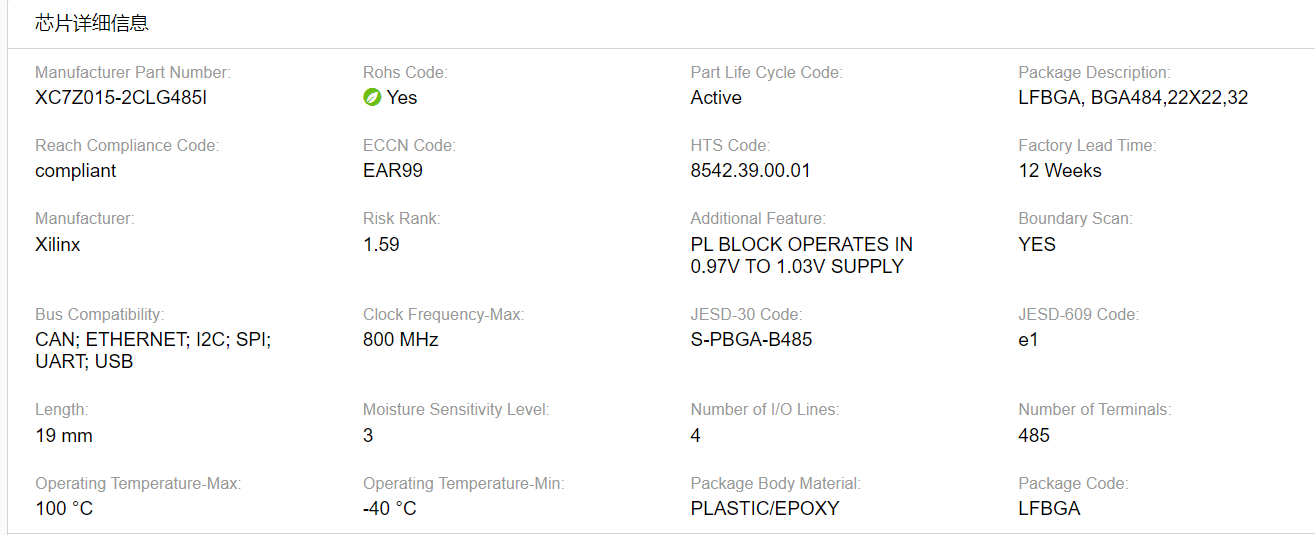

Manufacturer: Xilinx

Product Category: Processors, Microprocessors

Manufacturer Part #: XC7Z015-2CLG485I

XC7Z015-2CLG485I Zynq?-7000系列基于Xilinx全可編程SoC體系結構。這些產品在單個設備中集成了功能豐富的基于ARM?Cortex-A9的雙核處理系統(PS)和28 nm Xilinx可編程邏輯(PL)。ARM Cortex-A9 CPU是PS的核心,還包括片上內存、外部內存接口和豐富的外圍連接接口。

XC7Z015-2CLG485I 主要特征

雙核ARM?皮質?-基于A9的應用處理器單元(APU)

每個CPU 2.5 DMIPS/MHz

CPU頻率:高達1 GHz

相干多處理器支持

ARMv7-A體系結構

TrustZone?安全

Thumb?-2指令集

Jazelle?RCT執行環境體系結構

霓虹的? 媒體處理引擎

單精度和雙精度矢量浮點單元(VFPU)

CoreSight? 和程序跟蹤宏單元(PTM)

定時器和中斷

32 KB級別1 4路集合關聯指令和數據緩存(每個CPU獨立)

512 KB 8路集關聯二級緩存(在CPU之間共享)

字節奇偶校驗支持

片上啟動ROM

256 KB片上RAM(OCM)

字節奇偶校驗支持

多協議動態存儲器控制器

DDR3、DDR3L、DDR2或LPDDR2存儲器的16位或32位接口

16位模式下的ECC支持

1GB的地址空間,使用單列8、16或32位寬的存儲器

XC7Z015-2CLG485I 靜態內存接口

兩個10/100/1000三速以太網MAC外設,支持IEEE標準802.3和IEEE標準1588修訂版2.0

兩個USB 2.0 OTG外設,每個外設最多支持12個端點

兩個SD/SDIO 2.0/MMC3.31兼容控制器

兩個全雙工SPI端口和三個外圍芯片選擇

兩個高速UART(高達1 Mb/s)

兩個主和從I2C接口

具有四個32位組的GPIO,其中最多54位可與PS I/O(一組32b和一組22b)一起使用,最多64位(最多兩組32b)可連接到可編程邏輯

多達54個靈活多路復用I/O(MIO),用于外圍引腳分配

真雙端口

高達72位寬

可配置為雙18KB

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601849 -

單片機

+關注

關注

6032文章

44516瀏覽量

633030 -

電子元器件

+關注

關注

133文章

3307瀏覽量

104939

發布評論請先 登錄

相關推薦

正點原子ZYNQ7015開發板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強悍,資料豐富!

請問SPI一包數據最多可以傳多少個字節?

FPGA核心板 Xilinx Artix-7系列XC7A100T開發平臺,米爾FPGA工業開發板

CC2640R2L使用BLE的Notify功能,通過定時器每隔10ms向手機發送一包數據,會出現丟包的原因?

關于XC7Z020的尾綴,CLG400的價格為何會比CLG484 要貴上將近50塊??

核芯互聯發布支持PCIe Gen 6的時鐘發生器芯片CLG0841/CLG0851

XC7Z015-2CLG485I 168個一包

XC7Z015-2CLG485I 168個一包

評論